工程文件

module aa(

input rst_n,

input clk,

output clko);

reg [1:0] cnt;

reg clk1,clk2;

always@(posedge clk or negedge rst_n)

if(!rst_n)

cnt = 2'b0;

else if(cnt == 2'b10)

cnt = 2'b0;

else cnt = cnt + 1;

always@(posedge clk or negedge rst_n)

if(!rst_n)

clk1 = 0;

else if(cnt == 0)

clk1 = 1;

else if(cnt == 2'd2)

clk1 = 0;

always@(negedge clk or negedge rst_n)

if(!rst_n)

clk2 = 0;

else if(cnt == 0)

clk2 = 1;

else if(cnt == 2'd2)

clk2 = 0;

assign clko = clk1 && clk2;

endmodule

测试文件

`timescale 1ns/1ns

module tb();

reg rst_n,clk;

wire clko;

aa aa(

rst_n,

clk,

clko);

initial clk = 0;

always #10 clk = ~clk;

initial begin

rst_n = 0;

#30 rst_n = 1;

#1000 $stop;

end

endmodule

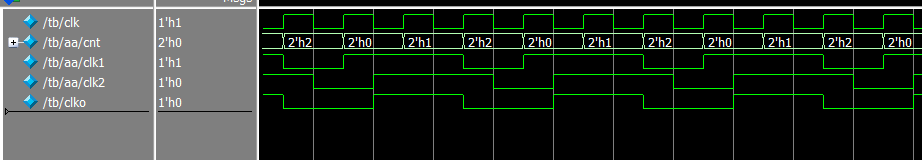

实现原理

分别在原clk上升沿和下降沿实现占空比非50%的奇数分频时钟,然后将两时钟进行与(或)操作。

上述将两时钟进行与还是或,主要看你得到的占空比非50%的奇数分频时钟中高电平比例超过50%还是低电平比例超过50%。

以上述代码为例,三分频电路。那么计数器计数计3个即可,0,1,2。所以计数器两位就够了。每次计到2,使其归零。然后占空比非50%分频,计数器为0时,使其为高电平;计数器为2时,使其为低电平。这样高电平持续时间就比低电平多,那么得到的两时钟最终就是进行与操作。

这里计数器为0时,使其为高电平;计数器为2时,使其为低电平。其实也可以计数到1,使其为低电平,这样低电平持续时间就比高电平多。那么最后相或。

总结规律的话就是,n分频,计数到n/2左右的两个整数都可以最后用相与、相或调整。

983

983

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?