如下verilog描述中哪个或者哪几个会生成寄存器?

A always@(clk)

reg_a <= reg_b;

B always@(negedge clk)

reg_a<= reg_b;

C always@(posedgeclk)

reg_a<= reg_b;

D assign reg_a =reg_b;

解析:A选项中虽然也有clk,但是不是沿触发的,而是用always实现的组合逻辑。B、C毫无疑问,无论是上升沿触发还是下降沿触发都会产生寄存器,所以我们可以得出结论能不能生成寄存器的关键条件是always敏感列表中的触发条件。而D选项也没有什么疑问了,用assign实现的组合逻辑赋值。所以答案选择B、C。

触发器的触发要同时用到高电平和低电平,也就是说一次触发占据一个周期,不可能同时上升沿和下降沿触发,它们间隔不到一个周期,没有电路相对应。

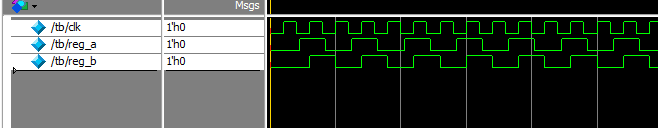

always@(clk)

reg_b <= reg_a;

当clk初值设置为1时,它会在每个clk下降沿将reg_a的值传递给reg_b。

当clk初值设置为0时,它会在每个clk上升沿将reg_a的值传递给reg_b。

通过对比上述两图,我们可以猜测,每一次赋值都是需要一个敏感信号的一周期时间的。所以,不能always@(posedge clk or negedge clk)。

而always@(clk)等价于always@(posedge clk)或者always@(negedge clk);这个在仿真中体现在clk的初值上;而在实际硬件中,具体怎样体现不知道。

6468

6468

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?