- ATPG automatic test pattern generation

1. physical defects

-

short and open

-

drc escape

具有多样性等特点

不好测试,所以学术界提出了fault model 概念,具体作用有 test generation fault simulation

quality prediction fault diagnosis

除了测试还能具体分析芯片的covereage

fault model 定义:描述错误的行为

2. fault model 种类

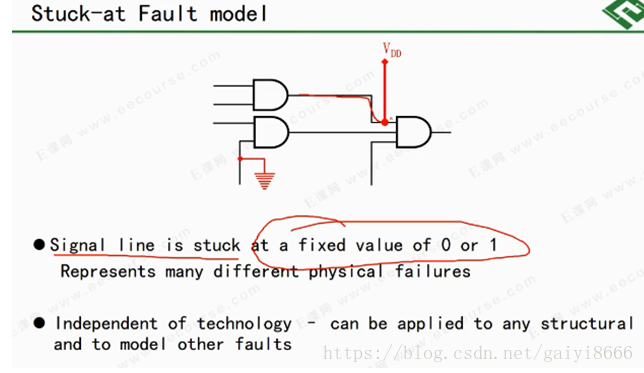

stcuk at fault model 注意和工艺无关

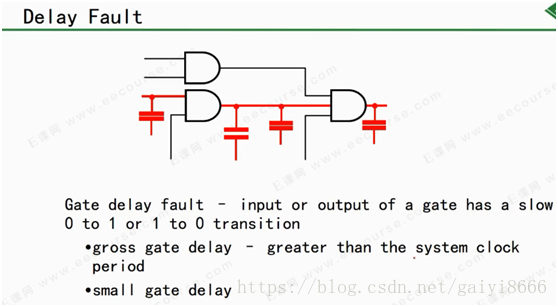

第2种 为 dealy fault model

行为表征:比如100M 能工作,600M不能工作

delay fault model又分为两种 transition delay fault model

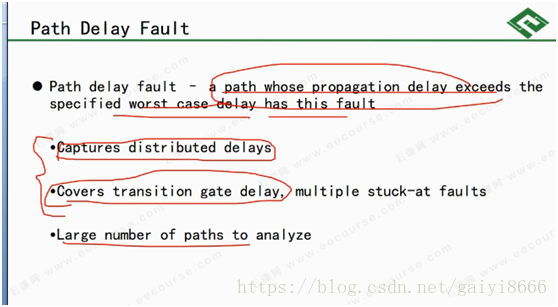

path delay fault model

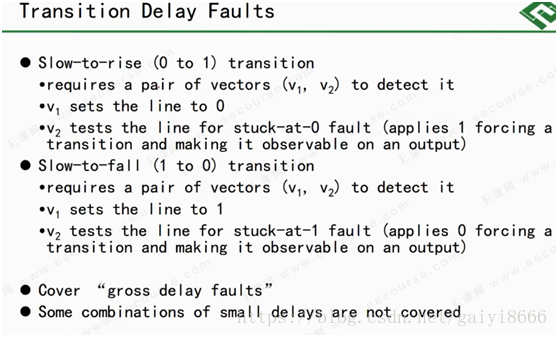

transition delay faults :slow to rise slow to fall

path delay fault :其实可以把 transition delay 看成一种特殊 path delay

描述这个 fault 就是整个路径的延迟大于时钟周期

实际上这种 fault model 更接近实际的情况,但是却不用这种model为什么呢,因为path 上路径太多,一个好的model除了反应具体的defect特性,还要好求解,显然path delay fault model 没有第2种特性

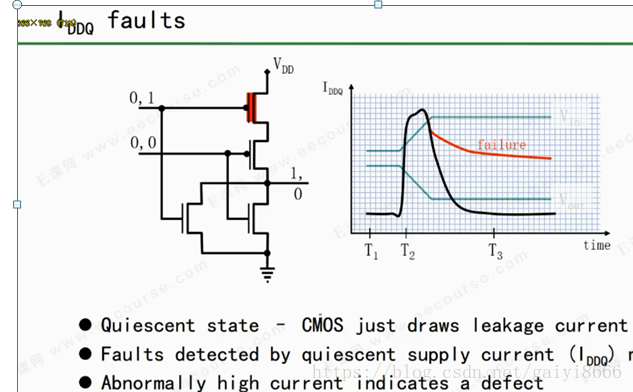

IDDQ fault moel 用的很少

就是在晶体管不工作的时候,漏电流过大,但是现在尺寸已经很小,漏电流本身就比较大,这个阈值不好设置。

因此现在大部分用的 fault model 都是stuck at 和 transition delay fault model ,对这两种 model 进行求解 生成结构性测试向量

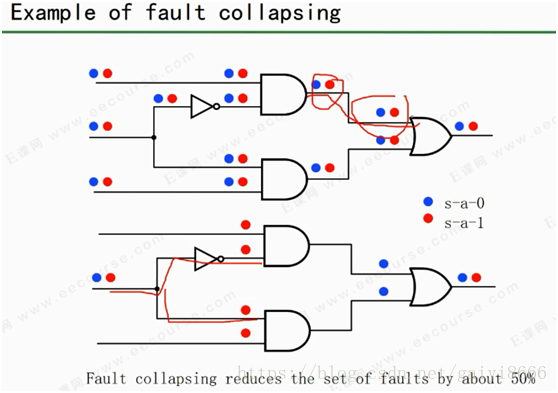

3. collapsing faults list

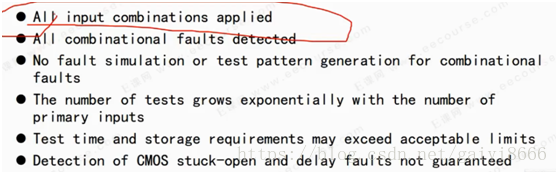

我们当然希望做到完备的测试 exhaustive testing ,但是实际上却不可能,太浪费时间

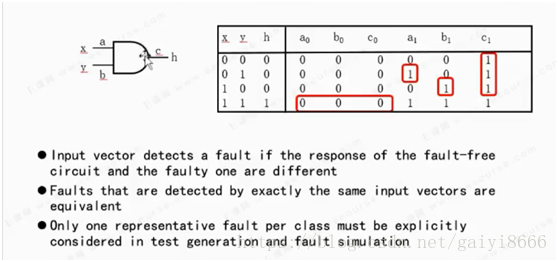

对于一个与门,有一个输入 stuck at 0 与输出 stuck at 0 等价,

-

(1)fault free 正常输出 如果 vector detect 到 fault,那么将会与 fault free ciruit 电路不一样

-

(2)能够被同一个vector detect 到fault 认为是等价的

-

(3)对于等价的 fault 分为一类,一类产生一条结构性测试向量即可

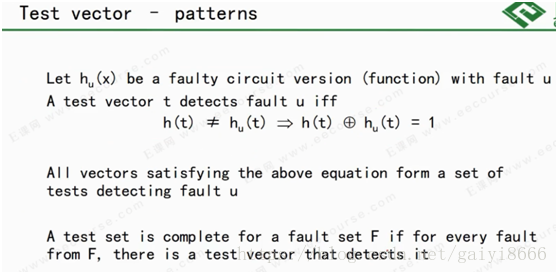

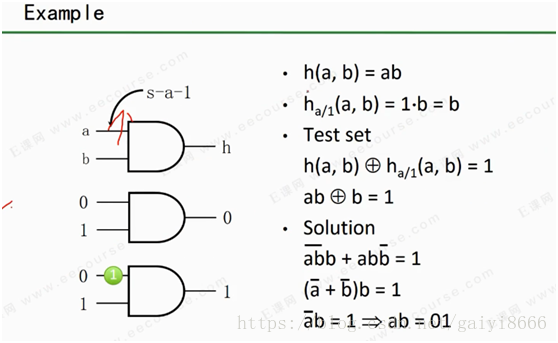

假设fault free 的 circuit 用 h(x)表示

faulty circuit 用 hu(x)

可以很明显得出 : 两个异或得到1

例子:a stuclk at 1 进行求解 ab=01

例子:fault collasping 之后的 测试向量明显减少

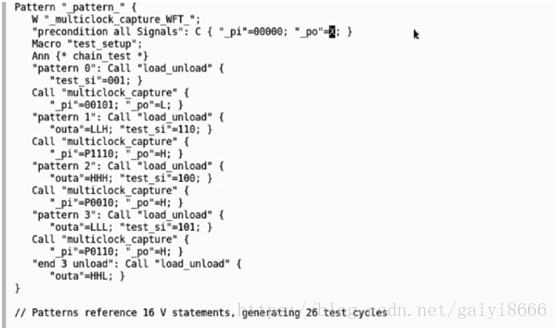

4. atpg tcl 和结果

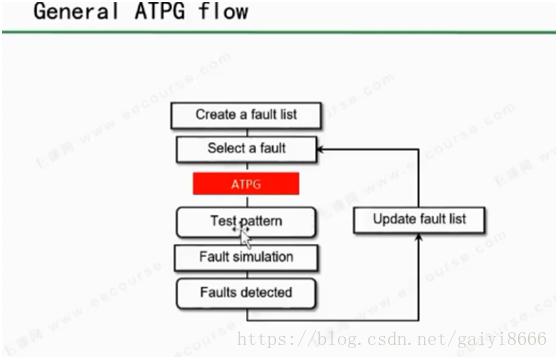

5. atpg flow

产生结构性测试向量都是根据 fault model 来的

选择fault model ,基于D 算法进行求解

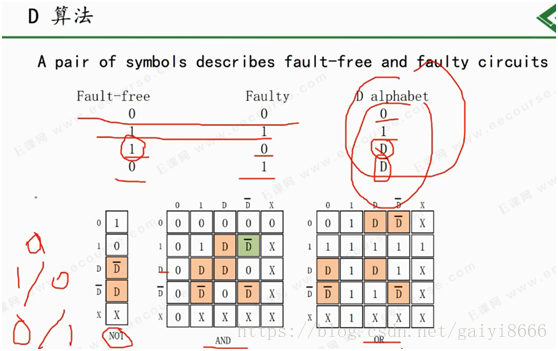

6.什么是D 算法

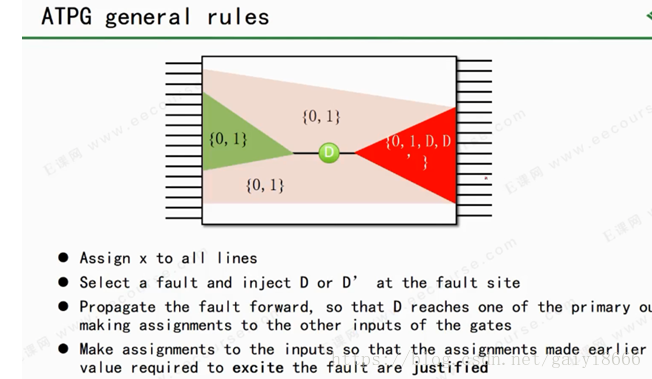

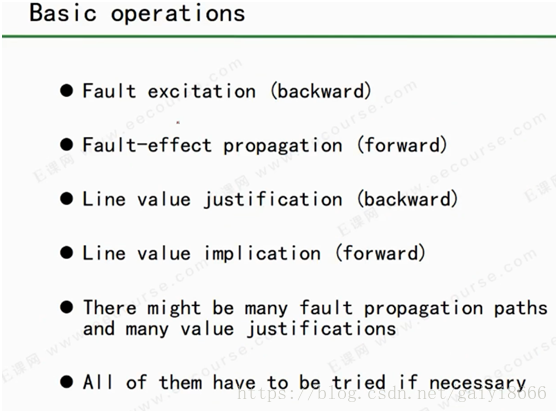

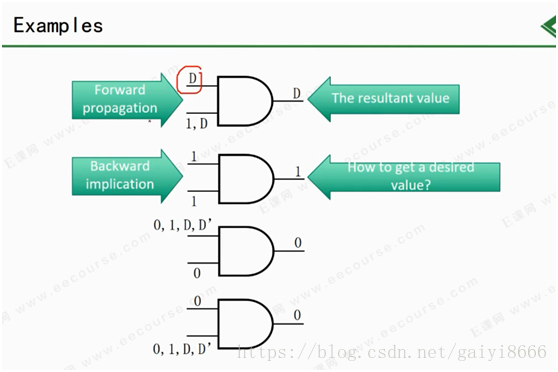

ATPG general rules

一些专业术语

例子: 第一个与门如果要把D forward 那么另一个port 一定要为1 或者d

第2个与门输出的1 如果要向 backward 那么输入必须都为1

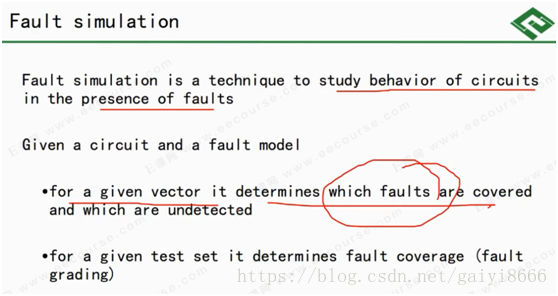

7. fault simlution

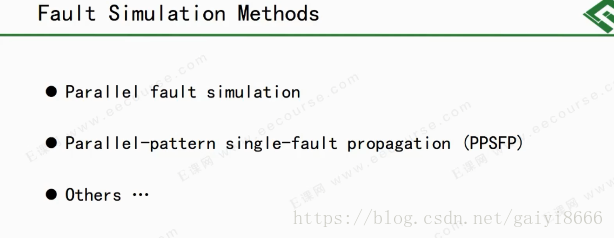

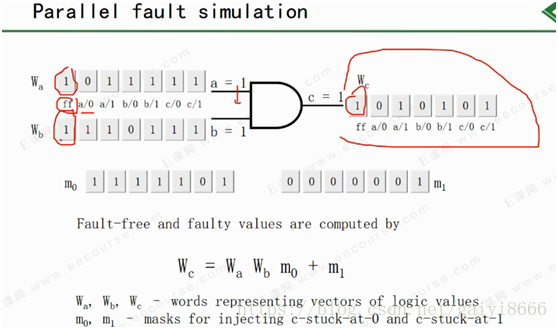

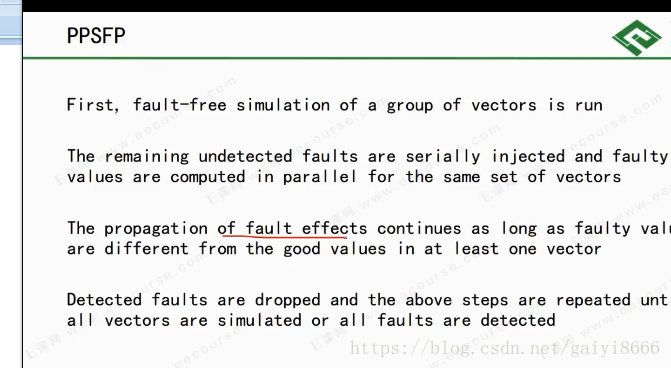

两种 parallel fault simulation

parallet pattern single fault propagation

参考资料

原文链接:https://blog.csdn.net/gaiyi8666/article/details/80867362

本文详细介绍了DFT中的Automatic Test Pattern Generation (ATPG)技术,包括物理缺陷、故障模型、故障等价类压缩、D算法及其应用。重点讨论了Delay Fault Model,解释了Transition Delay Fault和Path Delay Fault的区别,并分析了为何在实践中更多使用Stuck-at和Transition Delay Fault Model。同时,文章还涵盖了ATPG的基本流程和Fault Simulation的重要性。

本文详细介绍了DFT中的Automatic Test Pattern Generation (ATPG)技术,包括物理缺陷、故障模型、故障等价类压缩、D算法及其应用。重点讨论了Delay Fault Model,解释了Transition Delay Fault和Path Delay Fault的区别,并分析了为何在实践中更多使用Stuck-at和Transition Delay Fault Model。同时,文章还涵盖了ATPG的基本流程和Fault Simulation的重要性。

5323

5323

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?