相关阅读

静态时序分析![]() https://blog.csdn.net/weixin_45791458/category_12567571.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12567571.html?spm=1001.2014.3001.5482

理想时钟(ideal_clock)、传播时钟(propagated_clock)是两种相对的时钟,理想时钟用于时钟树综合(CTS)前,而传播时钟用于时钟树综合后。生成时钟(generated_clock)用于定义一个由另一个时钟(被称为主时钟(master_clock))派生出的时钟,例如一个分频时钟,这么做的目的是因为DC无法自动由触发器时钟端的时钟推断出其输出端的分频时钟,本文旨在理清这三者之间关系。

理想时钟

create_clock命令创建的时钟是就是理想时钟,关于该命令的使用,可以参考之前的文章SDC命令详解:使用create_clock命令进行约束。

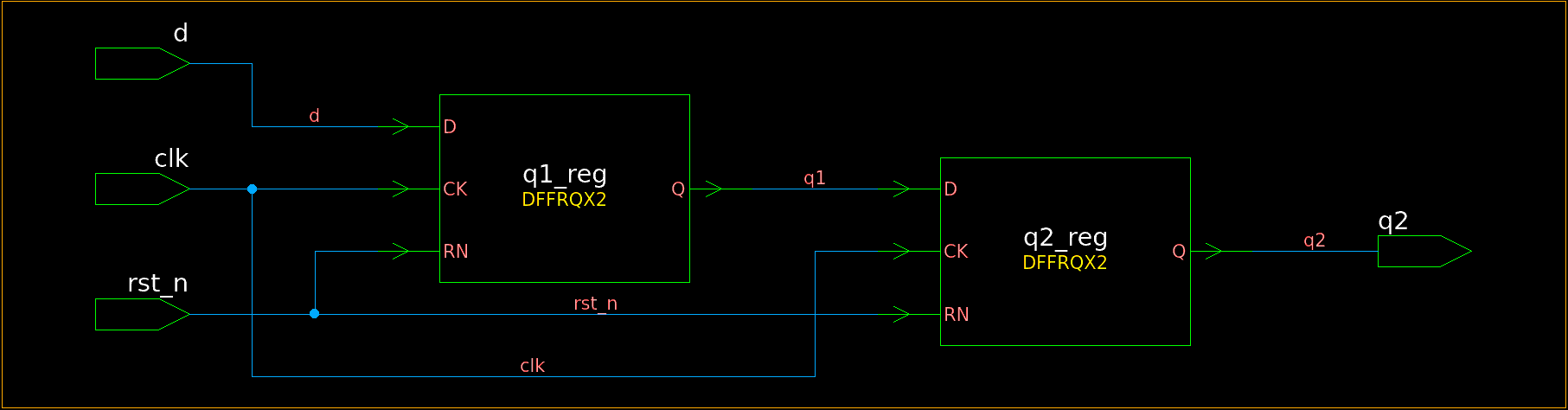

下面用一个简单的例子说明这一点,图1是两个D触发器的简单级联。

图1 一个简单的例子

下面使用create_clock命令,在clk端口创建了一个理想时钟,周期为10。

create_clock -period 10 [get_ports clk]对于理想时钟而言,它的延迟包括两部分:源延迟(source)和网络延迟(network delay),它们都是使用set_clock_latency命令进行设置的,关于该命令的使用,可以参考之前的文章SDC命令详解:使用set_clock_latency命令进行约束。注意:理想时钟的网络延迟值是直接设置的,而不会从时钟路径上的线延迟(net delay)和单元延迟(cell delay)中推断出来。

下面的命令设置了时钟clk的源延迟为2ns,网络延迟为0.5ns。

set_clock_latency -source 2 [get_clocks clk]

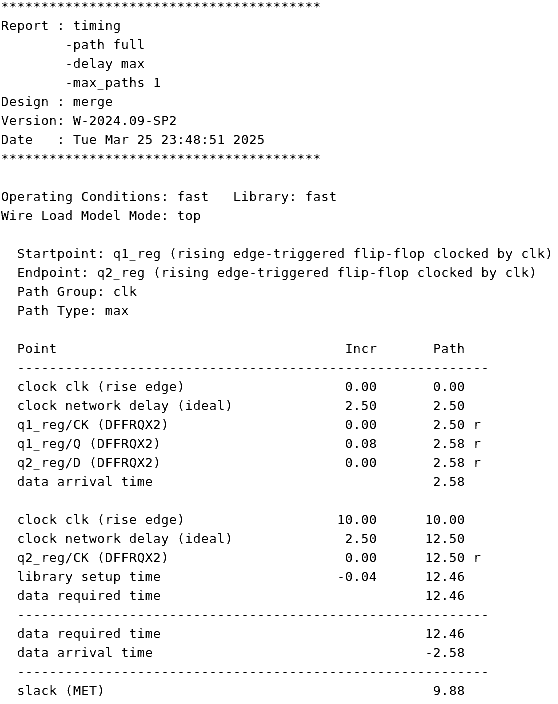

set_clock_latency 0.5 [get_clocks clk]图2所示的建立时间时序报告显示,时钟的总延迟为2.5ns(注意这里的network delay其实指的是总延迟,而不只是网络延迟),括号中的ideal提示了这是一个理想时钟。

图2 建立时间时序报告

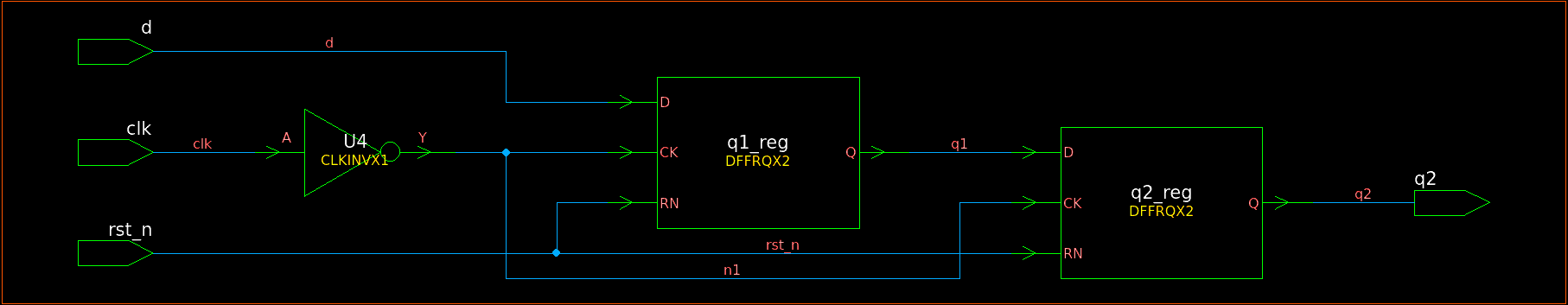

那么,是不是说时钟路径上的任何单元都无法影响理想时钟呢?其实不然,它可以影响理想时钟的时钟极性,即如果存在一个反相器,则时钟上下沿会反相,如图3所示的电路图。

图3 时钟路径上有反向器的例子

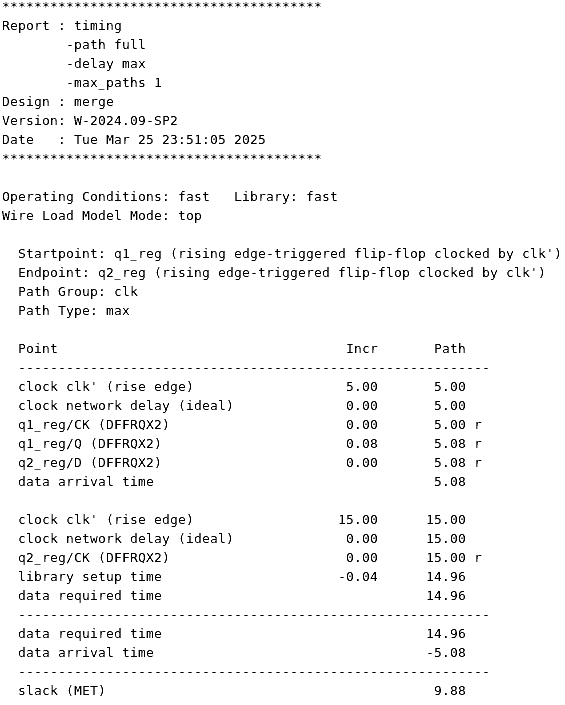

图4为此时的建立时间时序报告,注意其中上升沿的时间已经不是0ns和10ns,而是5ns和15ns。

图4 建立时间时序报告

顺带一提,理想时钟的转换时间,是由set_clock_transition命令直接指定的,关于该命令的使用,可以参考之前的文章SDC命令详解:使用set_clock_transition命令进行约束。

传播时钟

传播时钟是在进行了时钟树综合后,使用set_propagated_clock命令将一个理想时钟转换为传播时钟(注意,虚拟时钟即无时钟源对象的时钟无法被转换为传播时钟),此时的时钟延迟由源延迟和真实网络延迟组成,这里的网络延迟是根据时钟路径上的线延迟和单元延迟真实计算出来的。

例如对于图3所示的例子,使用set_propagated_clock命令将理想时钟clk转换成传播时钟,此时会给出如下警告,因为这个理想时钟之前设置了网络延迟值,将其转换成传播时钟会导致网络延迟值被删除(对于转换时间也是如此)。

set_propagated_clock [get_clocks clk]

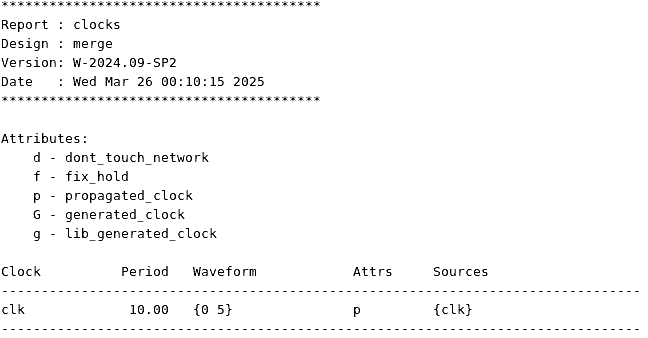

Warning: Converting ideal clock at 'clk' to propagated clock. (UID-477)图5是此时的时钟报告,可以看出此时的时钟clk已经拥有p属性了,即是一个传播时钟了。

图5 时钟报告

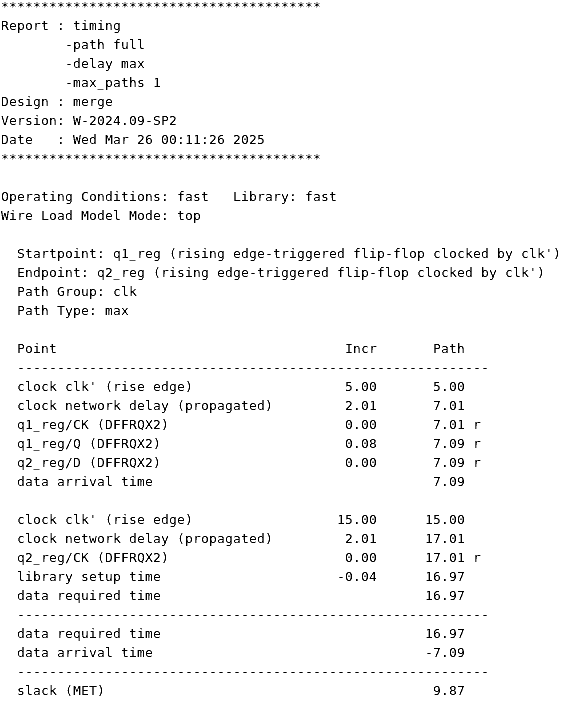

图6是此时的建立时间时序报告,时钟的总延迟为2.01ns(注意这里的network delay其实指的是总延迟,而不只是网络延迟),其中的0.01ns就是时钟路径上的线延迟和单元延迟之和,括号中的propagated提示了这是一个传播时钟。

图6 建立时间时序报告

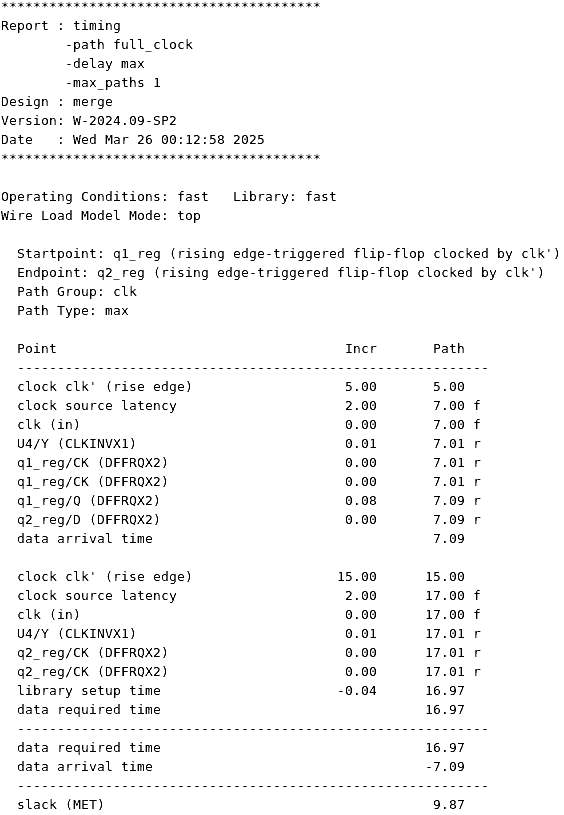

可以选择添加-path full_clock选项,这样的时序报告会展开一个传播时钟的时钟路径,而不是只显示为一个总的延迟值,如图7所示。

图7 展开时序路径的建立时间报告

注意:在这个例子中,线延迟为0,因为使用了理想线负载模型,所以只显示了单元延迟0.01ns。

以上内容,对理想时钟和传播时钟的延迟计算进行了讨论,关于它们两者和生成时钟的关系,留到下一章进行讨论。

下一章

2387

2387

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?