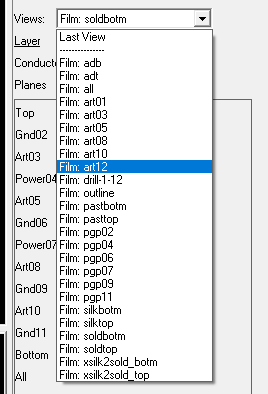

1.art和pgp 信号层和电源层

在Allegro软件中,ART(Artwork)和PGP(Plane)层都是PCB的一个层。其中,ART层是指ARTWORK层,它通常用于在电路板的制造过程中为电路板的铜层、印刷层、丝网印刷层等图层定义图形元素、标识和文字等。ARTWORK层通常由高对比度的线条或图案组成,而不是电路板的电气连接。而PGP层则是指平面层(Plane),它用于定义电路板的电气连接、接地层和电源层。在12层板中,pgp02 或者 pgp04 层通常用于电源或地平面层,ART01,ART03则可以用于铜层或印刷层等用途。

2.adb和adt

Film:adt顶层视图

Film:adb底层视图

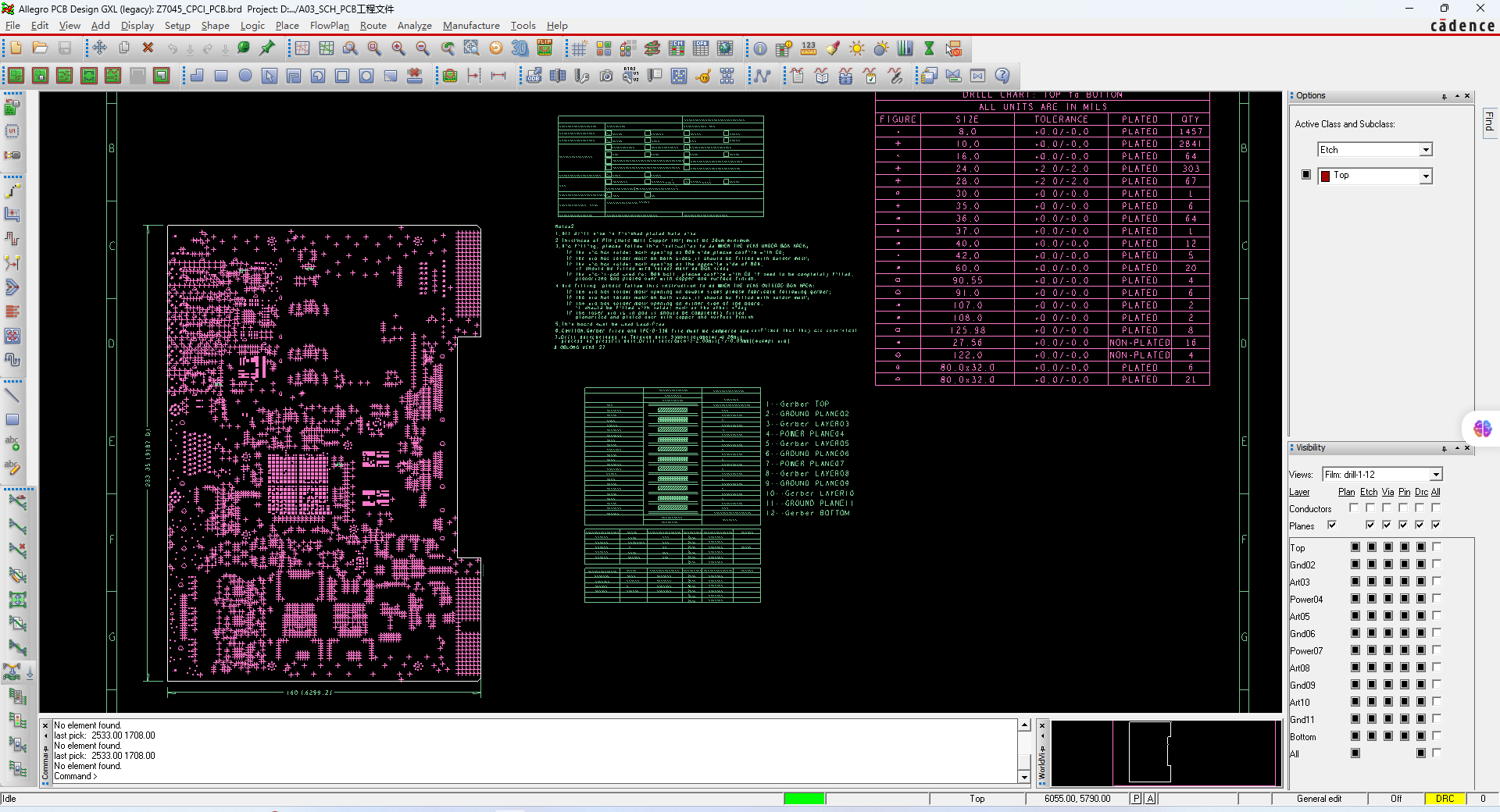

Film:drill钻孔视图(钻孔表和层叠说明)

Film:outline板框

Film:silktop顶层丝印视图(丝印和元器件位号)

Film:silkbot底层丝印视图

3.drill钻孔

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?