Q:我们再来设计实现由4个D触发器构成的4位移位寄存器。

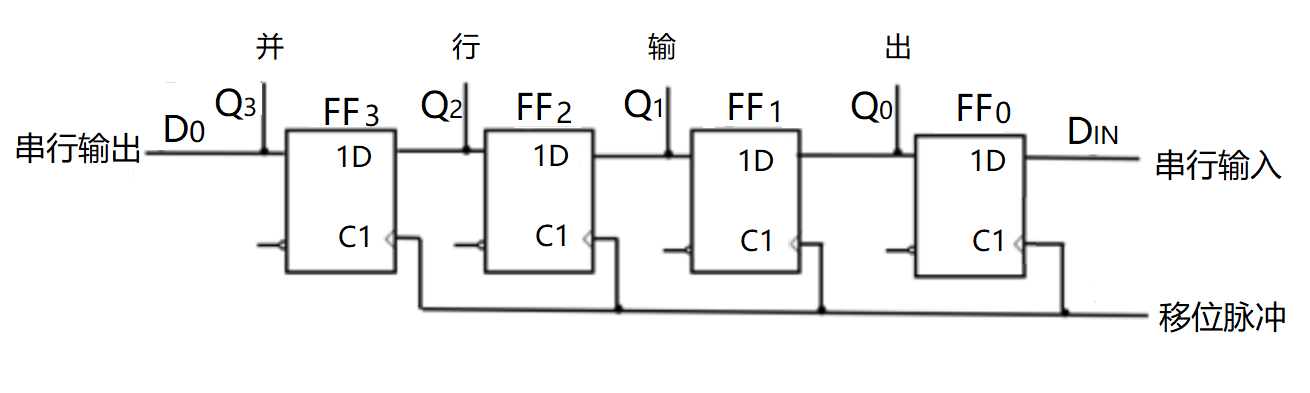

A:将4个D触发器串接级联构成的具有移位功能的寄存器称为移位寄存器(Shift Register)。二进制数据从第一个触发器的串行输入端输入,其余每个触发器的输入端均与前一个触发器的输出相连。

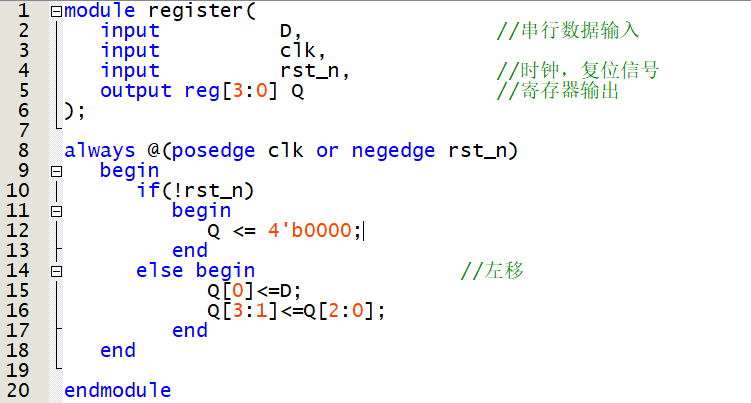

经过4个周期后,寄存器中存储的数据由原来Q_3Q_2Q_1Q_0 变为D_3D_2D_1D_0。此时,串行输入数据可以从并行数据输出端输出。该电路的串行输入数据是从低位往高位向左移位的。4位移位寄存器Verilog代码:

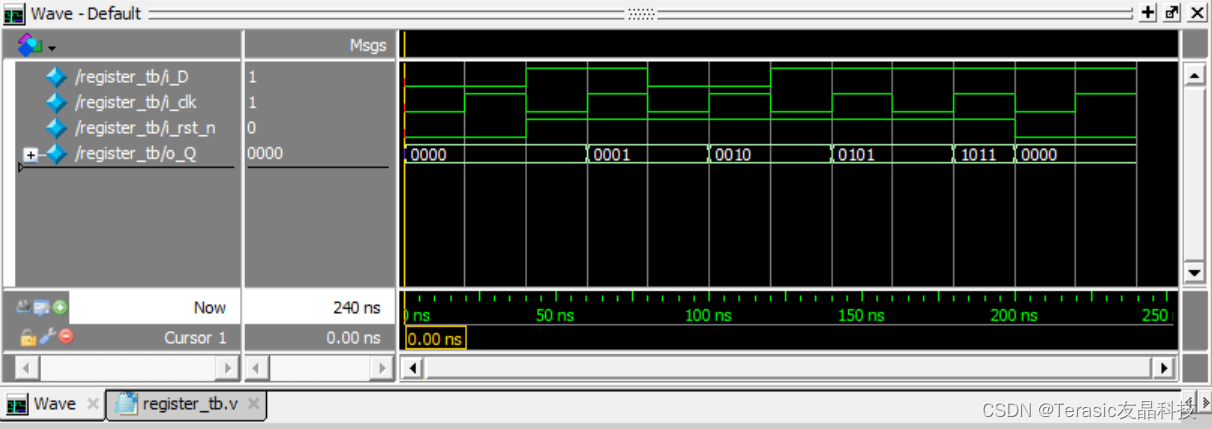

使用DE2-115开发板的开关 SW[0] 作为输入D,KEY[1] 作为脉冲时钟时钟clk输入,KEY[0]作为异步复位信号rst_n输入。在 LEDR[3:0] 上显示移位寄存器的输出状态Q。ModelSim仿真结果:

1164

1164

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?