`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2024/06/25 11:01:58

// Design Name:

// Module Name: iserdes2_test

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module iserdes2_test(

input wire clk,

input wire rst_n

);

wire clk_200M;

wire clk_100M;

wire clk_20M;

clk_wiz_0 clk_wiz_0_u

(

// Clock out ports

.clk_200M(clk_200M), // output clk_200M

.clk_100M(clk_100M), // output clk_100M

.clk_20M(clk_20M), // output clk_20M

// Status and control signals

.resetn(rst_n), // input resetn

.locked( ), // output locked

// Clock in ports

.clk_in1(clk)); // input clk_in1

// *************************************************************************** //

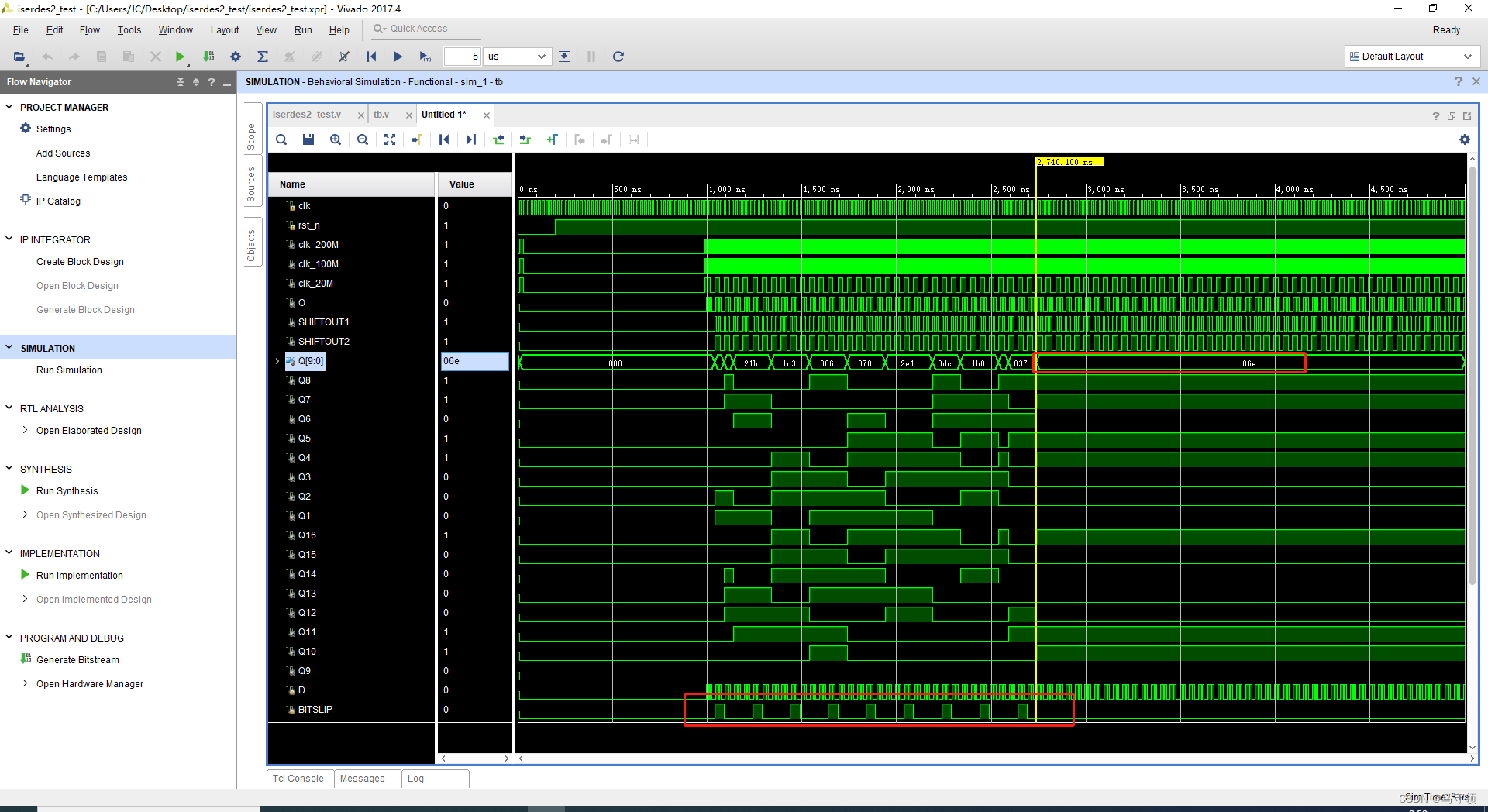

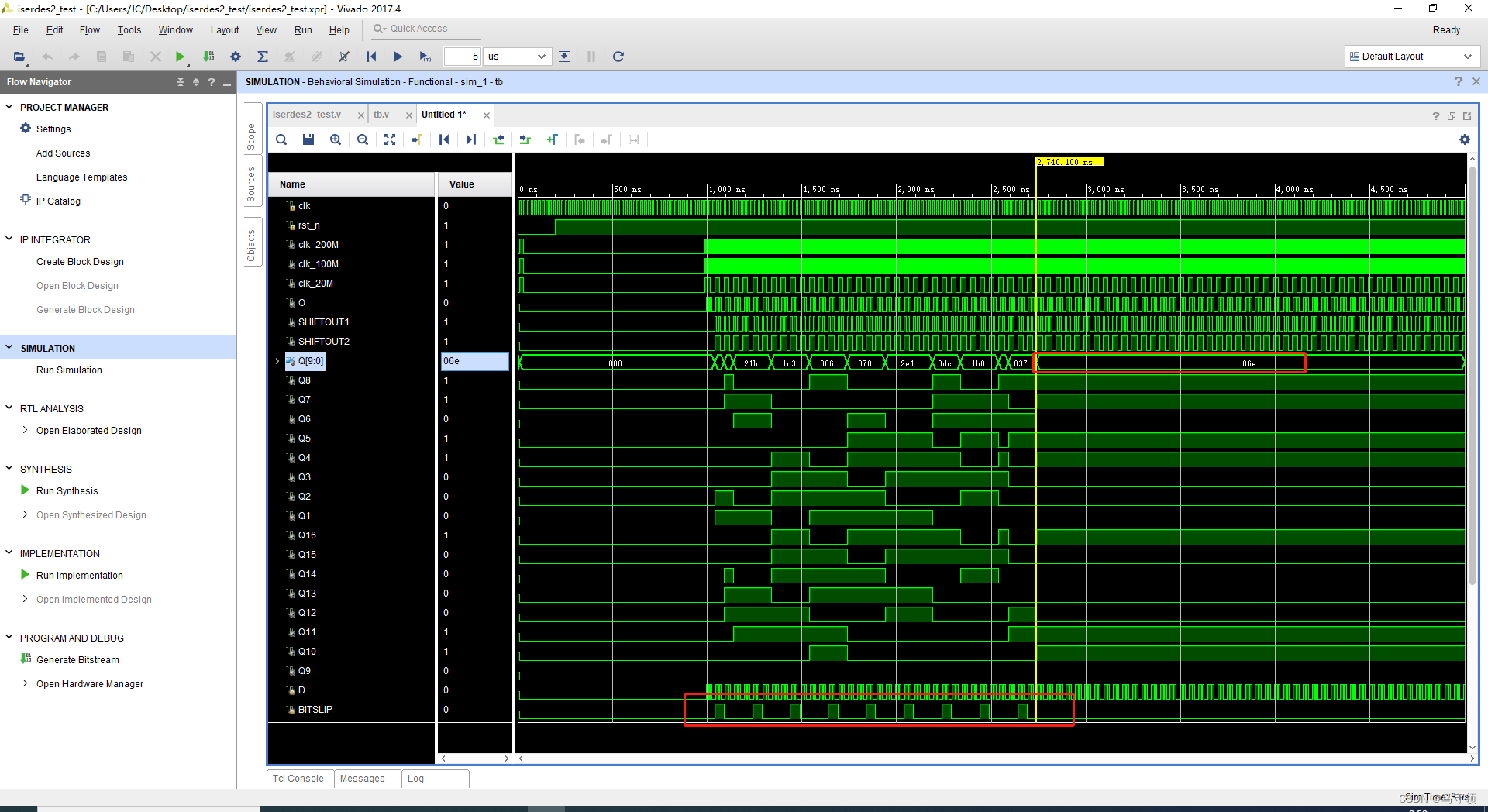

parameter data_in = 10'h06E;

wire O;

wire SHIFTOUT1;

wire SHIFTOUT2;

wire [9:0] Q;

wire Q8,Q7,Q6,Q5,Q4,Q3,Q2,Q1;

wire Q16,Q15,Q14,Q13,Q12,Q11,Q10,Q9;

reg D;

reg BITSLIP;

assign Q = {Q1,Q2,Q3,Q4,Q5,Q6,Q7,Q8,Q11,Q12};

reg [4:0] i;

always @(posedge clk_200M)begin

if(~rst_n)

i <= 0;

else if(i == 'd9)

i <= 0;

else

i <= i + 1;

end

always @(posedge clk_200M)begin

if(~rst_n)

D <= 0;

else

D <= data_in[i];

end

// *************************************************************************** //

ISERDESE2 #(

.DATA_RATE("DDR"), // DDR, SDR

.DATA_WIDTH(10), // Parallel data width (2-8,10,14)

.DYN_CLKDIV_INV_EN("FALSE"), // Enable DYNCLKDIVINVSEL inversion (FALSE, TRUE)

.DYN_CLK_INV_EN("FALSE"), // Enable DYNCLKINVSEL inversion (FALSE, TRUE)

// INIT_Q1 - INIT_Q4: Initial value on the Q outputs (0/1)

.INIT_Q1(1'b0),

.INIT_Q2(1'b0),

.INIT_Q3(1'b0),

.INIT_Q4(1'b0),

.INTERFACE_TYPE("NETWORKING"), // MEMORY, MEMORY_DDR3, MEMORY_QDR, NETWORKING, OVERSAMPLE

.IOBDELAY("NONE"), // NONE, BOTH, IBUF, IFD

.NUM_CE(2), // Number of clock enables (1,2)

.OFB_USED("FALSE"), // Select OFB path (FALSE, TRUE)

.SERDES_MODE("MASTER"), // MASTER, SLAVE

// SRVAL_Q1 - SRVAL_Q4: Q output values when SR is used (0/1)

.SRVAL_Q1(1'b0),

.SRVAL_Q2(1'b0),

.SRVAL_Q3(1'b0),

.SRVAL_Q4(1'b0)

)

ISERDESE2_master (

.O(O), // 1-bit output: Combinatorial output

// Q1 - Q8: 1-bit (each) output: Registered data outputs

.Q1(Q1),

.Q2(Q2),

.Q3(Q3),

.Q4(Q4),

.Q5(Q5),

.Q6(Q6),

.Q7(Q7),

.Q8(Q8),

// SHIFTOUT1, SHIFTOUT2: 1-bit (each) output: Data width expansion output ports

.SHIFTOUT1(SHIFTOUT1),

.SHIFTOUT2(SHIFTOUT2),

.BITSLIP(BITSLIP), // 1-bit input: The BITSLIP pin performs a Bitslip operation synchronous to

// CLKDIV when asserted (active High). Subsequently, the data seen on the Q1

// to Q8 output ports will shift, as in a barrel-shifter operation, one

// position every time Bitslip is invoked (DDR operation is different from

// SDR).

// CE1, CE2: 1-bit (each) input: Data register clock enable inputs

.CE1(1'b1),

.CE2(1'b1),

.CLKDIVP(1'b0), // 1-bit input: TBD

// Clocks: 1-bit (each) input: ISERDESE2 clock input ports

.CLK(clk_100M), // 1-bit input: High-speed clock

.CLKB(~clk_100M), // 1-bit input: High-speed secondary clock

.CLKDIV(clk_20M), // 1-bit input: Divided clock

.OCLK(1'b0), // 1-bit input: High speed output clock used when INTERFACE_TYPE="MEMORY"

// Dynamic Clock Inversions: 1-bit (each) input: Dynamic clock inversion pins to switch clock polarity

.DYNCLKDIVSEL(1'b0), // 1-bit input: Dynamic CLKDIV inversion

.DYNCLKSEL(1'b0), // 1-bit input: Dynamic CLK/CLKB inversion

// Input Data: 1-bit (each) input: ISERDESE2 data input ports

.D(D), // 1-bit input: Data input

.DDLY(1'b0), // 1-bit input: Serial data from IDELAYE2

.OFB(1'b0), // 1-bit input: Data feedback from OSERDESE2

.OCLKB(1'b0), // 1-bit input: High speed negative edge output clock

.RST(~rst_n), // 1-bit input: Active high asynchronous reset

// SHIFTIN1, SHIFTIN2: 1-bit (each) input: Data width expansion input ports

.SHIFTIN1(),

.SHIFTIN2()

);

// *********************************************************************************************************** //

ISERDESE2 #(

.DATA_RATE("DDR"), // DDR, SDR

.DATA_WIDTH(10), // Parallel data width (2-8,10,14)

.DYN_CLKDIV_INV_EN("FALSE"), // Enable DYNCLKDIVINVSEL inversion (FALSE, TRUE)

.DYN_CLK_INV_EN("FALSE"), // Enable DYNCLKINVSEL inversion (FALSE, TRUE)

// INIT_Q1 - INIT_Q4: Initial value on the Q outputs (0/1)

.INIT_Q1(1'b0),

.INIT_Q2(1'b0),

.INIT_Q3(1'b0),

.INIT_Q4(1'b0),

.INTERFACE_TYPE("NETWORKING"), // MEMORY, MEMORY_DDR3, MEMORY_QDR, NETWORKING, OVERSAMPLE

.IOBDELAY("NONE"), // NONE, BOTH, IBUF, IFD

.NUM_CE(2), // Number of clock enables (1,2)

.OFB_USED("FALSE"), // Select OFB path (FALSE, TRUE)

.SERDES_MODE("SLAVE"), // MASTER, SLAVE

// SRVAL_Q1 - SRVAL_Q4: Q output values when SR is used (0/1)

.SRVAL_Q1(1'b0),

.SRVAL_Q2(1'b0),

.SRVAL_Q3(1'b0),

.SRVAL_Q4(1'b0)

)

ISERDESE2_slave (

.O(), // 1-bit output: Combinatorial output

// Q1 - Q8: 1-bit (each) output: Registered data outputs

.Q1(Q9),

.Q2(Q10),

.Q3(Q11),

.Q4(Q12),

.Q5(Q13),

.Q6(Q14),

.Q7(Q15),

.Q8(Q16),

// SHIFTOUT1, SHIFTOUT2: 1-bit (each) output: Data width expansion output ports

.SHIFTOUT1( ),

.SHIFTOUT2( ),

.BITSLIP(BITSLIP), // 1-bit input: The BITSLIP pin performs a Bitslip operation synchronous to

// CLKDIV when asserted (active High). Subsequently, the data seen on the Q1

// to Q8 output ports will shift, as in a barrel-shifter operation, one

// position every time Bitslip is invoked (DDR operation is different from

// SDR).

// CE1, CE2: 1-bit (each) input: Data register clock enable inputs

.CE1(1'b1),

.CE2(1'b1),

.CLKDIVP(1'b0), // 1-bit input: TBD

// Clocks: 1-bit (each) input: ISERDESE2 clock input ports

.CLK(clk_100M), // 1-bit input: High-speed clock

.CLKB(~clk_100M), // 1-bit input: High-speed secondary clock

.CLKDIV(clk_20M), // 1-bit input: Divided clock

.OCLK(1'b0), // 1-bit input: High speed output clock used when INTERFACE_TYPE="MEMORY"

// Dynamic Clock Inversions: 1-bit (each) input: Dynamic clock inversion pins to switch clock polarity

.DYNCLKDIVSEL(1'b0), // 1-bit input: Dynamic CLKDIV inversion

.DYNCLKSEL(1'b0), // 1-bit input: Dynamic CLK/CLKB inversion

// Input Data: 1-bit (each) input: ISERDESE2 data input ports

.D(1'b0 ), // 1-bit input: Data input

.DDLY(1'b0), // 1-bit input: Serial data from IDELAYE2

.OFB(1'b0), // 1-bit input: Data feedback from OSERDESE2

.OCLKB(1'b0), // 1-bit input: High speed negative edge output clock

.RST(~rst_n), // 1-bit input: Active high asynchronous reset

// SHIFTIN1, SHIFTIN2: 1-bit (each) input: Data width expansion input ports

.SHIFTIN1(SHIFTOUT1),

.SHIFTIN2(SHIFTOUT2)

);

reg [3:0] bitslip_cnt;

reg [3:0] delay_cnt;

parameter IDLE_BITSLIP = 'd0,

PULL_BITSLIP = 'd1,

DELAY_0 = 'd2;

reg [3:0] state_bitslip;

always @(posedge clk_20M)begin

if(~rst_n)begin

state_bitslip <= IDLE_BITSLIP;

BITSLIP <= 1'b0;

bitslip_cnt <= 'd0;

delay_cnt <= 'd0;

end

else begin

case(state_bitslip)

IDLE_BITSLIP : begin

delay_cnt <= 'd0;

if(bitslip_cnt < 'd9)

state_bitslip <= PULL_BITSLIP;

else

state_bitslip <= IDLE_BITSLIP;

end

PULL_BITSLIP : begin

BITSLIP <= 1'b1;

bitslip_cnt <= bitslip_cnt + 1'b1;

state_bitslip <= DELAY_0;

end

DELAY_0 : begin

BITSLIP <= 1'b0;

delay_cnt <= delay_cnt + 1'b1;

if(delay_cnt == 'd1)

state_bitslip <= IDLE_BITSLIP;

else

state_bitslip <= DELAY_0;

end

default : ;

endcase

end

end

endmodule

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2024/06/25 11:04:31

// Design Name:

// Module Name: tb

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module tb();

reg clk,rst_n;

initial begin

clk = 0;

rst_n = 0;

#200

rst_n = 1;

end

always #(10) clk = ~clk;

iserdes2_test iserdes2_test_u(

.clk(clk),

.rst_n(rst_n)

);

endmodule

446

446

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?