ADC输入为14位,用32位数据去存放叠加后的值,定义一个深度为64*2=128的RAM,位宽为16位

首先确定RAM的深度和宽度,原始ADC为14位,为了满足10000次的叠加,我们采用32位的变量来存放叠加后的数据,因此采用两个RAM,存放一次的波形点数,一共64个点,我们RAM的深度位128,位宽为16位

首先准备读写时钟,因为要通过RAM对波形数据进行叠加,所以要先读后写,即先读出RAM内的值,再采集此次的ADC的值,叠加后放进RAM中,一个周期64个点循环进行该操作

读写时钟波形如图所示:

{signal: [

['input',

{name: 'clk', wave: 'P...................|...', period: 1},

{name: 'rst', wave: 'l.H.................|...'},

],

['inside',

{name: 'stack_en', wave: 'l..1............|...', phase: 0 },

{name: 'state', wave: '2..2222222222........|...', data:['','s0','s1','s2','s3','s4','s5','s6','s7','s8'], phase: 0 },

{name: 'rd_clk', wave: 'h...LhLh............|...', phase: 0 },

{name: 'rd_addr', wave: '2..2.2.2..........|...', data:['','rd_addr0','rd_addr1'], phase: 0 },

{name: 'rd_data', wave: '2..2.2.2..........|...', data:['','rd_data0','rd_data1'], phase: 0 },

{name: 'cnt_rd_data', wave: '1....0.1.........|...', data:['','rd_data0','rd_data1'], phase: 0 },

{name: 'wr_clk', wave: 'h.......lHlH........|...', phase: 0 },

{name: 'wr_addr', wave: '2.......2.2.2.......|...', data:['','wr_addr0','wr_addr1'], phase: 0 },

{name: 'wr_data', wave: '2.......2.2.2.......|...', data:['','wr_data0','wr_data1'], phase: 0 },

{name: 'cnt_wr_data', wave: '1.......0.1.........|...', data:['','rd_data0','rd_data1'], phase: 0 },

],

['output',

{name: 'xxx', wave: 'l...................|...', phase: 0.5 },

],

],

head: {text:

['tspan',

['tspan', {class:'error h3'}, '双口RAM读写控制时序'],

],

},

config: { hscale: 1}

}1. 读出RAM模块

读RAM时:声明一个cnt_ram_rd做翻转,为0时根据DSP为大端存储或者为小端存储读出对应的高16位或者低16位,为1时,将读出的数据累加后的数据写入ACC中间寄存器(读RAM时序,先读出的数据做高位,再读出的数据,加上此时ADC data后做低位)

//---------------- prepare acc H_word and accumulate --------------------------

always@(posedge ram_rd or negedge stack_en)

if(~stack_en) begin

cnt_ram_rd = 1'b1;

acc = 1'b0;

acc_h = 1'b0;

end

else begin

cnt_ram_rd = cnt_ram_rd + 1'd1;

acc_h = (cnt_ram_rd==1'b0)? ram_rd_data : acc_h; // prepare acc H_word

acc = (cnt_ram_rd==1'b0)? acc : ({acc_h[15:0],ram_rd_data[15:0]} + {18'd0,adc_data}); // accumulate

//acc = (cnt_ram_rd==1'b0)? acc : ({ram_rd_data[15:0],acc_h[15:0]} + {18'd0,adc_data}); // accumulate

end

//读RAM时序,先读出的数据做高位,再读出的数据,加上此时ADC data后做低位

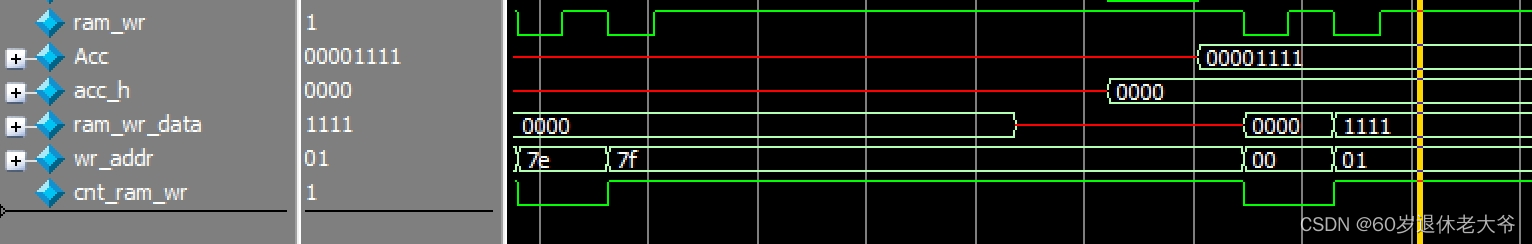

2.写入RAM模块

写RAM时,同样声明一个cnt_ram_rd做翻转,先将中间寄存器ACC的高位写入,再将ACC的低位写入,更新RAM的值

// ------------------ write Acc into ram --------------------------------

always@(negedge ram_wr or negedge stack_en)

if(~stack_en) begin

cnt_ram_wr = 1'b1;

end

else begin

cnt_ram_wr = cnt_ram_wr + 1'd1;

ram_data = (cnt_ram_wr==1'b0)? acc[31:16] : acc[15:0]; // write acc H_word firstly, L_word secondly

//ram_data = (cnt_ram_wr==1'b0)? acc[15:0]:acc[31:16]; // write acc H_word firstly, L_word secondly

end

注意事项

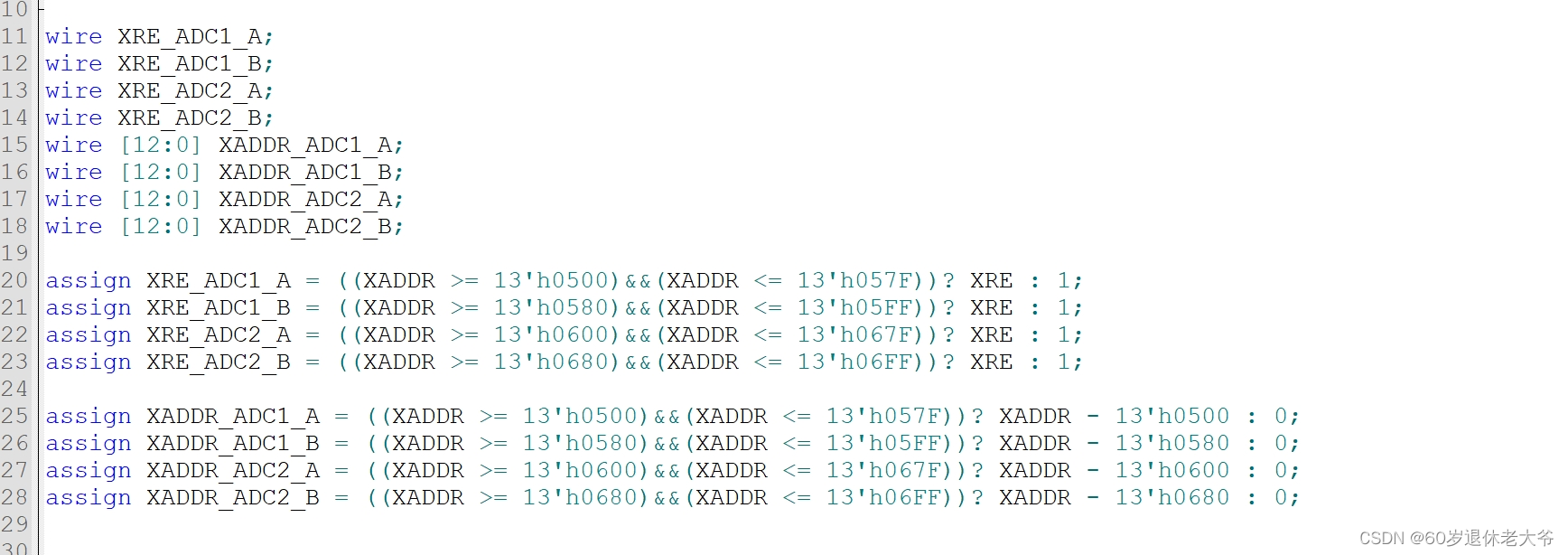

- 对XINTF总线的地址和RD信号不能直接连到叠加模块,要做限制

3212

3212

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?