名称:Quartus定时器设计verilog代码仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

基于FPGA的时长可调的定时器

设计要求:4个按键K1~K4,1个

LED。

(1)K1是复位按键,按下后LED灭

(2)按下K2~K4后松开,分别等待10

秒、20秒和30秒后,LED灯亮;直到

K1再次按下后LED灭。

设计任务:编写HDL代码,进行功能仿

真,开发板调试。

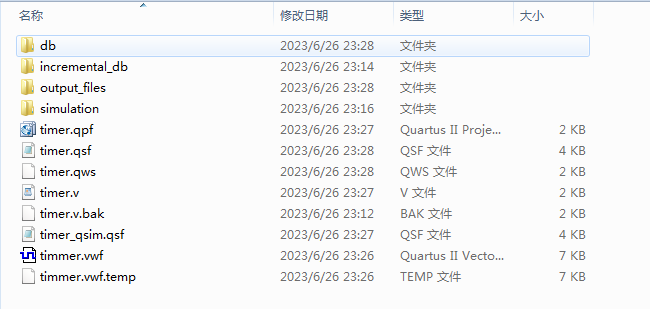

1. 工程文件

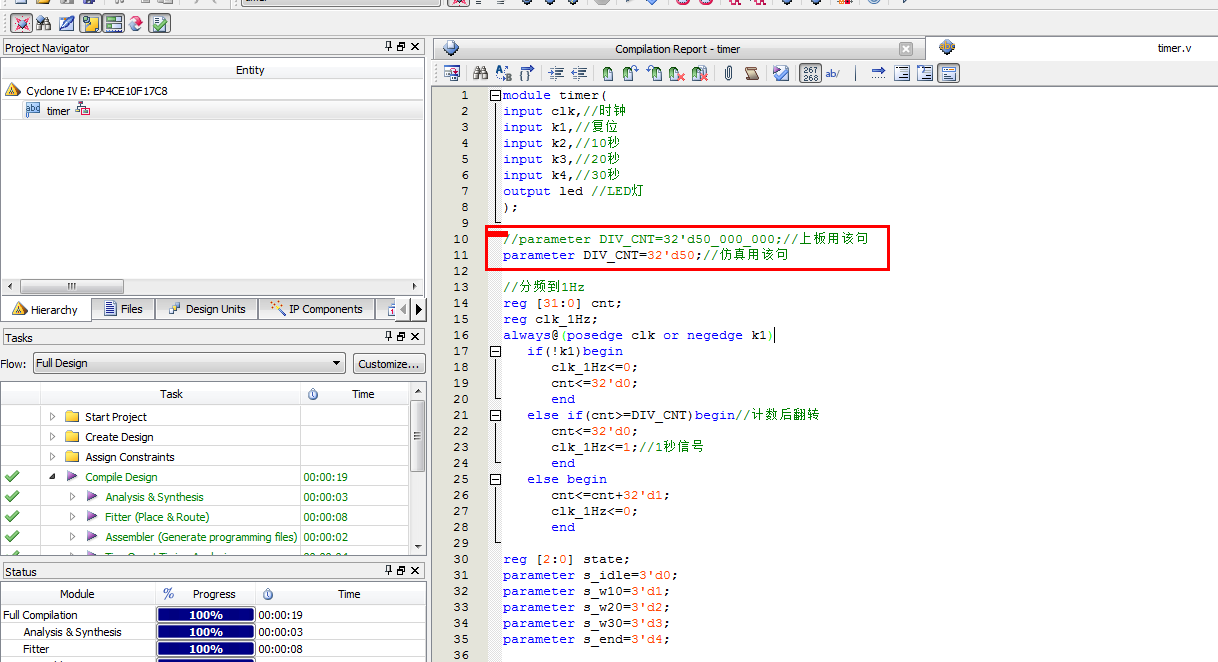

2. 程序文件

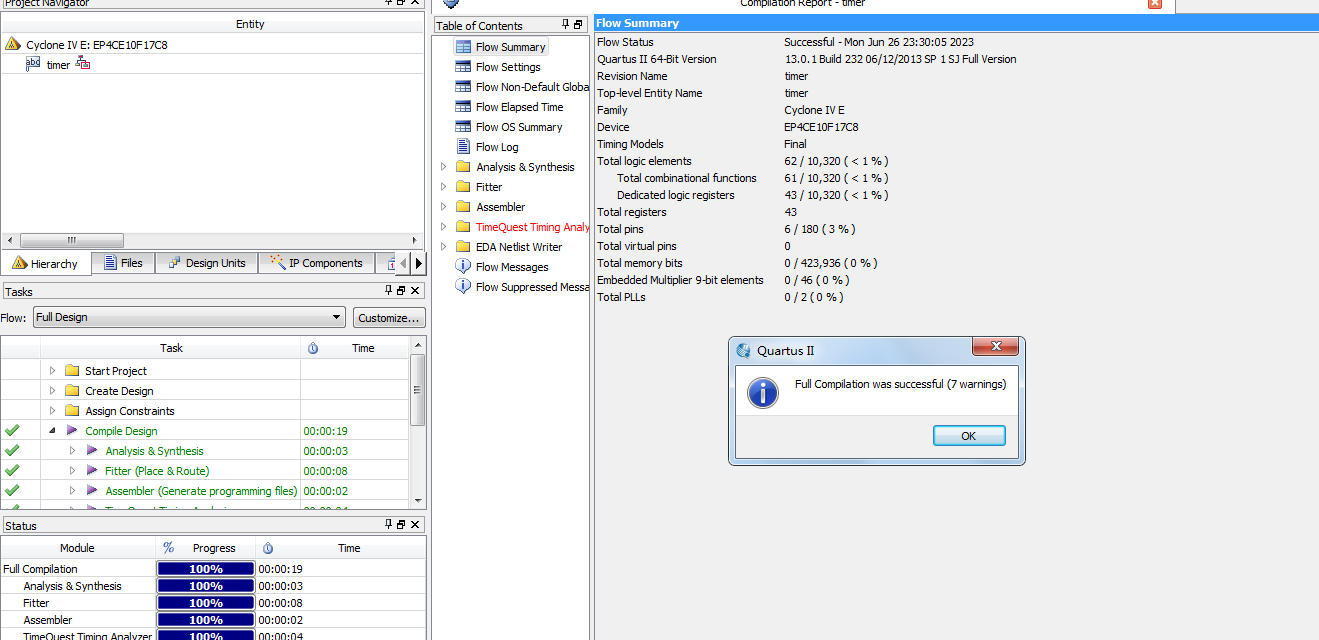

3. 程序编译

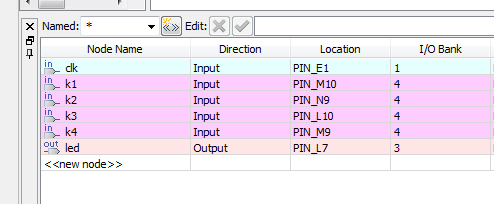

4. 管脚分配

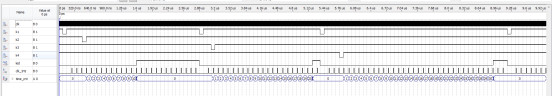

5. 仿真图

部分代码展示:

module timer( input clk,//时钟 input k1,//复位 input k2,//10秒 input k3,//20秒 input k4,//30秒 output led //LED灯 ); parameter DIV_CNT=32'd50_000_000;//上板用该句 //parameter DIV_CNT=32'd50;//仿真用该句 //分频到1Hz reg [31:0] cnt; reg clk_1Hz; always@(posedge clk or negedge k1) if(!k1)begin clk_1Hz<=0; cnt<=32'd0; end else if(cnt>=DIV_CNT)begin//计数后翻转 cnt<=32'd0; clk_1Hz<=1;//1秒信号 end else begin cnt<=cnt+32'd1; clk_1Hz<=0; end reg [2:0] state; parameter s_idle=3'd0; parameter s_w10=3'd1; parameter s_w20=3'd2; parameter s_w30=3'd3; parameter s_end=3'd4;

完整代码

扫描文章末尾的公众号二维码

610

610

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?