名称:单窗口排队机电路Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

单窗口排队机电路

给每个新来者编号,并计算队伍长度。

(1)进队、离队两个信号作为输入,当前服务号码和队长各由4个数码管显示;

(2)初始时队长0,进队号码由1顺序递增,输出编号;

(3)有人入队,长度加,有人离队长度减;

(4)工作时钟适当即可

1. 工程文件

2. 程序文件

3. 程序编译

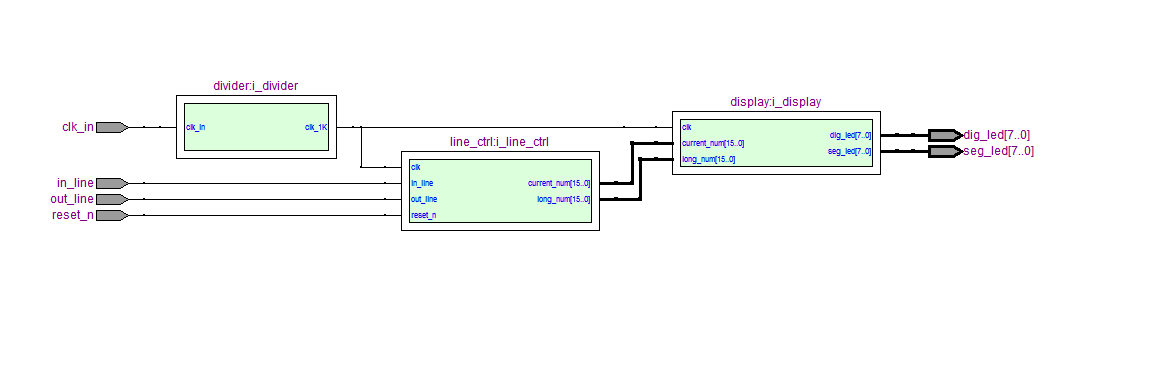

4. RTL图

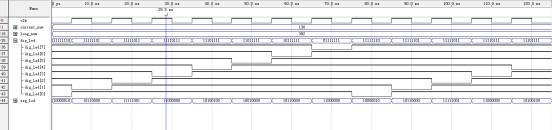

5. 仿真图

整体仿真图

分频模块

控制模块

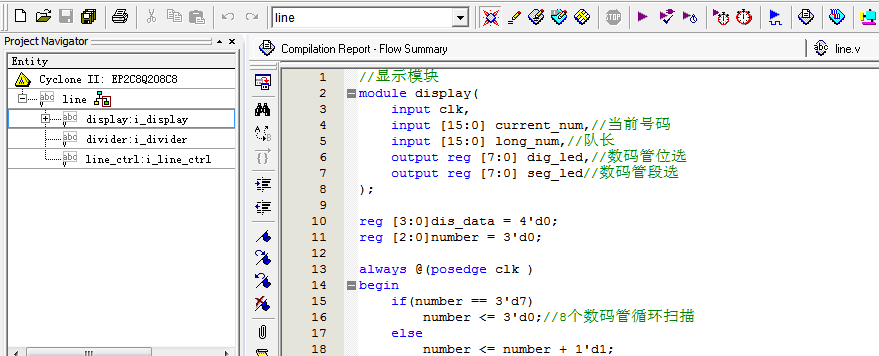

显示模块

部分代码展示:

//排队设计 module line( input clk_in,//50MHz input reset_n,//复位 input in_line,//进队 input out_line,//出队 output [7:0] dig_led,//数码管位选 output [7:0] seg_led//数码管段选 ); wire clk_1K; //50MHz分频到1KHz divider i_divider( . clk_in(clk_in),//50MHz . clk_1K(clk_1K)//分频得到1Khz ); wire [15:0] current_num;//当前号码 wire [15:0] long_num;//队长 //排队控制模块 line_ctrl i_line_ctrl( . clk(clk_1K),//1KHz . reset_n(reset_n),//复位 . in_line(in_line),//进队 . out_line(out_line),//出队 . current_num(current_num),//当前号码 . long_num(long_num)//队长 ); //显示模块 display i_display( . clk(clk_1K), . current_num(current_num),//当前号码 . long_num(long_num),//队长 . dig_led(dig_led),//数码管位选 . seg_led(seg_led)//数码管段选 ); endmodule

源代码

扫描文章末尾的公众号二维码

1730

1730

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?