module mem

(

input clk,

input en,

input we,

input [5:0]addr,

input [16-1:0]dout

);

reg[16-1:0]mem[63:0];

always@(posedge clk)

if(en&we)

mem[addr]<=din;//读入

always@(posedge clk)

if(en)//读请求

dout<=mem[addr];//读出 (延迟一个时钟输出)

endmodule

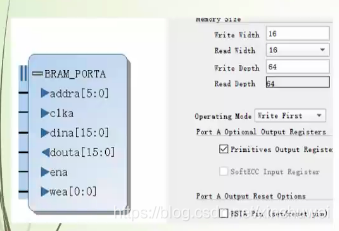

vivado 编译时会优先编译成bram,而不是编译成寄存器、查找表(很浪费资源)

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?