近期有个新项目接触了JESD204B的Transmit接口,使用Kintex UltraScale器件。总体来说,这东西非常好用,也挺简单。使用过程中在时钟配置方面遇到一点小问题,顺便记录一下。

时钟配置要求

Xilinx器件的JESD接口文档主要有两个,pg066和pg198,其中pg066是JESD204接口IP的文档,pg198是JESD204物理层文档。打开pg066的Clocking章节,可以看到一段比较重要的内容,对外部输入时钟做出了限制。

refclk是收发器的参考时钟,必须提供;glblclk主要用于用户逻辑,开发者使用该时钟产生数据源,然后送给JESD204接口IP。如果refclk大于165MHz,或者小于65MHz,那么glblclk是必须的;如果refclk和glblclk的时钟频率不一致,那么glblclk也是必须的。根据refclk的说明,refclk和glblclk是可以共用一路时钟的。

当refclk再65MHz~165MHz范围内,且与glblclk相等时,glblclk可以使用refclk。注意,任何时候refclk和glblclk都应该是同源的。下面这幅图就是refclk和glblclk共享时钟的情况。

写到这里,需要重点提一下。Ultrascale器件的时钟架构和7系列有很大的区别。对于收发器而言,UltraScale多了一个BUFG_GT。以前的器件中,IBUFDS_GTE扇出的时钟只能用于收发器。现在,将IBUFDS_GTE的另一路扇出连接到BUFG_GT,然后BUFG_GT的输出时钟就和普通BUFG扇出时钟一样,可以用于驱动用户逻辑,也可以用于MMCM/PLL等。BUFG_GT需要用下图中IBUFDS_GTE的黄色端口驱动。

refclk与glblclk可共享时钟

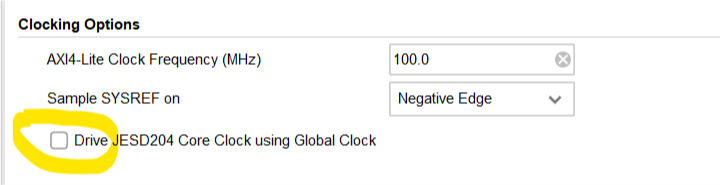

只要满足前文提到的条件,refclk和glblclk是可以共享时钟的。第一个项目中,线速率5Gbps,所以glblclk应该为5000/40=125MHz,同时收发器的参考时钟也可以接收125MHz的频率。在该设计中我使用了共享时钟方案,相关模块和接口都在Block Design中搭建。为了共享时钟,在添加IP时,记得勾掉下面的选项。

在Xilinx提供的源码中,这个与refclk共享的glblclk就是通过BUFG_GT产生的。

refclk与glblclk无法共享

第二个项目中,线路速率10Gbps,所以glblclk为250MHz,大于165MHz。这种情况下,refclk和glblclk只能使用不同的时钟。该项目需要4个link,每两个link共享一个refclk,4个link共享一个glblclk。在block design中,每个link都会生成一个symbol,而且每个symbol都会为glblclk保留一个差分的时钟输入端口,这是不可修改的。所以为了4个JESD204 IP共享一个glblclk,我没有使用block design的方式。而是修改jesd204_support.v模块的时钟端口,将原来的差分输入改为单端,然后将jesd204_clocking.v模块在顶层例化,用于产生glblclk,然后通过BUFG送给4个link。模块架构如下。

上图中,黄线标示的jesd204_clocking.v模块用于产生glblclk,供4个JESD204 IP使用;红线标示的两个jesd204_clocking.v模块用于产生refclk。

1199

1199

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?