朋友们经常看到xxxxx推出多少nm工艺,比如华为7nm,台积电3nm,三星3nm之类的新闻,那么这个nm纳米单位到底代表着什么呢

其实我们可以笼统的理解为MOS管mosfet的沟道的宽度。

这里有几个关键字,

1 笼统的理解

2 什么是mosfet沟道的宽度

3 为什么随着技术的发展,沟道的长度越来越短呢,有什么好处呢

我们来一一解答

详情可参考视频: 艺芯片技术揭秘:晶体管芯片内部物理结构布局设计标准单元全解析3nm工艺_哔哩哔哩_bilibili

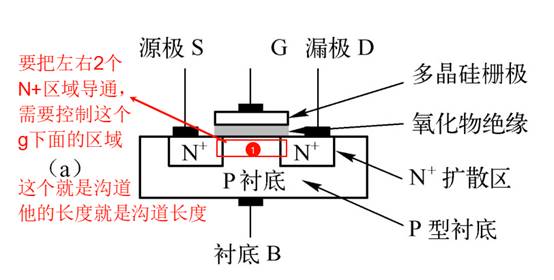

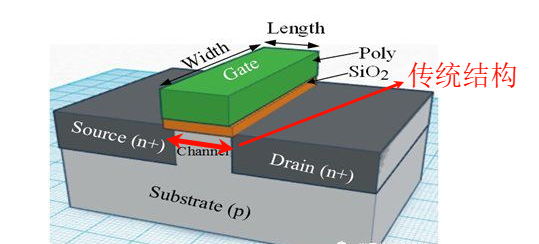

首先以上都是基于MOS管来说的,所以我们看下MOS管的基本结构

详细工作原理请参考:https://zhuanlan.zhihu.com/p/23897008022

我们看到了把,如果S和D极要想接通,必须让G栅极下面的区域导通,这个区域就形成沟道,他的长度就是沟道长度,明白了吧

而行业内定义把这个长度定义为衡量制程能力的参数,比如28nm就代表沟道长度为28nm

这样我们回答完第2个问题了

再说说第一个问题

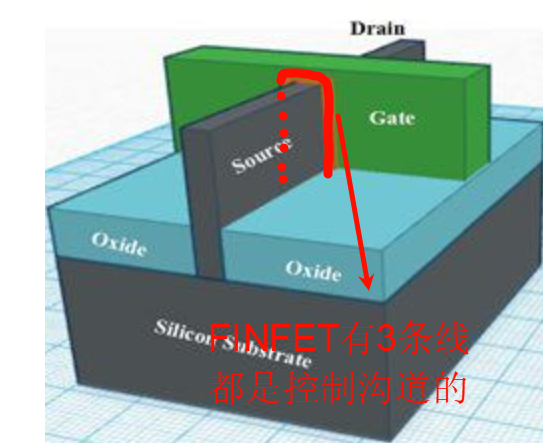

因为随着半导体技术工艺的进步,随着技术的推演,上面的沟道从平面结构演变出立体结构了, 叫做finfet沟道工艺, 按上面的参数量测方法,虽然他可能是18nm量出来,但是等效的性能却有10nm的表现, 所以我们就叫他10nm,

所以现在的3nm 2nm的工艺,实际的沟道长度肯定不止3nm或者2nm, 都是等效的

因为现在都用finfet 或者更高级的 gaafet。

见下图

最后说下第三个问题

提高芯片性能

- 提升开关速度

MOSFET 的开关过程本质上是通过栅极电压控制沟道中载流子(电子或空穴)的形成和消失。沟道长度越短,载流子在源极和漏极之间移动的距离就越短,所需的时间也就越少。根据载流子的迁移理论,载流子在电场作用下的漂移速度与电场强度和迁移率有关,在相同的电场强度下,较短的沟道使得载流子能够更快地完成迁移,从而加快了 MOSFET 的开关速度。这对于提高集成电路的工作频率至关重要,例如在 CPU(中央处理器)中,更高的开关速度意味着能够在更短的时间内完成更多的运算操作,提升了计算机的整体性能。 - 增强电流驱动能力

在 MOSFET 中,沟道可以看作是电流传导的路径。当沟道长度缩短时,沟道电阻会减小。根据欧姆定律(其中是电流,是电压,是电阻),在相同的栅极电压和源漏电压下,较小的沟道电阻会使通过沟道的电流增大,即增强了 MOSFET 的电流驱动能力。更强的电流驱动能力可以使电路更快地对信号进行响应和处理,提高了电路的性能和效率。

增加芯片集成度

- 实现更高密度的晶体管集成

集成电路的发展趋势是在有限的芯片面积上集成更多的晶体管,以实现更复杂的功能。较短的沟道长度意味着每个 MOSFET 占用的芯片面积更小。通过缩小沟道长度,可以在相同面积的芯片上放置更多的晶体管,从而大大提高了芯片的集成度。例如,从早期的大规模集成电路到如今的超大规模集成电路,晶体管数量从几千个增加到数十亿个甚至更多,这主要得益于沟道长度的不断缩短。更高的集成度使得芯片能够实现更强大的功能,如智能手机中的处理器可以集成 CPU、GPU(图形处理器)、内存控制器等多种功能模块。

降低功耗

- 减少动态功耗

动态功耗是 MOSFET 在开关过程中消耗的能量,主要与电容充放电和短路电流有关。其中,电容充放电功耗(其中是负载电容,是电源电压,是开关频率)。当沟道长度缩短时,MOSFET 的寄生电容会减小,因为沟道长度的减小会使源极、漏极和栅极之间的重叠面积减小,从而降低了电容值。在相同的电源电压和开关频率下,较小的寄生电容会使动态功耗降低。此外,较短的沟道还可以允许降低电源电压,因为在短沟道器件中,较低的电压就可以实现足够的电场来驱动载流子,进一步降低了动态功耗。 - 降低静态功耗

虽然短沟道器件可能会引入一些短沟道效应导致静态漏电流增加,但通过不断改进工艺和器件结构(如采用高 K 介质、FinFET 等技术),可以有效地控制静态漏电流。而且,从整体上看,由于芯片集成度的提高,每个功能单元的功耗可以分摊到更多的晶体管上,使得单位功能的功耗降低。

有问题可以留言,希望大家点赞关注, 下一篇我们深入讲解下芯片的前端设计,芯片布局

转载请注明 半导体老登

979

979

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?