关于PVT、corner、RC乱炖

转载EETOP论坛:https://my.oschina.net/u/4581603

时序分析的wcl、wc、lt、tc、ml

由于影响cell delay的因素主要有:工艺,电压和温度三种(PVT),由此产生各种corner:

wc:worst case slow,低电压,高温度,慢工艺 -> 一般情况下delay最大,setup 差。

wcl:worst case low-temperature,低电压,低温度,慢工艺 -> 温度反转效应时delay最大,setup差。

lt:即low-temperature,也叫bc(best case fast),高电压,低温度,快工艺 -> 一般情况下delay最小,hold差。

ml:max-leakage,高电压,高温度,快工艺 -> 温度反转效应下delay最小,hold差。

tc:typical,也叫tt,普通电压,普通温度,标准工艺 -> 各种typical。

其中的快、慢和标准工艺指manufacture时的N/PFET的驱动电流值,min对应慢工艺,max对应快工艺

温度反转就是指68nm以下的工艺,有可能出现在低温时cell delay反向变化的情况。具体到corner里,就是wcl的跑出来setup结果比wc的还差,相应ml的hold结果比lt的更差。所以一般signoff标准就要包括wcl和ml,也就是考虑了温度反转的情况

转载:link

工艺角(Process Corner)

与双极晶体管不同,在不同的晶片之间以及在不同的批次之间,MOSFETs 参数变化很大。为了在一定程度上减轻电路设计任务的困难,工艺工程师们要保证器件的性能在某个范围内。 如果超过这个范围,就将这颗IC报废了,通过这种方式来保证IC的良率。

传统上,提供给设计师的性能范围只适用于数字电路并以“工艺角”(Process Corners)的形式给出。其思想是:把NMOS和PMOS晶体管的速度波动范围限制在由四个角所确定的矩形内。这四个角分别是:快NFET和快PFET,慢NFET和慢PFET,快NFET和慢PFET,慢NFET和快PFET。例如,具有较薄的栅氧、较低阈值电压的晶体管,就落在快角附近。从晶片中提取与每一个角相对应的器件模型时,片上NMOS和PMOS的测试结构显示出不同的门延迟,而这些角的实际选取是为了得到可接受的成品率。因此,只有满足这些性能的指标的晶片才认为是合格的。在各种工艺角和极限温度条件下对电路进行仿真是决定成品率的基础。

注: SS、 TT、FF 分别是左下角的corner, 中心、右上角corner

工艺角分析,corner analysis,一般有五种情况:

fast nmos and fast pmos (ff)

slow nmos and slow pmos (ss)

slow nmos and fast pmos (sf)

fast nmos and slow pmos (fs)

typical nmos and typical pmos (tt)

t,代表typical (平均值)

s,代表slow(电流小)

f,代表fast(电流大)

PVT (process, voltage, temperature)

设计除了要满足上述5个corner外,还需要满足电压与温度等条件, 形成的组合称为PVT (process, voltage, temperature) 条件。电压如:1.0v+10% ,1.0v ,1.0v-10% ; 温度如:-40C, 0C 25C, 125C。

设计时设计师还常考虑找到最好最坏情况. 时序分析中将最好的条件(Best Case)定义为速度最快的情况, 而最坏的条件(Worst Case)则相反。

根据不同的仿真需要,会有不同的PVT组合。以下列举几种标准STA分析条件:

WCS (Worst Case Slow) : slow process, high temperature, lowest voltage

TYP (typical) : typical process, nominal temperature, nominal voltage

BCF (Best Case Fast ) : fast process, lowest temperature, high voltage

WCL (Worst Case @ Cold) : slow process, lowest temperature, lowest voltage

在进行功耗分析时,可能是另些组合如:

ML (Maximal Leakage ) : fast process, high temperature, high voltage

TL (typical Leakage ) : typical process, high temperature, nominal voltage

转载:link

RC快速理解

在众多环境因素中,有一项是net的寄生参数RC值,它可以反映net的delay大小。RC电路一阶相应,只记得电路RC值越大,电路充放电越慢,RC越小,充放电越快。所以一般来说,net的电容越小,电阻越小,这段net的delay就越小。

一段net的R值很容易理解,C值怎么算呢?这里的电容包含三个部分:同层金属线间的耦合电容,导线对地电容,还有一个导线侧面对地的边缘电容。

要算delay不能简单只看net上的RC值,毕竟供电是从前面的driving cell来的,因此还要考虑driver的RC。在早期工艺,一般cell的R值都远大于net的R值,与C相乘的时候net的R就可以忽略不计,所以对于一条net来讲,它的C是我们要重点关注的,可以说这时候电容占主导地位。C最大的时候,net delay最大,C最小的时候,net delay最小。由此我们衍生出两个corner:

cbest(Cmin) cworst(Cmax)

这两个corner都是针对同一条net而言的,就是说其实芯片的net上的RC值并不是一个定值,在实际工作时会在一个范围内浮动,我们通过抽RC的工具就可以确定这个浮动范围,然后选择上面讲的两个极值作为我们的两个RC corner。

而后,随着工艺的进步,cell的R值不再“远大于”net的R值,尤其对比较长的net,它的电阻已经到了不可忽略的地步,因此再单单选用C的极大极小来代表net delay的极大极小变得不再那么可取,所以我们要综合考虑net的RC情况。具体过程有点复杂,为了方便理解,我们要考虑的是(cell电阻+net电阻)(cell电容+net电容),把这个式子展开后可以得到一项cell电阻cell电容,可以先忽略,第二项net电阻net电容,以及cell电阻net电容+cell电容*net电阻。Net上电容和电阻有一定负相关性,外界环境变化时,net电容如果减小,电阻一般会变大。当net的电阻大到一定成都,cell电阻小到一定程度,net上的RC相乘的积就能占主导地位,这个积的极值就可以代表net的delay的极值。一般来说RC最大的时候,C要比Cmax稍微小一点,R和Rmax差不太多。这样我们就又有两个corner:

Rcbest rcworst

并不是说在先进工艺下cbest cworst corner就没用了,实际上,只有当导线比较长的时候,delay的极值才会发生在rcbest和rcworst的corner上,对于短导线、driver电阻很大的时候,cbest和cworst才能反映delay的极值。所以实际为了稳妥起见,这四个corner我们都会进行signoff。

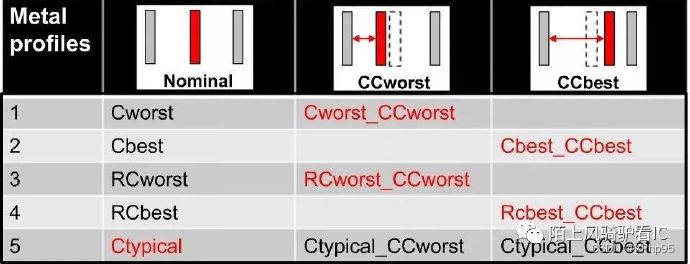

另外如果考虑DPT(double pattern technology),corner名字后面会再带一个CCworst或者CCbest。考虑OCV的variation还有可能带一个字母T

转载:https://blog.csdn.net/weixin_35286137/article/details/117151138

RC详解

Network电容:

耦合电容:Coupling capacitance=eT/S

表面电容:Surface capcitance=eW/H

边缘电容:Fringe capcitance

决定容值的因素:

介电常数:e

线宽:W

线厚:T

线间距:S

介电材料的厚度:H

随着工艺进步,W, S, T 逐代递减,表面电容跟随减小,耦合电容随之增加,耦合电容在总电容中占比增加,当线厚 T 一定时为了减少耦合电容要么增加线间距要么减小介电常数。通常为了减小噪声敏感信号线(如clock net)上的耦合电容,在物理实现时会人为增加对应信号的线宽及线间距,俗称NDR。要减小介电常数需要从材料入手,从 .18开始引入low K介电材料。

Network电阻:

R=r/W*T, r为电阻率,除了跟线宽 W 和线厚 T 相关之外,还跟温度相关,随着温度的上升而增大

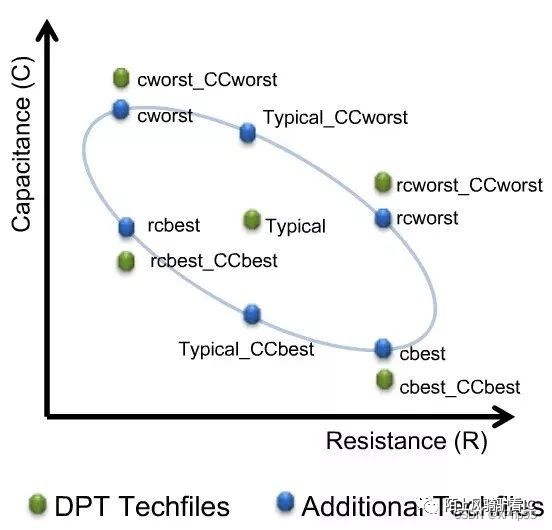

Network的单位电容和单位电阻是不可能同时最大或同时最小的。有了这些铺垫,来看一下不同工艺结点是如何定义RC corner的。

90nm 之前,Cell delay占主导,Network电容主要是对地电容,STA只需要两个RC corner即可:

Cbest(Cmin): 电容最小电阻最大

Cworst(Cmax):电容最大电阻最小

90nm 之后,netdelay的比重越来越大,而且network的耦合电容不可忽略,所以又增加了两个RC corner:

RCbest(XTALK corner): 耦合电容最大,(对地电容*电阻)最小

RCworst(Delay corner): 耦合电容最小,(对地电容*电阻)最大

至此总共有两个需要setup timing sign-off的RC corner,有四个需要hold timing sign-off的RC corner:

Setup time sign-off 的RC corner是: Cworst / RCworst

Hold time sign-off 的RC corner是: Cbest / RCbest / Cworst / RCworst

C-best:

It hasminimum capacitance. So also known as Cmin corner.

Interconnect Resistance is larger than the Typical corner.

This corner results in smallest delay for paths with short nets and can be used for min-path-analysis.

C-worst:

Refers tocorners which results maximum Capacitance. So also known as Cmax corner.

Interconnect resistance is smaller than at typical corner.

This corners results in largest delay for paths with shorts nets and can be used for max-path-analysis.

RC-best:

Refers tothe corners which minimize interconnect RC product. So also known as RC-mincorner.

Typicallycorresponds to smaller etch which increases the trace width. This results insmallest resistance but corresponds to larger than typical capacitance.

Corner has smallest path delay for paths with long interconnects and can be used for min-path-analysis.

RC-worst:

Refers tothe corners which maximize interconnect RC product. So also known as RC-maxcorner.

Typicallycorresponds to larger etch which reduces the trace width. This results inlargest resistance but corresponds to smaller than typical capacitance.

Corner has largest path delay for paths with long interconnects and can be used for max-path-analysis.

------C = a * W *L R = b *L/W RC = ab * L^2

所以对于短线来说(L很小),RC由于与L的平方成正比,非常小,电容起主要作用。对于长线RC起主要作用。

引入的DPT(Double Patterning Technology)之后,在同一层layer上要做两次mask,两次mask之间的偏差,会导致线间距变化,从而影响耦合电容值,需要将这一因素考虑到RC corner中,所以DPT 的RC corner是:Cworst_CCworst, RCworst_CCworst, Cbest_CCbest, RCbest_CCbest

Setup timesign-off 的RC corner是: Cworst_CCworst / RCworst_CCworst

Hold timesign-off 的RC corner是: Cbest_CCbest / RCbest_CCbest / Cworst_CCworst /RCworst_CCworst

除以上这些corner外,还有一个corner叫Typical corner,对应于DPT的是Ctypical_CCworst, Ctypical_CCbest,这些corner不用于timing sign-off

Q:还有一种RC corner 带后缀『_T』,只用于setup signoff,T指的是什么?

A:T代表tighten,在rc的variation上的sigma分布比不带T的更紧,因此只能用于setup,hold不推荐。Appleto Apple地比较,T的variation更小,理论看到的rc变化更小,单从setup产生violation的可能性更小。至于悲观还是乐观,除非自己定criteria,其余的follow foundry或者vendor的rule最重要。

Q:为什么setup既需要sign-off C-corner又需要sign-offRC-corner?

A:因为C-corner表示『电容』最大/最小,而RC-corner是『电容*电阻』最大/最小。通常对于短线而言,电容占主导地位,C-corner可以cover RC-corner,但对于长线则电阻占主导地位,C-corner无法cover RC-corner,而是反过来RC-corner去cover C-corner。而没人保证一个设计里只有短线没有长线,也没权威对长短的幅度有量化的定义,所以最保险的就是两者分别sign-off。

Q:为什么hold需要sign-off所有的corner?

A:对于hold而言,根据其仿真曲线,相互之间都无法完全覆盖,故需要sign-off所有corner。

Q:金属电阻是否跟density/spacing相关?为什么方块电阻跟density/spacing相关?

A:就电阻本身而言,阻值跟density没有关系,只跟金属线自身的宽厚和电阻率相关,但是,在半导体制造过程中,由于工艺偏差,电阻跟金属线的density是相关的。此时,电阻率是线宽跟线间距的函数。这一关系,在foundry给的工艺文件里都有相应的描述,这些都是在抽RC时需要考虑的因素。

就电阻本身是跟spacing没有无关的,但在半导体制造过程中,因为铜软,所以在dishing时会把铜线切掉一些,这跟那个范围的金属线密度相关,而且这个关系好像也不是线性的。线的密度不同,会使得制造过程对线的厚度造成的影响不同,线厚度被改变了,那阻值自然被改变了。在QRC抽RC的时候会把这一效应模拟成『电阻率=f(W,S)』。 这一效应在foundry给的工艺文件里有相应的描述

1026

1026

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?