3.1 模块介绍

模块(module)是Verilog 的基本描述单位,是用于描述某个设计的功能或结构及与其他模块 通信的外部端口。

模块在概念上可等同一个器件,就如调用通用器件(与门、三态门等)或通用宏单元(计数器、 ALU、CPU)等。因此,一个模块可在另一个模块中调用,一个电路设计可由多个模块组合而成。一 个模块的设计只是一个系统设计中的某个层次设计,模块设计可采用多种建模方式。

Verilog 的基本设计单元是“模块”。采用模块化的设计使系统看起来更有条理也便于仿真和测试, 因此整个项目的设计思想就是模块套模块,自顶向下依次展开。在一个工程的设计里,每个模块实现 特定的功能,模块间可进行层次的嵌套。对大型的数字电路进行设计时,可以将其分割成大小不一的 小模块,每个小模块实现特定的功能,最后通过由顶层模块调用子模块的方式来实现整体功能,这就 是Top-Down 的设计思想。本书主要以Verilog硬件描述语言为主,模块是Verilog的基本描述单位, 用于描述每个设计的功能和结构,以及其他模块通信的外部接口。

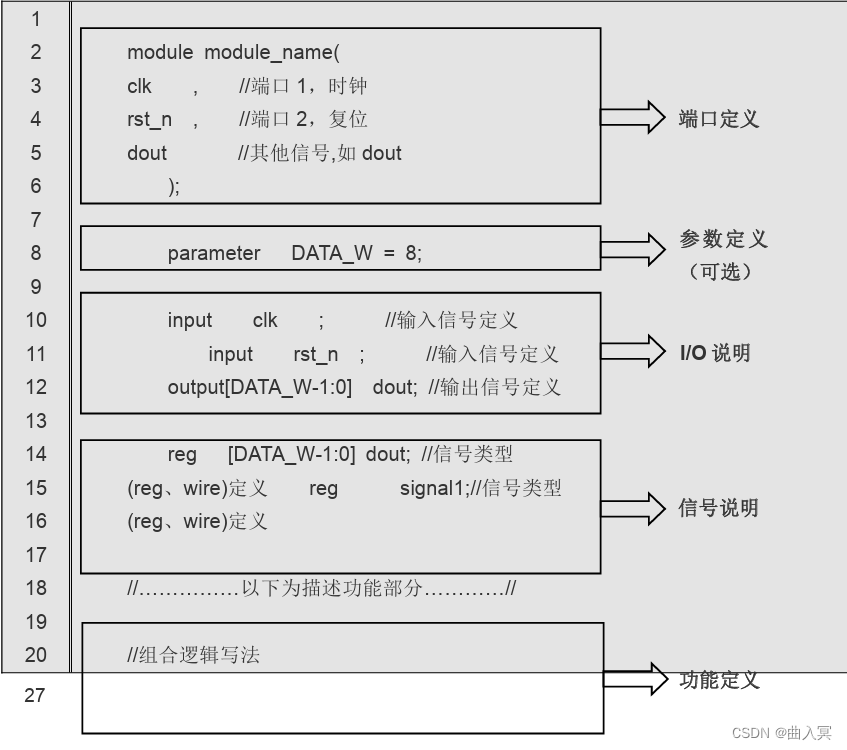

模块有五个主要部分:端口定义、参数定义(可选)、 I/O说明、内部信号声明、功能定义。 模块总是以关键词module开始,以关键词endmodule结尾。它的一般语法结构如下所示:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6875

6875

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?