集成电路是极为复杂的器件,几乎不可能达到完美,大多数器件都存在微小的不足和缺陷并导致失效,这一部分器件会在多年工作后突然无法继续使用,工程师们在可靠性实验中发现这些问题,在极端工作环境下可以加速老化来发现这些问题,但是并不是每一个设计缺陷都可以通过测试来发现,为了避免这些问题,版图绘制者要时刻牢记失效机制,并在版图绘制中考虑全面,从源头上减少失效的发生。

失效机制:

1、电迁移现象

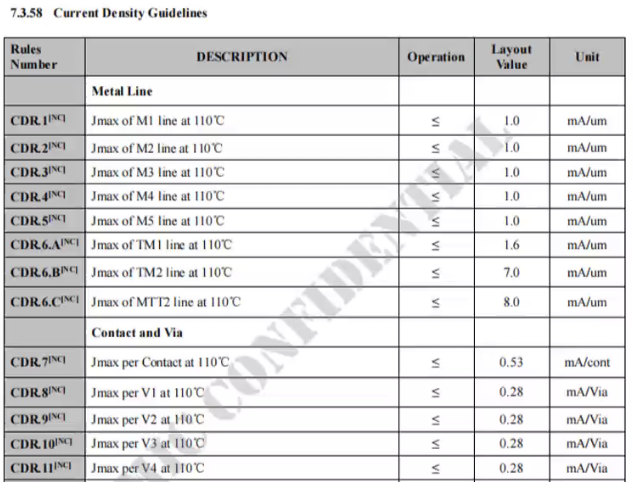

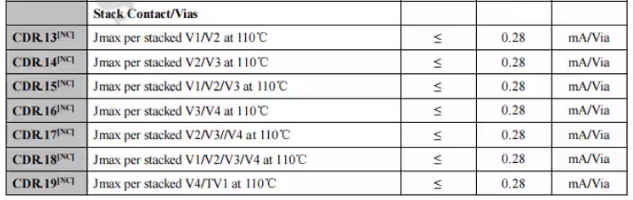

电迁移现象电迁移现象是因为极高电流密度产生的慢性损耗,主要原因是因为走线过窄导致。所以在版图设计过程中对于大电流的走线一定要根据金属过电流能力留出一定的金属宽度余量以防止出现电迁移失效。

根据LDO的带载能力,估计金属线宽度。

1、从工艺层面进行改进,为了改善电迁移现象,在大部分的金属互连中,使用的金属材料是铝,为了提高金属走线的过电流能力,一般会参杂一定比例的铜。

2、从版图层面进行改进,在版图绘制过程中就需要版图设计者对大电流的走线设置合理的走线线宽,保证芯片在极限工作环境下满足过电流要求。

2、天线效应

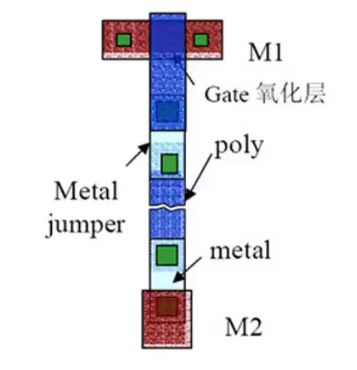

2、天线效应在干法刻蚀的时候会在晶片表面淀积电荷,如果连接到绝缘栅极的走线过长,在刻蚀的过程中,过长的走线就像是一条天线,收集刻蚀产生的静电荷。由于MOS器件属于压控型器件,栅极为绝缘氧化物,没有电荷泄放路径,不断积累的电荷达到一定程度后,就会对栅极造成介质击穿,这就是天线效应。

“天线”收集的电荷量主要由走线面积决定,由此可知天线效应主要与栅极面积和连接到栅极走线的面积相关,在设计规则文件中都会给出天线效应的计算公式,也可以直接通过运行天线效应设计规则文件进行检查。

预防天线效应

:1、金属走线跳线来消除天线效应,因为芯片的制造是一层一层不断通过淀积和刻蚀来完成的,通过“向上跳线法”将金属走线往更高的层走线可以消除天线效应。

2、如果金属走线跳线到顶层依然无法消除天线效应,这个时候就需要添加(N+/PSUB或P+/Nwell)二极管来消除天线效应的影响。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1496

1496

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?