目录

题目

用verilog实现无毛刺时钟切换电路。

核心思路

0:无毛刺的时钟切换英文名叫:Glitch-free clock switching circuit

1:如果单纯的在sel高是选择clka输出,sel为低时选择clkb输出,那么很有可能在时钟切换的时刻出现毛刺,这甚至会导致电路故障。所以要进行专门的时钟切换电路的设计,保证电路切换中不会有毛刺的出现,这一根本原理在时钟切换过程中,要在原时钟和待切换时钟的低电平进行切换。

2:clk0和clk1是无关时钟,如何实现二者之间的一个无毛刺切换是接下来需要解决的问题?

先从最容易相当的设计说起:

可以使用纯组合逻辑来设计时钟切换电路,但是这种设计不可避免的产生毛刺:

如下,两种一个道理:

如何改进这种设计呢?

相关时钟源的时钟切换电路:

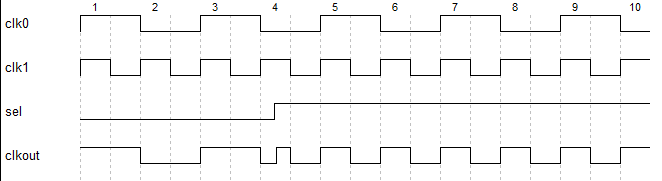

从前面组合逻辑时钟切换电路的设计,我们得出的切换波形如上:

可见,会产生毛刺,而产生毛刺的原因在于sel信号改变的位置没有和需要切换的时钟对齐。

如何改进这种问题呢?

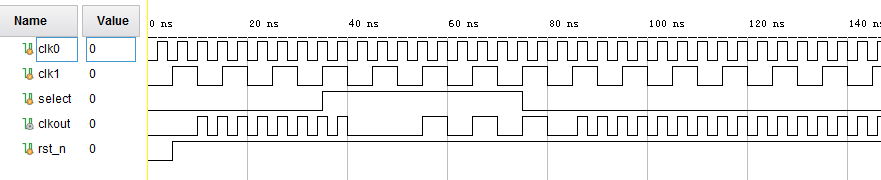

我们可以用当前时钟的下降沿来采样(sel与反馈的输出相与的结果),可以简单地理解为采样sel信号。具体的设计如下:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2749

2749

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?