文章目录

1、序列检测器

题目:

用Moore型状态机实现序列“1101”从右到左的不重叠检测。

1、请画出状态转移图,其中状态用S1,S2,…来标识。

2、针对这个具体设计,如何衡量验证的完备性?

Moore型:状态机的状态变化仅和当前状态有关。

Mealy型:不仅和当前状态有关,也和输入有关。

1.1 状态机实现序列检测器

1.11不重叠检测和重叠检测

看下图即可:

题目分析:

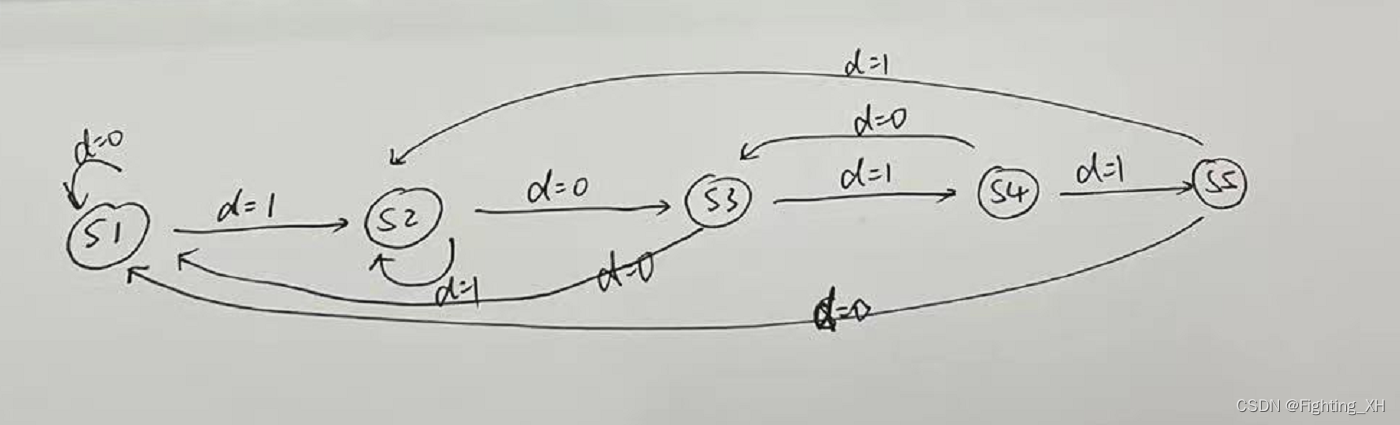

从右到左不重叠检测1101,也就是从左到右不重叠检测1011,因此我们可画出状态图:

1.1.2 verilog实现

//序列检测器1011,不重叠检测

module test(

input clk,

input rst_n,

input d, //序列输入

output reg

订阅专栏 解锁全文

订阅专栏 解锁全文

14

14

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?