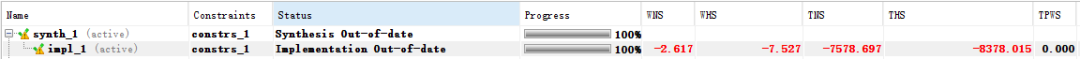

VIVADO中时序报告中WNS,WHS,TNS,THS含义

运行“report_timing”或“report_timing_summary”命令后,会注意到 WNS、TNS、WHS 和 THS。

WNS 代表最差负时序裕量 (Worst Negative Slack)

TNS 代表总的负时序裕量 (Total Negative Slack),也就是负时序裕量路径之和。

WHS 代表最差保持时序裕量 (Worst Hold Slack)

THS 代表总的保持时序裕量 (Total Hold Slack),也就是负保持时序裕量路径之和。

这些值告诉设计者设计与时序要求相差多少。如果为正值,则说明能达到时序要求,若为负值,则说明时序达不到要求。

但是并不代表有时序警告功能实现不了,只是工程不稳定。更加或者删减模块甚至重新编译都会出现问题。这时候可以打开implementation查看时序警告的位置。

所谓时序达不到要求就是指不能够满足建立保持时间,应该去关注对于时序的约束。

时序约束包括很多,后面会针对这方面专门出一个专栏。主要的是对时钟信号的周期、占空比的约束,时钟分组,时钟抖动,还有IO的输入输出延时约束等

来源:https://support.xilinx.com/s/article/51455?language=zh_CN

NOW现在行动!

学习Xilinx FPGA最好的资料其实就是官方手册,下表总结了部分手册的主要介绍内容,关注我,持续更新中......

| 文件名 | 主标题 | 内容简单介绍 | 是否有中文版 | |

| UG476 | 7 Series FPGAs GTX/GTH Transceivers | GTX和GTH介绍,PCIe、serdes等学习必备 | 否 | |

| UG471 | 7 Series FPGAs SelectIO Resources | 描述 7 系列 FPGA 中可用的 SelectIO资源。 | 否 | |

| UG1114 | PetaLinux Tools Documentaton | PetaLinux 工具文档 参考指南 | 是,V2019.2 | |

| UG949 | UltraFAST 设计方法指南(适用于 Vivado Design Suite) | 赛灵思® UltraFast™ 设计方法是用于为当今器件优化设计进程的一套最佳实践。这些设计的规模与复杂性需要执行特定的步骤与设计任务,从而确保设计每一个阶段的成功开展。依照这些步骤,并遵循最佳实践,将帮助您以最快的速度和最高的效率实现期望的设计目标 | 是,V2018.1 | |

| IP手册 | pg057 | FIFO Generator | FIFO生成器IP使用手册 | 否 |

| pg104 | Complex Multiplier | 复数乘法器IP使用手册 | 否 | |

| pg122 | RAM-Based Shift Register | 移位寄存器IP使用手册 | 否 |

推荐阅读

【Vivado那些事】Vivado中常用的快捷键(二)其他常用快捷键

图书推荐|ARM Cortex-M0 全可编程SoC原理及实现

Github 上有哪些优秀的 VHDL/Verilog/FPGA 项目

高速串行通信常用的编码方式-8b/10b编码/解码

Verilog计时(微秒、毫秒和秒)脉冲的产生及同步整形电路

再说System Verilog 与 Verilog 的关系

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?