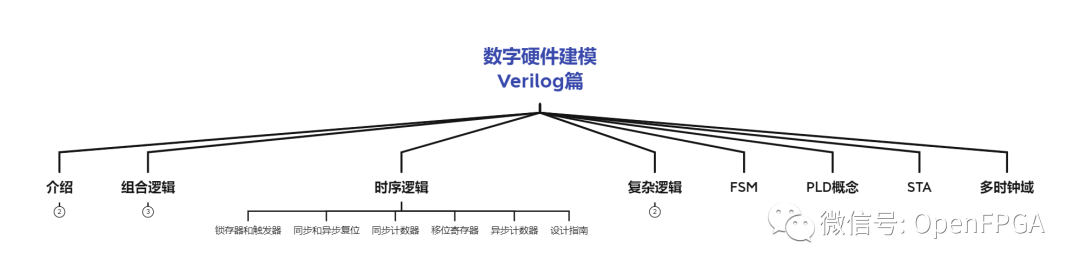

Verilog时序逻辑硬件建模设计(一)锁存器D-latch和触发器Flip-Flop

没有任何寄存器逻辑,RTL设计是不完整的。RTL是寄存器传输级或逻辑,用于描述依赖于当前输入和过去输出的数字逻辑。

时序逻辑

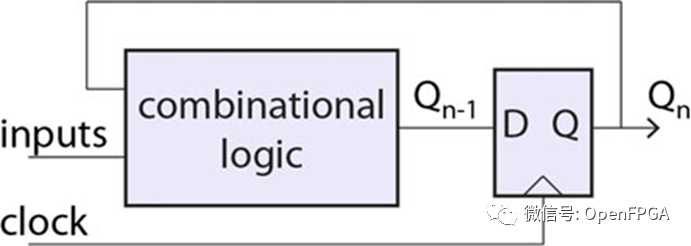

时序逻辑被定义为数字逻辑,其输出是当前输入和过去输出的函数。因此,时序逻辑可以保存二进制数据。时序逻辑元件是锁存器和触发器,用于设计给定的功能。对于RTL设计工程师来说,了解基于时钟的逻辑电路的高效RTL设计是至关重要的。在复杂的设计中,时序逻辑元件用于保存大量数据。该逻辑在时钟上触发。在实际应用中,描述可以在时钟的正边缘或负边缘触发的逻辑电路。人们总是期望所设计的电路在有限的时钟周期内产生有限的输出。图5.1描述了在时钟正边缘触发的基本时序逻辑。逻辑输出是当前输入和过去输出的函数。

图5.1基本时序逻辑

图5.1基本时序逻辑

正电平触发D锁存器D-latch

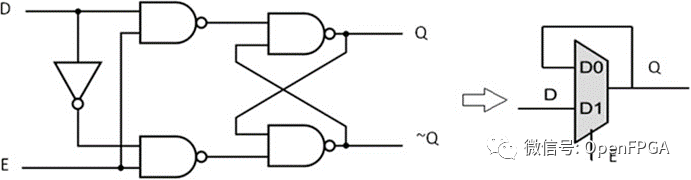

锁存器是对电平敏感的元器件。在D锁存器中,D代表数据输入。锁存器对正或负时钟电平或使能敏感。正电平触发锁存器如图5.2所示,真值表如表5.1所述。如表5.1所示,对于锁存器使能E等于正电平(逻辑1)输出,Q等于数据输入D;,否则输出保持在先前状态(过去输出),并由Qn-1显示。时序如图5.3所示。

图5.2正电平触发D锁存器表5.1正电平触发D锁存器真值表

图5.2正电平触发D锁存器表5.1正电平触发D锁存器真值表

| E | D | Q | ~Q |

|---|---|---|---|

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

| 0 | X | Qn−1 | ~Qn−1 |

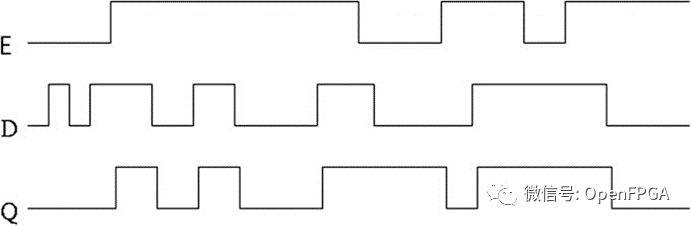

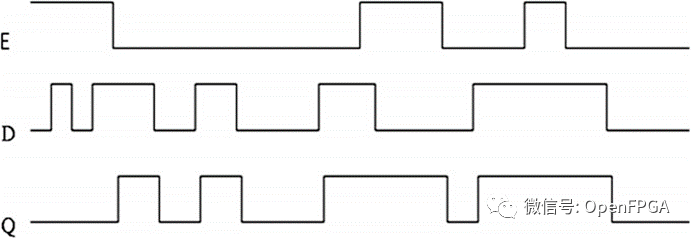

图5.3正电平触发D锁存器的时序

图5.3正电平触发D锁存器的时序

从时序可以清楚地看出,在使能输入“E”等于正电平的时间段内,输出Q等于数据输入D。所以D锁存器在这段时间内是透明的。在“E”的负电平(逻辑“0”)期间,D锁存器保持上一个值。

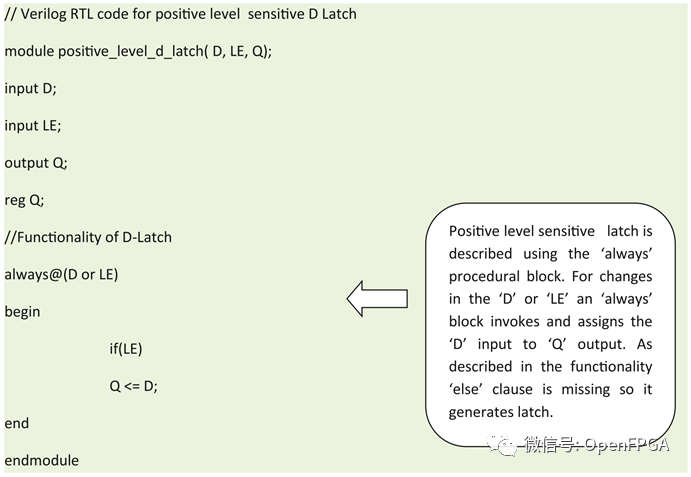

现在读者心中的重点是如何使用Verilog描述正电平触发D锁存器。可视化和描述设计功能非常简单。示例5.1描述了正电平触发D锁存器的Verilog RTL,综合后硬件如图5.4所示。

示例5.1正电平触发D锁存器的可综合RTL

示例5.1正电平触发D锁存器的可综合RTL

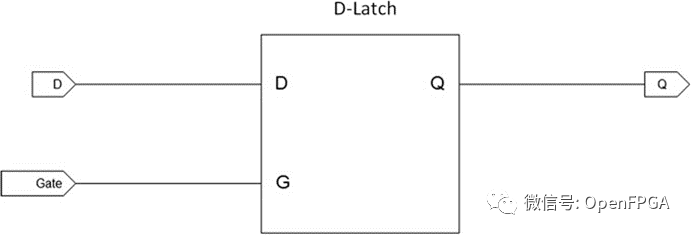

图5.4正电平触发D锁存器

图5.4正电平触发D锁存器

负电平触发D锁存器

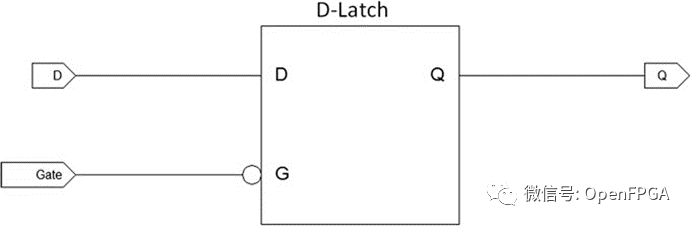

负电平触发D锁存器的真值表如表5.2所述,它具有激活的低电平或负电平触发的锁存器启用(“LE_n”)、数据输入“D”和输出“Q”。等效门级表示如图5.5所示。锁存器在“LE_n”的负电平上起到透明作用(参考上一部分),并在“LE_n”的正电平期间保持数据。时序如图5.6所示。

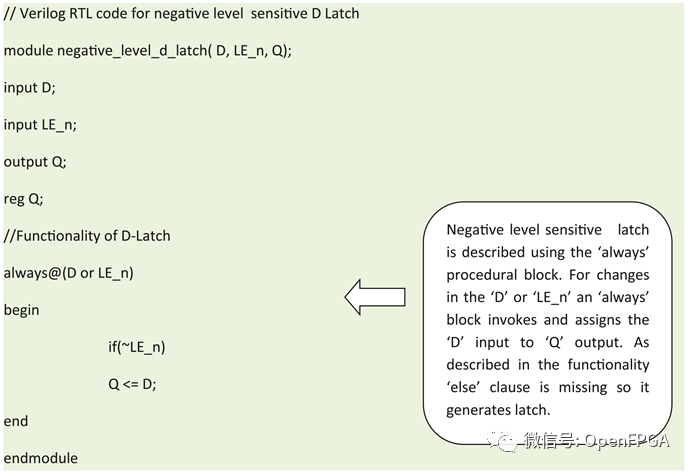

Verilog RTL描述如例5.2所示,综合硬件如图5.7所示。

表5.2负电平触发D锁存器真值表| LE_n | D | Q | ~Q |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | X | Qn-1 | ~Qn−1 |

图5.5负电平触发D锁存器

图5.5负电平触发D锁存器

图5.6负电平触发D锁存器的时序

图5.6负电平触发D锁存器的时序

示例5.2负电平触发D锁存器的可综合verilog RTL

示例5.2负电平触发D锁存器的可综合verilog RTL

图5.7负电平触发锁存器的综合硬件

图5.7负电平触发锁存器的综合硬件

触发器Flip-Flop

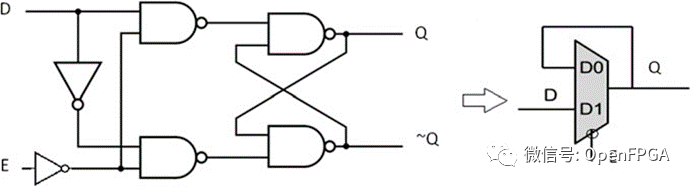

触发器是一种边缘触发逻辑电路。它可以在时钟的正边缘或负边缘触发。触发器可以通过级联使用正负电平触发的锁存器来实现。触发器用作存储器存储元件。触发器分为set-reset (SR), JK, D, 和 toggle触发器。在ASIC/FPGA设计中D触发器用作时序电路元件,其中D代表数据输入。下一节将讨论正、负边缘触发触发器。

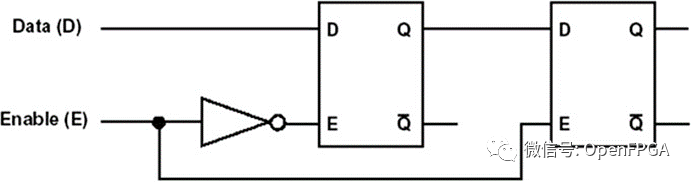

正边沿触发D触发器

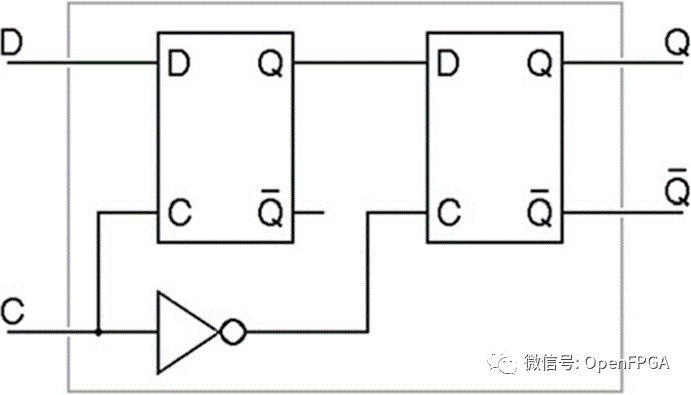

正边沿触发D触发器是在时钟的正边沿触发的。实际上,没有逻辑门可以在边缘触发!正边沿触发D触发器可以视为负电平敏感锁存器和正电平触发锁存器的连接。正边沿触发D触发器的逻辑电路如图5.8所示。

图5.8正边沿触发D触发器

图5.8正边沿触发D触发器

负边沿触发D触发器

负边沿触发D触发器是在时钟负沿上触发的。负边沿触发D触发器可以视为正电平触发锁存器和负电平触发锁存器的连接。正边沿触发D触发器的逻辑电路如图5.9所示。

图5.9负边沿触发D触发器

图5.9负边沿触发D触发器

Verilog/SV代码检查器-Lint 建模规则检查器与 Verilator

本文深入探讨了Verilog中的时序逻辑硬件建模,重点介绍了D-latch和Flip-Flop。D-latch包括正电平触发和负电平触发两种类型,其输出取决于当前输入和过去的输出。而Flip-Flop作为边缘触发逻辑电路,分为正边沿和负边沿触发D触发器,它们在数字逻辑设计中起到关键作用,常用于存储和传输数据。通过示例和逻辑电路图,文章详细阐述了这些元件的工作原理和Verilog实现方式。

本文深入探讨了Verilog中的时序逻辑硬件建模,重点介绍了D-latch和Flip-Flop。D-latch包括正电平触发和负电平触发两种类型,其输出取决于当前输入和过去的输出。而Flip-Flop作为边缘触发逻辑电路,分为正边沿和负边沿触发D触发器,它们在数字逻辑设计中起到关键作用,常用于存储和传输数据。通过示例和逻辑电路图,文章详细阐述了这些元件的工作原理和Verilog实现方式。

4780

4780

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?