1.时钟组件

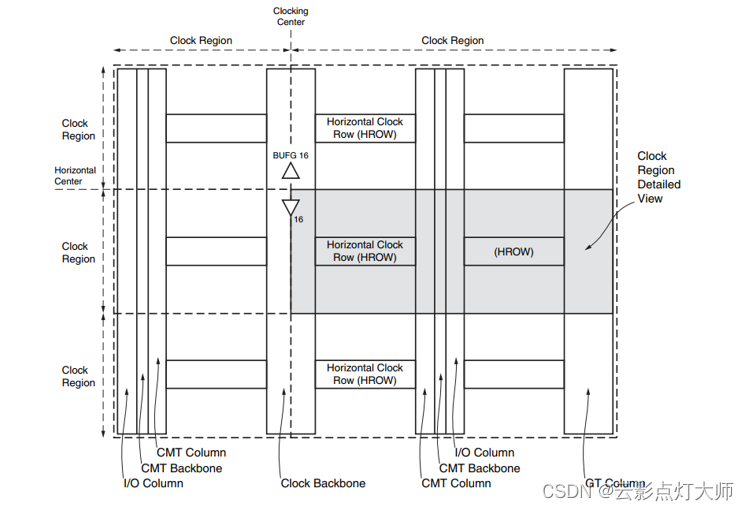

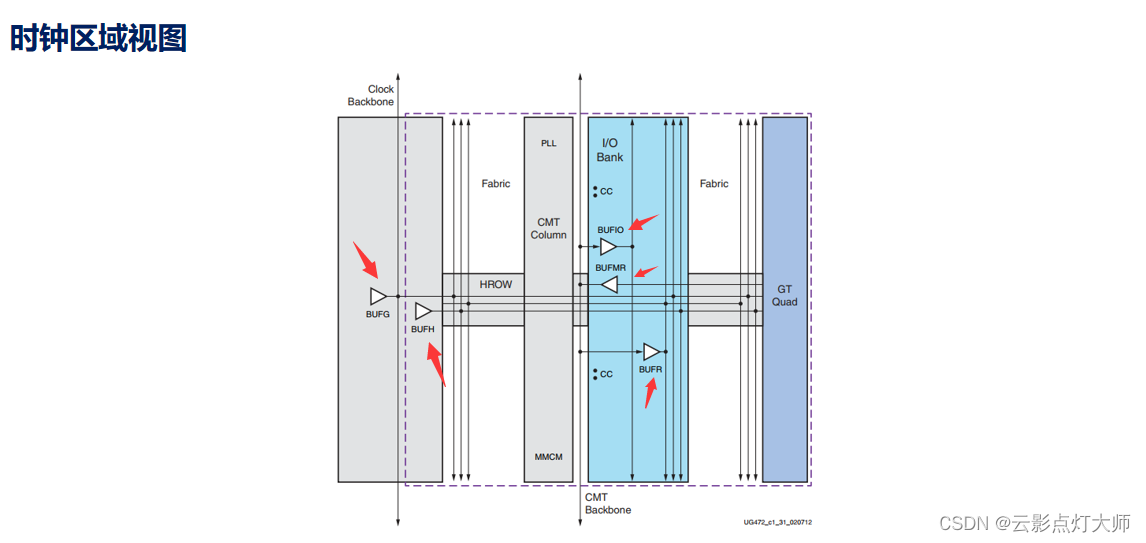

时钟结构

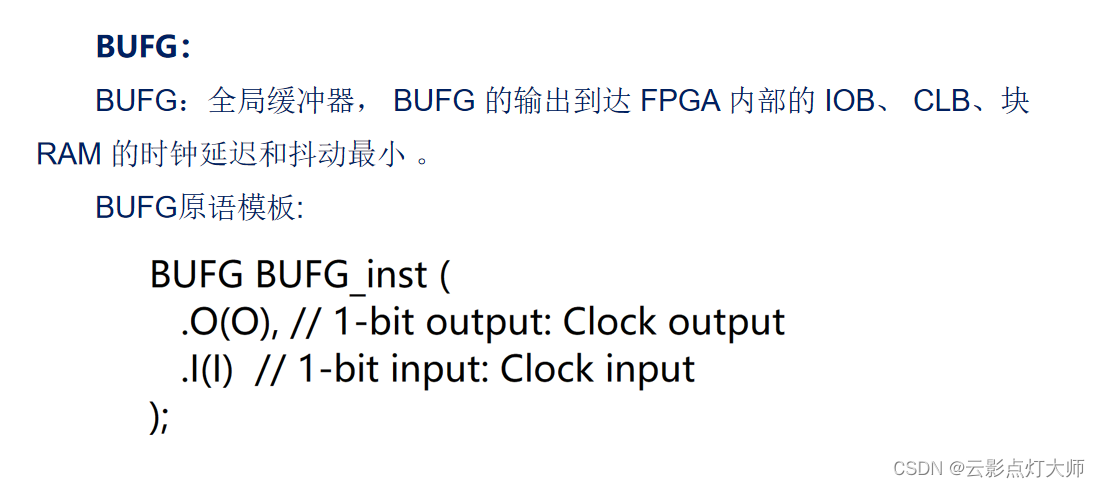

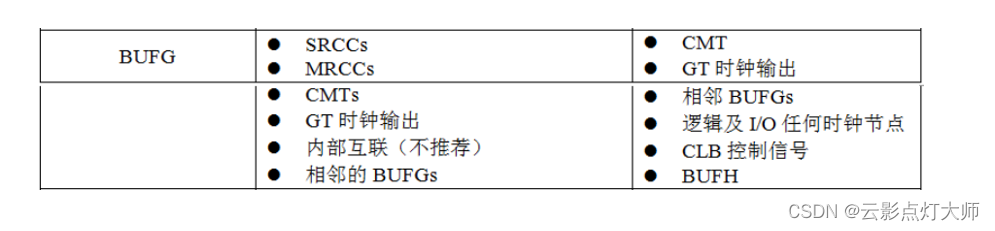

(1)BUFG

输入输出

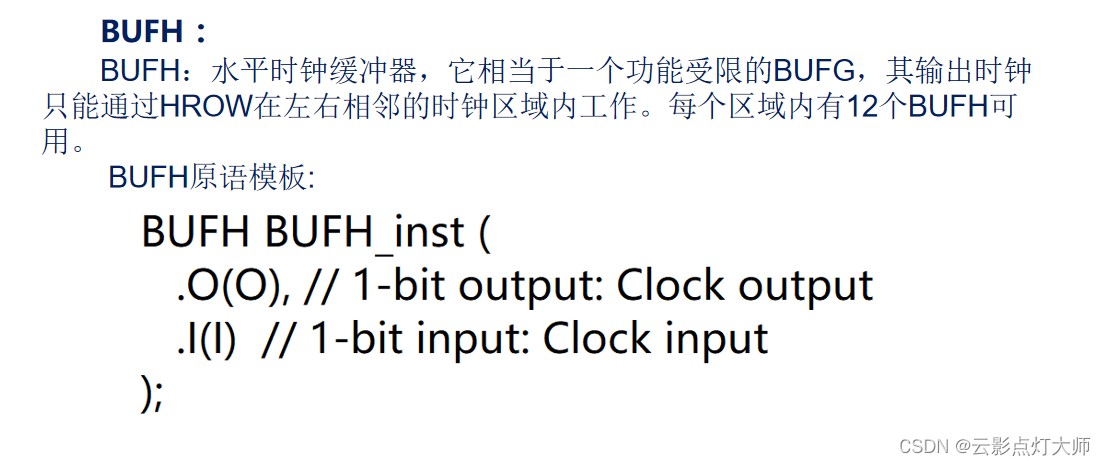

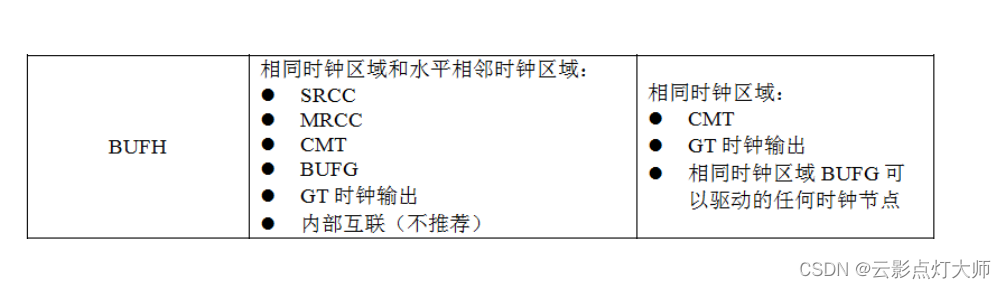

(2)BUFH

输入输出

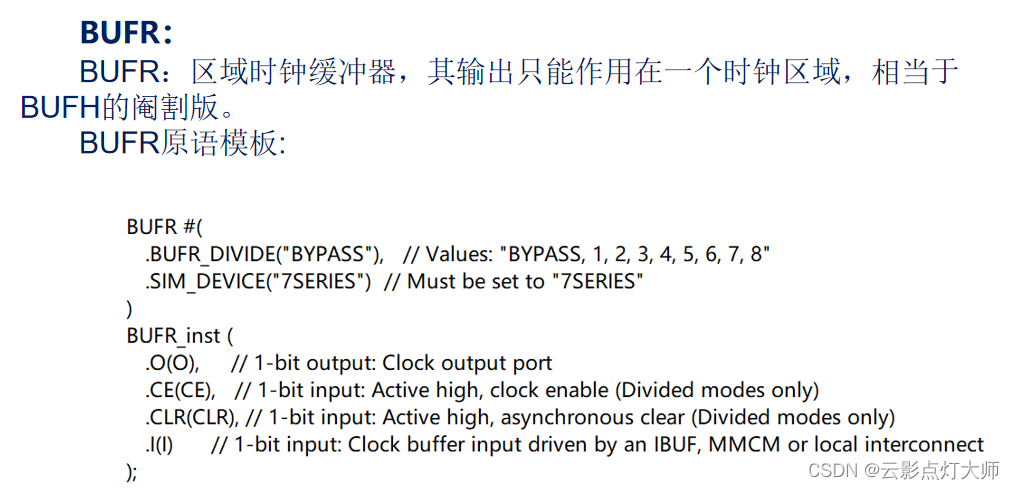

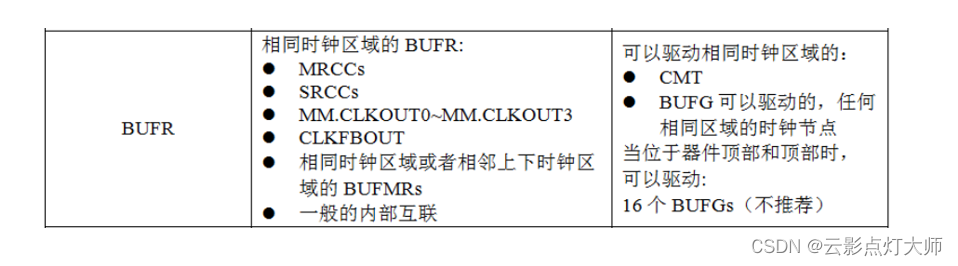

(3)BUFR

可以进行分频,就不用进入PLL了

输入输出

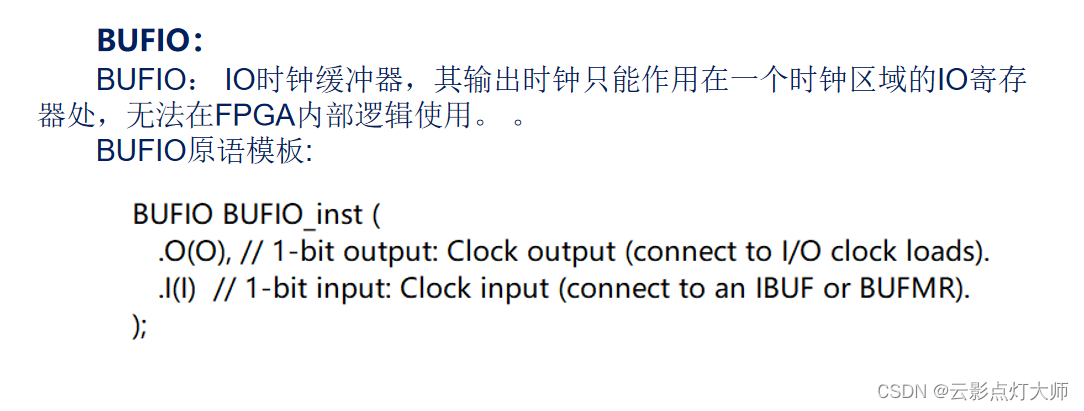

(4)BUFIO

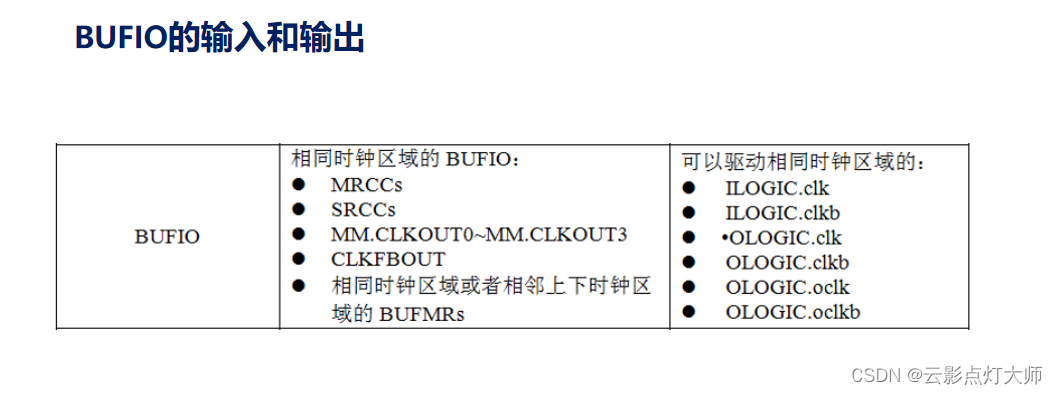

输入输出

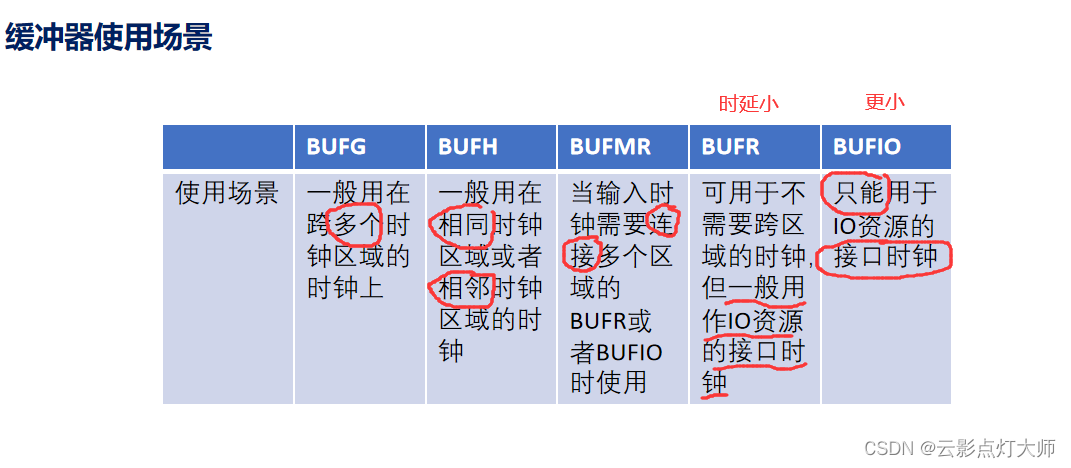

(5)使用场景

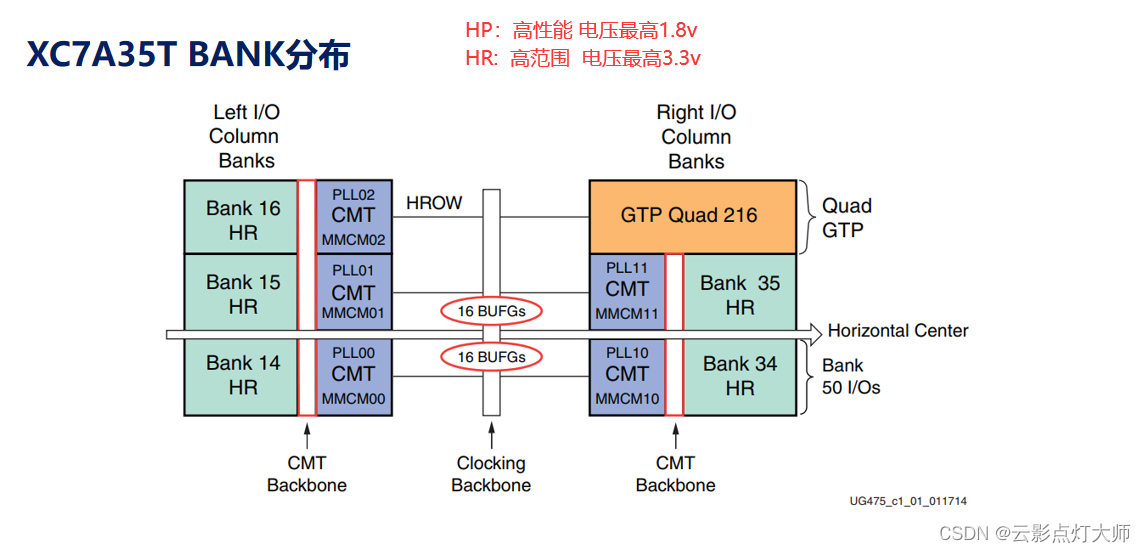

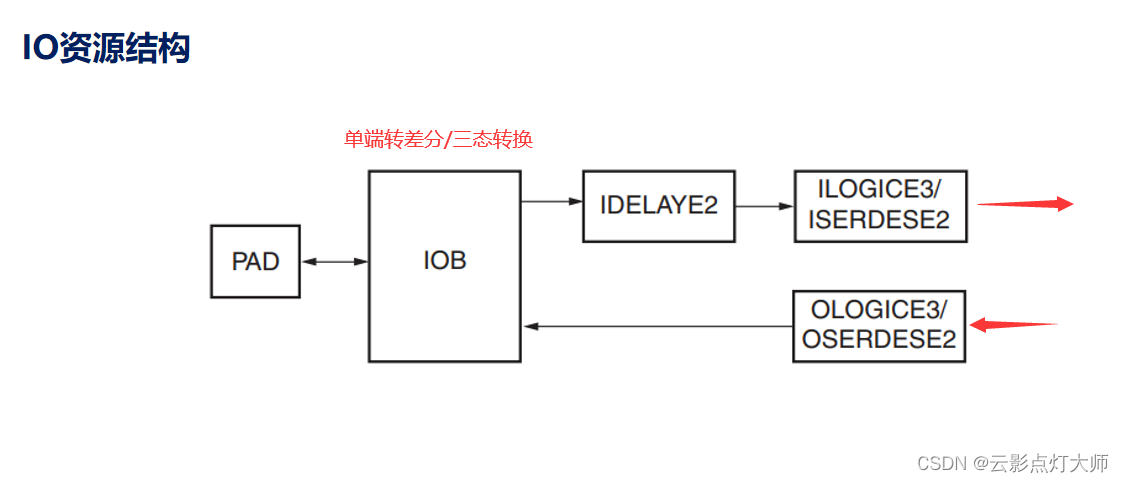

2.IO端口组件

HR是3 HP是2

(1)IDDR

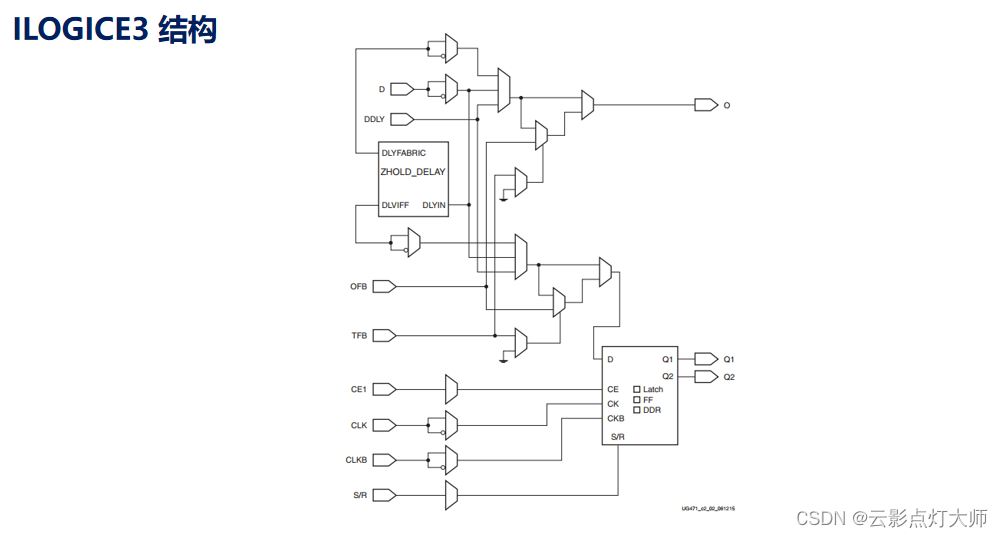

其中 ILOGICE3的结构

其中

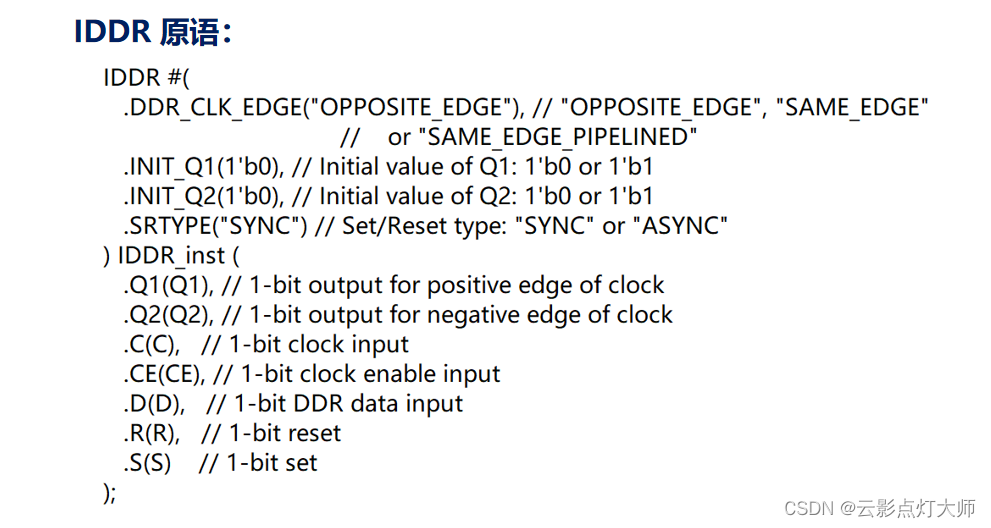

IDDR:输入数据的双沿采样,是ILOGIC块中专用的寄存器,用于实现输入数据双沿采样。

IDDR工作模式:

OPPOSITE_EDGE mode ;

SAME_EDGE mode ;

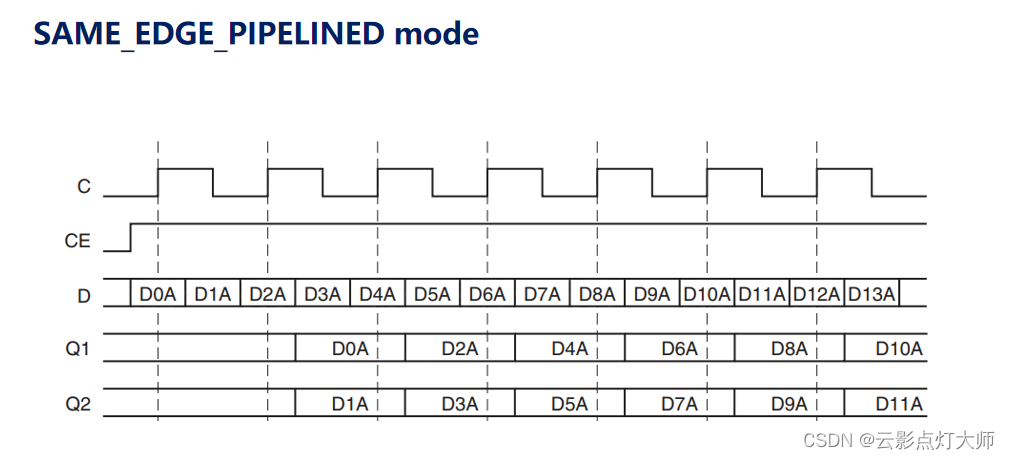

SAME_EDGE_PIPELINED mode;

常用的模式为 SAME_EDGE_PIPELINED mode

原语

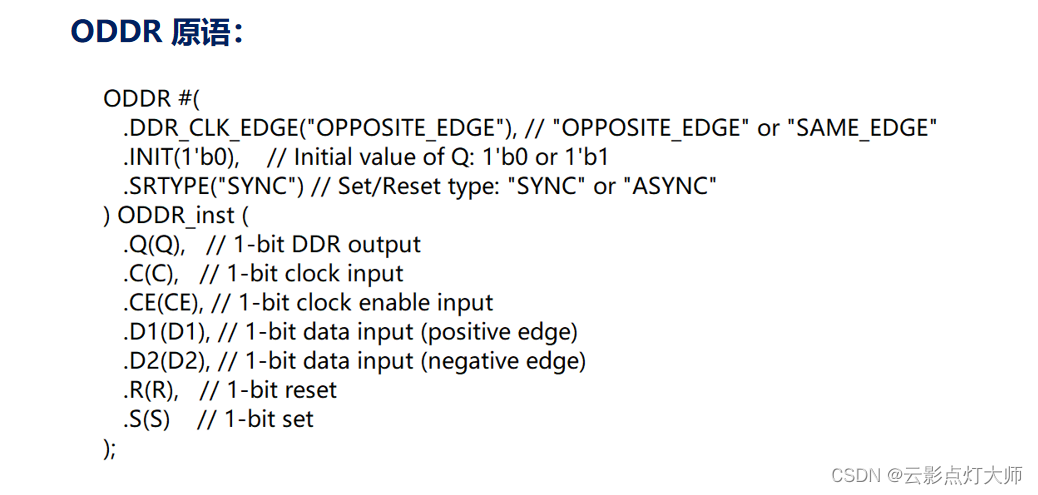

(2)ODDR

ODDR :输出数据的双沿采样,是OLOGIC块中专用的寄存器,用于实现输出数据双沿采样

ODDR工作模式:

OPPOSITE_EDGE mode ;

SAME_EDGE mode ;

常用 SAME_EDGE mode ;

原语

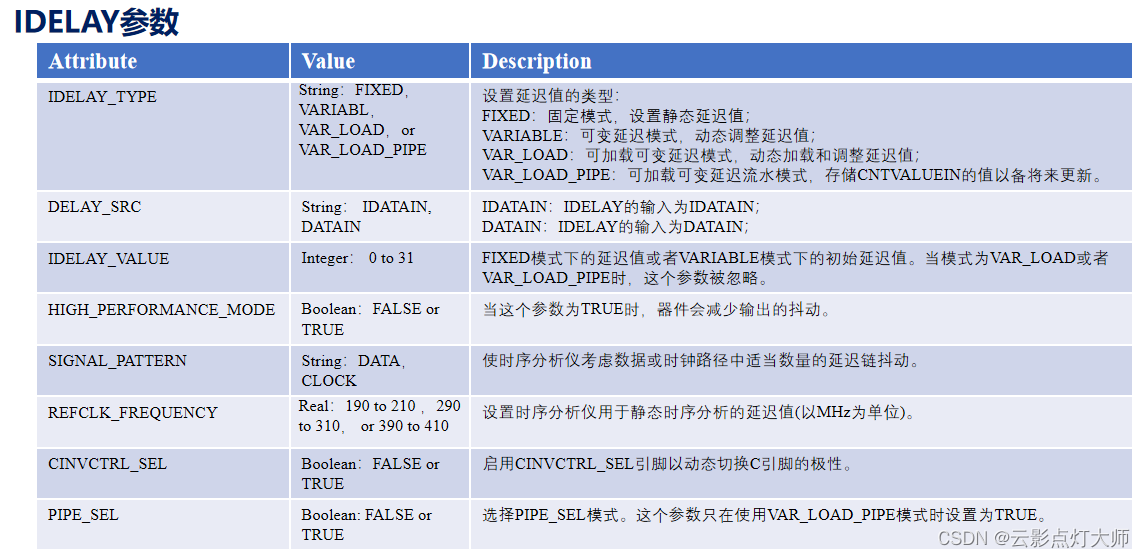

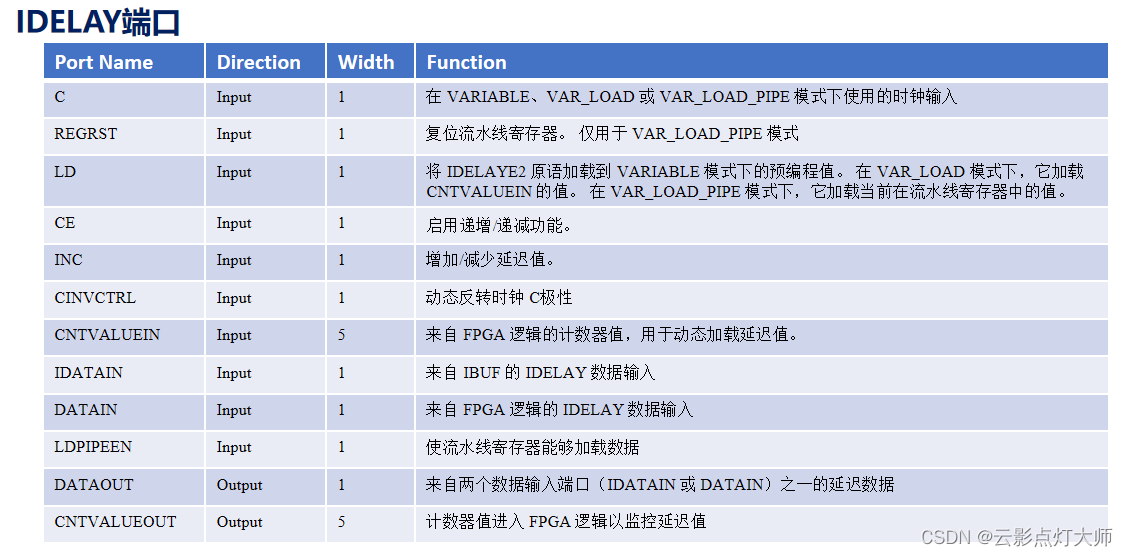

(3)IDELAY

9606

9606

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?