1.打开stateflow的五种方式方式:

(1)在maltab命令行里面输入:sf

(2)命令行输入:sflib

(3)命令行输入:sfnew -matlab

(4)命令行输入:sfnew -c 这是打开stateflow c语言编写的

(5)直接在simulink library 中直接打开stateflow

如上图,随便哪一种方式都可以。

2.在matlab/simulink中建立stateflow后

双击进入stateflow中,在空白处右键点击Properties进入进行相关设置,如Action Language是matlab语言可设置为C语言,更新方法等。

3.现在介绍stateflow建模

看下面两个模块,这个是虚线,是个并行关系,怎么设置呢?即在 空白处右键选择Decompostion中Parallel就出现虚线(注意:这里有1,2表示执行顺序,1表示优先执行)。选择Exclusive即为互相排斥关系,为实线,如下图:

想改变并行执行顺序怎么做呢?只需要在上面案例中state1上选中Execution order选择为2,另一个就会变成1,如下图:

动作类型(entry(en),during(du),exit(ex)

用于基于事件的时序逻辑的运算符

对于基于事件的时序逻辑,请使用下表所述的运算符。

基于事件的时序逻辑示例

以下示例说明了基于事件的时序逻辑在状态动作和转移中的使用。

| 运算符 | 用法 | 示例 | 说明 |

|---|---|---|---|

|

| 状态动作 (on after) |

| 从状态激活后开始 5 个时钟周期,每个 |

|

| 转移 |

| 仅在广播 |

|

| 状态动作 (on before) |

|

|

|

| 转移 |

| 仅在广播 |

|

| 状态动作 (on at) |

| 状态消息会在状态激活后的正好 10 个 |

|

| 转移 |

| 仅在广播 |

|

| 状态动作 (on every) |

| 状态激活后,每 5 个 |

|

| 状态动作 (during) |

| 此动作会对状态激活后的时钟时间进行计数并返回整数值。然后,该动作会为变量 |

基于事件的时序逻辑的表示法

可以使用以下两种表示法之一来表示基于事件的时序逻辑。

事件表示法

使用事件表示法定义仅依赖基础事件的状态动作或转移条件。

事件表示法采用以下语法:

tlo(n, E)[C]其中

-

tlo是一个布尔时序逻辑运算符(after、before、at或every) -

n是运算符的出现次数 -

E是运算符的基础事件 -

C是一个可选条件表达式

条件表示法

使用条件表示法定义依赖基础事件和非基础事件的转移条件。

条件表示法遵循以下语法:

E1[tlo(n, E2) && C]其中

-

E1是任意非基础事件 -

tlo是一个布尔时序逻辑运算符(after、before、at或every) -

n是运算符的出现次数 -

E2是运算符的基础事件 -

C是一个可选条件表达式

事件表示法和条件表示法示例

| 表示法 | 用法 | 示例 | 说明 |

|---|---|---|---|

| 事件 | 状态动作 (on after) |

|

|

| 事件 | 转移 |

| 状态激活 10 个 |

| 条件 | 转移 |

| 仅在广播 |

注意

在状态动作中必须使用事件表示法,因为状态动作的语法不支持使用条件表示法。

用于绝对时间时序逻辑的运算符

对于绝对时间时序逻辑,请使用下表中所述的运算符。

绝对时间时序逻辑示例

下面的示例说明了绝对时间时序逻辑在状态动作和转移中的运用。

| 运算符 | 用法 | 示例 | 说明 |

|---|---|---|---|

|

| 状态动作 (on after) |

| 自状态激活并执行 12.3 秒的仿真后, |

|

| 转移 |

| 自状态激活并执行 8 毫秒的仿真后,会发生转出关联状态的转移。 |

|

| 转移 |

| 自状态激活并执行 5 微秒的仿真后,会发生转出关联状态的转移。 |

|

| 转移 |

| 如果变量 |

|

| 状态动作 (exit) |

| 此动作对状态激活和反激活之间所经过的仿真时间进行计数并返回秒数。 |

4.怎样定义stateflow输入输出接口?这里给出三种方法

(1)通过窗口chart/Add Input & output,如下图:

(2)第二种方法通过工具栏中的Model Explorer

(3)直接点击编译,会报错弹出窗口,在弹出的窗口里面选择输入,输出,再次编译就不会报错。这里不给出图片,自己试一下即可知道。(这里别忘了加默认的初始状态)

4.讲了这么多,教大家一个实例

其实这个x==1条件可以看作家里总开关有电,switch_on表示控制灯的开关为开,light=1 表示灯亮。灯的变量设置如下:light为输出,switch_off为输入端口2,为下降沿,switch_on输入端口1,上升沿,x为输入,端口为1,event是为默认转移条件设置的,设置为输入3,设置为Either。是为了刚初始化时,状态为默认的off。

整体完成如上:当初始开始时,为off状态,为当x=1,触发从0到1,灯亮,输出为1,1到0灯灭,输出为0。

程序的下载地址:https://download.csdn.net/download/caokaifa/11437934

5.连接节点的应用

这个相当于if ..elseif ..else...这个没什么难的,直接搭建即可

6.stateflow回调函数调用

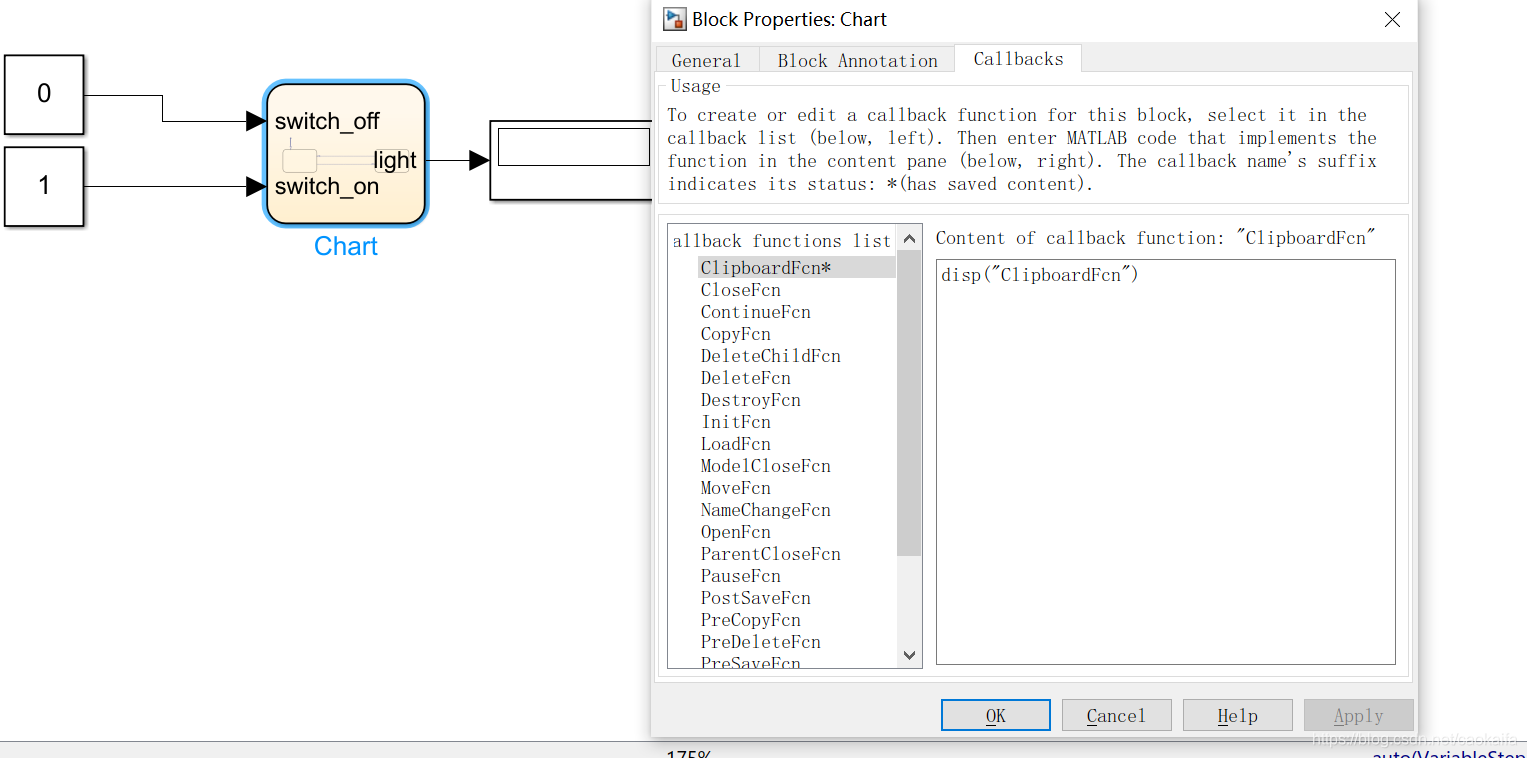

首先,随便搭建一个stateflow模块或用我上面搭建的stateflow例子都可以:我就搭建了一个如下图

然后右击stateflow模块,点击Properties如下图:

然后出现如下图:

然后点击Callbacks,然后点击ClipboardFcn,添加disp("ClipboardFcn")

这样,点击OK,保存就好了,现在看调用函数的效果。回到工程,右击点击剪切stateflow模块,如下图:

这时,matlab输入命令窗口出现开始设置的disp显示内容。

其他的调用函数按照上面操作即可。

注意:这里可能有的回调函数没有显示你的内容,可能是因为函数对disp有点bug,你可以随便定义i=9,运行看工作空间有没有就知道有没有执行。

7.stateflow 函数怎么调用matlab工作空间的变量

这里,通过ML即可获取工作空间的变量,搭一个stateflow如下:

这里的功能实现就是通过获取工作空间的变量x与y,其中state1在5s后切换到state2,state2在5s后切换到状态1,工作空间输入x=2,y=3;仿真结果如下:

这里就实现了stateflow调用工作空间的变量值。

这里要注意了:完成上面的调用需要设置东西,否则会报错误,点击Properties

进入以后把Action Language选择C语言即可编译。

同时也可调用matlab 中函数,如下图:

在matlab中定义一个mm.m文件的函数,输入y=3

结果如下:

2099

2099

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?