物理优化约束

Vivado Design Suite在物理优化过程中尊重DONT_TOUCH特性。它不在具有这些属性的网络或小区上执行物理优化。要加快网络选择过程中,具有DONT_TOUCH属性的网络经过预过滤,不被考虑用于物理优化。此外,还遵守Pblock分配,以便复制逻辑继承原始逻辑的Pblock赋值。定时异常也从复制从原始细胞到复制细胞。有关更多信息,请参阅《Vivado Design Suite用户指南》中的“合成属性”一节:合成(UG901)。DONT_TOUCH属性通常放置在叶细胞上,以防止它们优化。分层单元格上的DONT_TOUCH保留了单元格边界,但进行了优化仍然可以发生在细胞内。

工具会自动将值为TRUE的DONT_TOUCH属性添加到具有值为TRUE的MARK_DEBUG属性。这样做是为了在整个实现流程,以便可以在任何设计阶段对其进行探索。这是推荐的MARK_DEBUG的使用。但是,DONT_TOUCH限制性太强,阻止了复制和重定时等优化,导致关闭时机困难。在这些情况下,DONT_TOUCH可以设置为FALSE值,而保持MARK_DEBUG为真。删除DONT_TOUCH属性的结果是DEBUG的网络可以被优化掉并且不再被探测。如果MARK_DEBUGnet被复制,只有原始的net保留MARK_DEBUG,而不是被复制的net。

物理优化报告

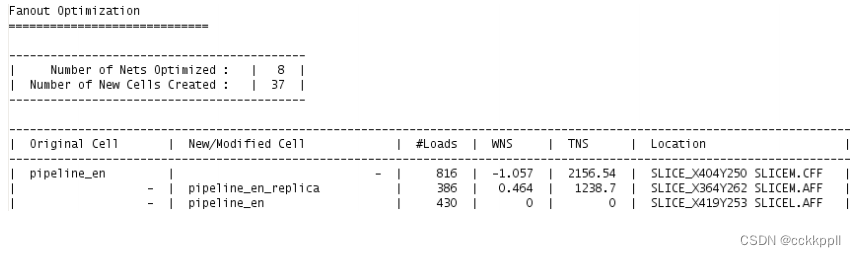

Tcl报告命令report_phys_opt提供了执行的每个优化的详细信息通过phys_opt_design在非常精细的细节级别上实现。它必须在与相同的Vivado会话中运行phys_opt_design,而优化历史存在于存储器中。因此,如果需要报告,建议包括report_phys_opt命令在最后一个phys_ opt_design命令之后的Tcl脚本中。这些报告仅可用于放置后的phys_opt_design优化。这个报告不是累积的。每个phys_pt运行都有一个不同的phys_pt报告,仅说明在phys_opt_design的特定运行期间所做的更改。以下报告示例显示了涉及寄存器的扇出优化的第一个条目命名为pipeline_en。报告中显示了以下详细信息:

1.原始驱动器pipeline_en驱动816负载和包含该高扇出网络的路径WNS为-1.057 ns的故障定时。

2.复制驱动程序pipeline_en以创建一个新的单元pipeline_en_replica。

3.816个负载在pipeline_en_replica和原始负载之间分配,前者占用386个负载驱动程序pipeline_en,它承担剩余的430个负载。

4.在复制和放置pipeline_en_replica之后,pipeline_en _replica路径的WNS是+0.464ns,并且pipeline_en路径的WNS减少到零。

5.改变了原始驱动程序pipeline_en的位置,以改进基于其减少的一组负载的位置。

交互式物理优化

从2015.3版本开始,物理优化具有“回放”功能使用交互式Tcl命令iphys_opt_design进行优化。iphys_opt_design命令描述特定的优化事件,例如关键单元的复制或者从块RAM中提取一组寄存器。该命令包括所有信息重新创建网表和优化所需的位置更改所必需的发生交互式物理优化可以通过两种方式使用:

本文介绍了VivadoDesignSuite在物理优化过程中的特性,如DONT_TOUCH和MARK_DEBUG的作用,以及如何使用iphys_opt_design进行交互式优化,包括复制、重定时和报告优化详情。着重讲解了如何通过交互式Tcl命令控制物理优化并重复设计更改的过程。

本文介绍了VivadoDesignSuite在物理优化过程中的特性,如DONT_TOUCH和MARK_DEBUG的作用,以及如何使用iphys_opt_design进行交互式优化,包括复制、重定时和报告优化详情。着重讲解了如何通过交互式Tcl命令控制物理优化并重复设计更改的过程。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1291

1291

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?