目录

在 FPGA(现场可编程门阵列)综合过程中,信号的扇出(Fanout)是一个关键的概念。扇出指的是一个信号驱动其他模块或寄存器的数量。当扇出数量过高(即出现 High Fanout 情况)时,会对 FPGA 设计的性能、时序和资源利用等方面产生诸多不利影响。因此,深入理解 High Fanout 问题并掌握有效的降低策略对于高质量的 FPGA 设计至关重要。

1.Fanout 的定义与计算

在FPGA设计中,扇出是指一个信号输出端所连接的其他逻辑单元(如寄存器、组合逻辑块等)的输入端的数量。例如,一个驱动信号连接到 5 个其他模块的输入,那么这个信号的扇出数为 5。扇出数可以通过综合工具的报告文件或者在设计的原理图中直观地统计得到。

如果设计采用了多层的层次化结构,高层模块中的信号可能会因为需要驱动多个底层模块而导致高扇出。例如,在一个包含多个子模块的复杂处理器设计中,全局控制信号(如复位信号、时钟使能信号等)可能需要分发到各个子模块,从而产生较高的扇出。

当一个模块被多次实例化并且共享某些输入信号时,这些信号的扇出会随着实例化次数的增加而增大。比如一个通用的算术逻辑单元(ALU)模块被多个数据处理单元复用,其操作码输入信号的扇出就会较高。

如全局时钟信号(clk)和全局复位信号(rst),由于需要控制整个 FPGA 芯片内的多个模块的同步和初始化,往往具有很高的扇出。这些信号在整个设计的每个时钟周期或复位操作时都要被广泛使用。

在数据传输密集的设计中,数据总线信号(如地址总线、数据总线)的扇出也可能较高。例如,在一个具有多个存储单元和数据处理单元的片上系统(SoC)设计中,地址总线信号需要连接到所有的存储单元和相关的控制逻辑,导致扇出增加。

2.High Fanout问题对FPGA设计的影响

FPGA 内部的布线资源是有限的。高扇出信号需要更多的布线通道来连接到众多的负载单元。当大量的布线资源被高扇出信号占用时,其他信号的布线可能会受到限制,导致布线拥塞。例如,在一个复杂的逻辑设计中,如果多个高扇出信号集中在某个区域,该区域的布线资源可能会耗尽,使得一些局部的信号连接无法按照最优的路径进行布线,增加了布线长度和信号延迟。

为了能够驱动高扇出的负载,综合工具可能会采用更强大的驱动单元(如具有更高驱动能力的缓冲器或反相器)。这些驱动单元通常会占用更多的逻辑资源。而且,由于高扇出信号的延迟问题,可能需要在设计中添加额外的时序调整逻辑(如延迟单元、寄存器等)来满足时序要求,进一步浪费了逻辑资源。

3.功耗问题

高扇出信号在驱动多个负载时,由于负载电容较大,信号的翻转会导致更多的充放电电流。根据动态功耗公式:

(其中P为动态功耗,C为负载电容,V为电源电压,f为信号翻转频率),负载电容的增加会直接导致动态功耗的增加。例如,在一个频繁进行数据传输的系统中,高扇出的数据总线信号的动态功耗可能会成为整个系统功耗的主要部分。

为了驱动高扇出负载而采用的具有高驱动能力的逻辑单元,其本身可能具有较高的静态功耗。虽然 FPGA 中的静态功耗相对动态功耗较小,但在一些低功耗设计要求下或者大规模 FPGA 设计中,高扇出信号导致的静态功耗增加也不容忽视。

4.降低High Fanout的策略

信号复制是指将高扇出信号复制多个副本,每个副本驱动一部分负载。这样可以减小每个信号副本的扇出,从而降低信号延迟和负载电容。例如,对于一个具有高扇出的全局控制信号,将其复制为几个副本,每个副本分别驱动不同区域的模块。

适用于那些在功能上允许局部控制的信号。比如在一个具有多个功能模块的 FPGA 设计中,一个全局使能信号可以被复制为多个模块级别的使能信号,每个副本仅控制一个或几个相关的模块。这样可以有效地降低信号的扇出,同时不会影响设计的功能。

分区是将整个 FPGA 设计按照功能、位置或其他标准划分为多个区域,然后将高扇出信号在不同区域进行分发。例如,可以根据模块的层次结构或者物理位置将设计划分为几个部分,对于高扇出的信号,在每个分区内设置一个中继节点来接收和转发信号,这样可以将信号的扇出分散到各个分区。

考虑一个包含多个处理器核和周边设备的 FPGA SoC 设计。全局时钟信号和复位信号的扇出很高。可以将设计划分为几个区域,每个区域包含一个处理器核及其相关的存储单元和接口设备。然后在每个区域设置一个时钟缓冲器和复位同步器,用于接收和转发全局时钟信号和复位信号。这样,原本高扇出的全局信号在每个区域内的扇出就会大大降低,同时也有利于减少区域间的时钟偏移和信号延迟。

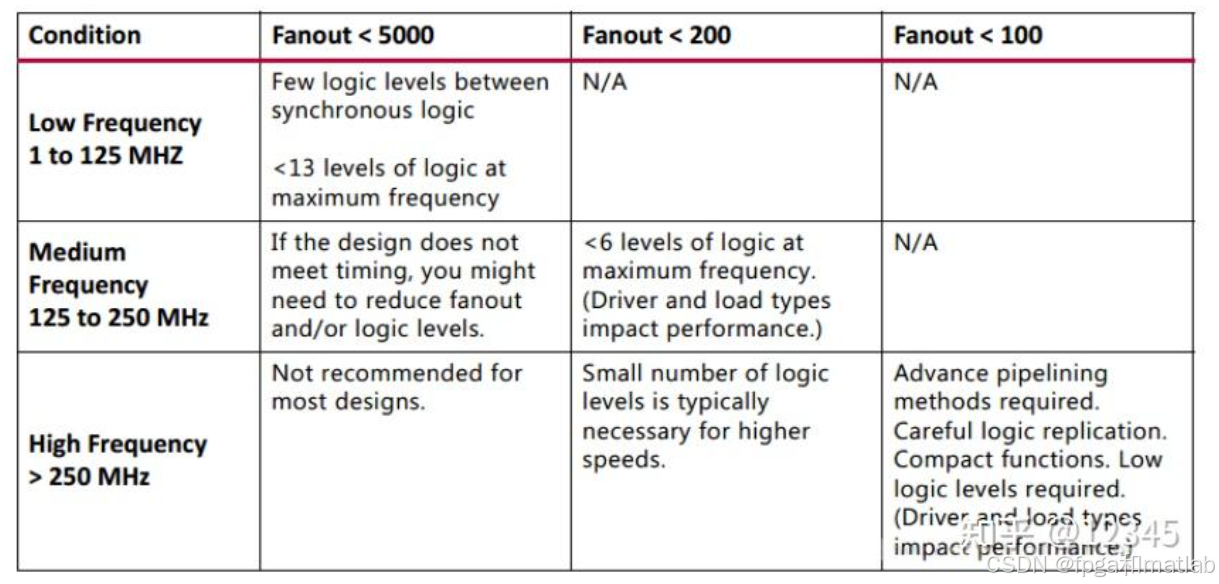

其中,Xilinx官方对扇出设计的建议如下:

3318

3318

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?