PCB的挖空 在射频的Layout中

是一门学问

在[1]当中提到 射频走线 在维持50欧姆前提下

下方挖空 寄生电容未必变小

因为线宽也跟着变宽

然而组件的焊盘 大小是固定的

因此挖空只会让寄生电容变小

这个论点是正确 但并非只考虑寄生电容

还要考虑阻抗 因为由下方公式知道

寄生电容变小 阻抗就变大

因此首要考虑 是焊盘大小

考虑基准为射频走线的线宽

如果焊盘大小 远大于50欧姆射频走线

那表示其阻抗必远小于50欧姆

那就必须挖空 在减少寄生电容之余 进一步提升阻抗 使其更靠近50欧姆

当然要挖几层 这必须由PCB迭构来决定

但如果焊盘大小 等于50欧姆射频走线

基本上我们可以判断 其阻抗约莫会在50欧姆附近

这时如果挖空 反而会让阻抗高于50欧姆

当然若是BGA 更不可能挖空

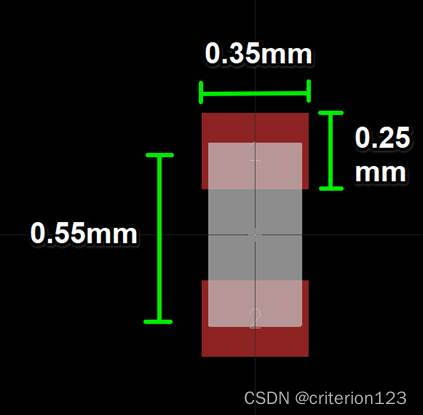

或是另一种判断基准 0201的焊盘大小

一般而言 因为0201的焊盘已经足够小 寄生电容不大

故几乎都不挖空

因此 倘若组件的焊盘 跟0201焊盘差不多

那就没有挖空的必要

参考文献

7099

7099

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?