随着chiplet的兴起,Die2Die的高速互联越来越重要,相比于传统的C2C(chip2chip)的互联,D2D的片间距离很近(10mm量级),且这些小的chip(裸片)最终形成一个封装【多芯片模块(MCM)】。所以D2D的互联信道短,干扰和损耗小,就出现了串口和并口两种互联总线。而C2C的高速互联都是高速串口。

1.C2C互联简介

常见的soc上板级互联高速接口用的PCIE和XGMAC(1G MAC /10GMAC)。特别是XGMAC在车载领域用的较多,用于不同控制域之间的芯片互联,加上以太网的协议可以支持灵活的多个芯片互联。

FPGA上有:

Serial RapidIO(SRIO):由Motorola和Mercury等公司率先倡导的一种高性能、 低引脚数、 基于数据包交换的互连体系结构,是为满足和未来高性能嵌入式系统需求而设计的一种开放式互连技术标准。RapidIO主要应用于嵌入式系统内部互连,支持芯片到芯片、板到板间的通讯,可作为嵌入式设备的背板(Backplane)连接。

jgliu的博客推荐 rapidIO/DDR/SPI/I2C_cy413026的博客-CSDN博客

Aurora:是Xilinx FPGA常用的一种可裁剪的、轻量级的、链路层点对点的针对FPGA间的高速数据传输的串行传输通信协议。目前支持的传输速度为0.5~13.1Gbps,还支持通道绑定实现更高的数据传输速度。

在FPGA中经常和AXI总线+axi chip2chip bridge+Aurora组成多个chip间的通信

Aurora 和 ChipToChip IP(二)_Y__Yshans的博客-CSDN博客

2.D2D互联简介

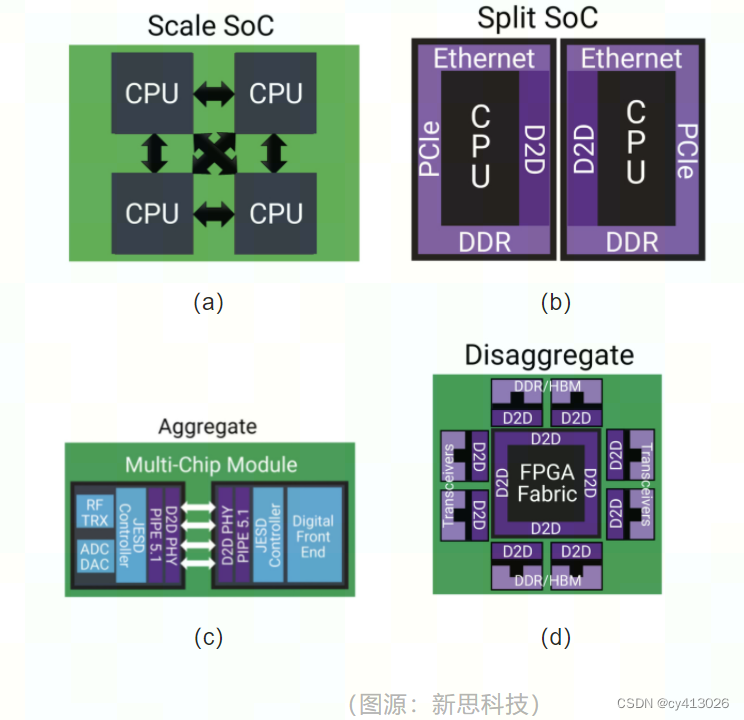

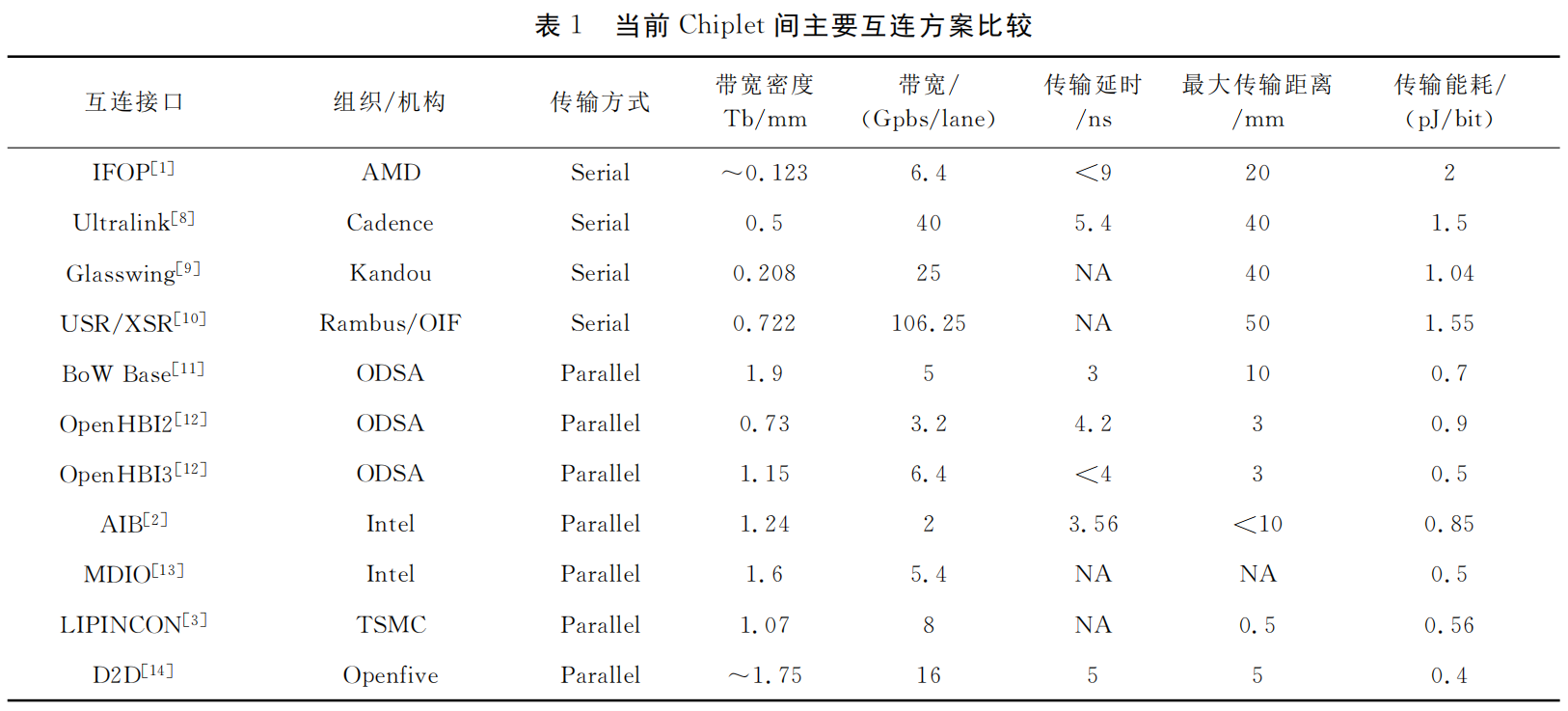

前面已经说了 D2D现在有并行和串行两种互联方案,业界巨头各有各的互联接口,但是自2022年Universal Chiplet Interconnect Express UCIE的出现【Intel、AMD、ARM、高通、三星、台积电、日月光、Google Cloud、Meta和微软等公司联合推出的Die-to-Die互连标准】,有望统一D2D的接口标准。

傻白探索Chiplet,互连技术研究现状_cy413026的博客-CSDN博客

| 标准 | 数据速率 [Gbps] | Bump 区[um] | 功率效率 [pJ/bit] | 边缘密度 [Tbps/mm] | 面积密度 [Tbps/mm2] | FOM-1 [Tbps/mm / pJ/bit] 越大越好 | FOM-2 [pJ/bit / mm] 越小越好 |

| AIB 2.0 | 6.4 | 55 | 0.5 | 1.64 | - | 3.28 | 0.1 |

| OpenHBI 1.0 | 8 | 40 | 0.4 | 2.29 | 2.04 | 5.71 | 0.1 |

| OpenHBI 2.0 | 12~16 | 40 | 0.5 | 3.34 | 3.06 | 6.86 | 0.06 |

| BoW – 基本 | 8 | 40 | 0.5 | 1.78 | 1.07 | 3.56 | 0.1 |

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?