本片博客主要介绍一下RS锁存器(RS latch),D锁存器(D latch)和D触发器(D flip flop)各自的电路原理和优缺点以及演变历史。

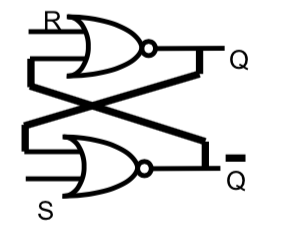

RS锁存器(RS latch)

电路图:

真值表:

| R | S | Q |

|---|---|---|

| 0 | 0 | Q |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 1 | X |

注意到

- 当R=1时,输出为0,故R又称为直接置“0”端,或“复位”端(reset)

- 当S=1时,输出也为1,故S又称为直接置“1”端,或“置位”端

- 当R=S=0时,输出保持不变(很重要的特征!保证了RS同时为0(断电)后,电路输出能够保持不变)

- 注意!!!RS不能同时为1

- 如果RS同时为1,那么根据电路图可以推导出两个输出全为0,有人可能会说这有什么大不了,但是接下去当RS同时变为0的时候,问题来了!!!

- 由于RS不可能同时变为0(电路时延不可能完全相同),那么就存在先后问题,就会给电路带来不确定性!因为我们不知道是谁先变成0,就更不知道输出会变成什么样!

D锁存器(D latch)

电路图:

为了解决RS锁存器带来的问题(RS不能同时为1),在此基础上,添加两个与门和一个非门,即可避免这种情况。升级版电路名字就叫D锁存器。

但是D锁存器同样存在它的问题,那就是无法去除输入的毛刺(换句话说,对毛刺很敏感)。可以看到当E端为0的时候,R端也会恒为0,S端则等于D端输入,亦即是此时输出直接等于输入。所以在E=0的时候,输出完全跟随输入(哪怕输入存在毛刺/抖动,这在电路中十分常见!!!)。为了进一步的改进,人们在此基础上又提出了D触发器。

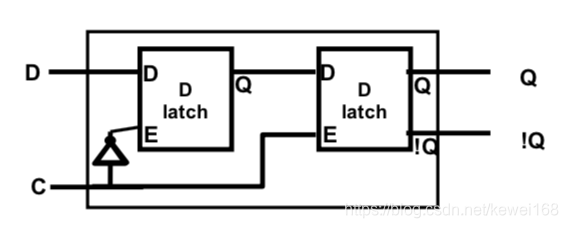

D触发器(D flip flop)

电路图:

通过两个D锁存器级联,并加入一个非门,就形成了D触发器。通过非门,使得两个D锁存器的时钟存在一个180°的相位差(亦即是相差半个时钟周期),从而实现,只在时钟上升沿的时候读取输入并输出,所以其他时候输入的变化不会传导到输出端,去除了输入可能存在的毛刺,得到了稳定的输出。

4272

4272

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?