1. 前言

FPGA开发中经常用到AXI总线协议,之前一直不知道具体过程,花了一天时间认真学习了一下,分享给大家。

2. 参考文章

建议结合博客和官方文档学习:

3. 实战demo

3.1 什么是AXI总线?

AXI 作为 ARM AMBA 微控制器总线的一部分,第一次出现在AMBA 3.0中。后面AMBA 4.0发布,AXI4出现了。

AXI 4总线和别的总线一样,都用来传输bits信息(包含了数据或者地址)。AXI4总线有三种类型,分别是

- AXI4

- AXI4-Lite

- AXI4-Stream

AXI4 是一种高性能memory-mapped总线,AXI4-Lite是一只简单的、低通量的memory-mapped 总线,而 AXI4-Stream 可以传输高速数据流。从字面意思去理解,AXI4-Lite是AXI4的轻量版。这里保留了memory-mapped的写法,主要是为了与AXI4-Stream区分开。

memory-mapped 可以这样去理解,假设有master A , 和 slave B, A与B通过AXI4或者AXI4-Lite连接通讯,A可以把B这个外设看作A上的某个地址。当A向B传输数据时,就等同于A向这个地址传输数据。

AXI4-Stream与AXI4、AXI4-Lite不同, 它不需要地址通道。

3.2 AXI4如何读写

对于AXI4来说一次正常的读操作和写操作如下图所示:

读操作:

写操作:

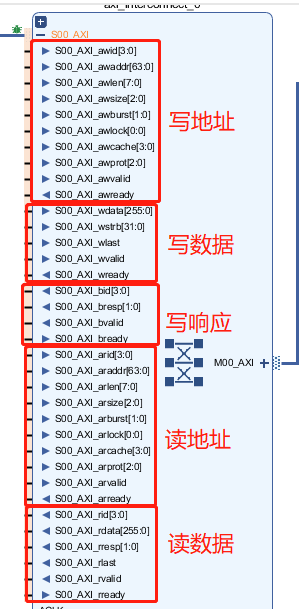

AXI总结端口名称和输入输出方向:

4.1 学习工程搭建

-

Basic中的interface Type 设置为AXI4

-

等综合完成Open IP Exanple Design

-

点击RTL ANALYSIS 发现example的实际结构就是一个BMG_STIM_GEN_INST对RAM进行读写操作

-

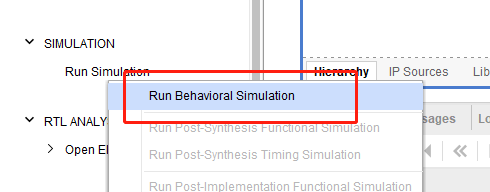

打开行为仿真

-

选择bmg0, 把右边的端口全部添加进Wave Window

-

最好选择仿真时间4us

5. 仿真结果解读

5.1 写操作

写操作截图:

5.1.1 写地址

如图可知

ID:1; //ID=1;

Write_addr=0x0000_0000; //写地址=0x0000_0000

len=0 //数据长度=s_axi_awlen+1=1;

size=2 //数据大小=s_axi_awsize^2=4Byte=32bit;

burst模式=1; //INCR:增量突发,传输过程中,地址递增。增加量取决AxSIZE的值。

awvaild下降沿 //从1变0时,主机发数据

5.1.2 写数据

Write_data=0x0a080604; // 符合size=2,数据为32位

wlast下降沿 //标识发送数据完成

wvaild下降沿 //高时表示数据总线数据有效

5.1.3 写回应

ID=1; //ID=1

bresp=0; //resp=0,常0表示ok

bvaild=0; //表示回应通道正常

bready=1; //一个周期表示数据写完成

5.2 读操作

5.2.1 读地址

ID=1; //ID=1;

read_addr=0x0000_0000; //读地址=0x0000_0000;

len=0; //长度=len+1

size=2; //大小等于32位

arvalid=1 //

arready下降沿 //

5.2.2 读数据

ID=1; //ID=1;

read_data=0x0a080604; //读到数据=0a080604;

resp=0; //回应常0

rlast=1; //表示最后一个数据

rvaild=1; //从机准备好

rready=1; //主机读数据

6. 截图

1166

1166

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?