例1.

宽度12,深度128,单时钟,normal模式

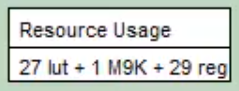

- 左下角是生成FIFO所需要的资源,注意实际硬件的限制。

M9K是硬件的嵌入式RAM,用于FIFO的RAM存储单元即使未用尽,也不能再用于其他模块,等于就是闲置了。比如一个开发板只有46个RAM,每个RAM存储单元512。使用了46个深度为4的FIFO,一个FIFO就占了一个M9K,所以硬件的RAM资源被用完,但是flow summary里的total memory bits使用率只有4/512=0.7%

- almost full的用处

在逻辑的控制中,由于寄存器的延时,可能根据full信号来控制来不及,这时就可根据almost full来提前控制。 - 读模式

normal,rdreq=1两拍之后,数据才有效(???);show-ahead,rdreq和数据同时有效。

仿真观察时序

观察各信号的时序。方法:ip生成以后有fifo.qip置为顶层,然后直接新建fifo_tb.v编写测试文件,然后在仿真设置里添加测试文件。

`timescale 1 ps / 1 ps

module fifo_tb();

reg clock;

reg [7:0] data;

reg rdreq;

reg sclr;

reg wrreq;

wire almost_empty;

wire almost_full;

wire empty;

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

822

822

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?