创建工程

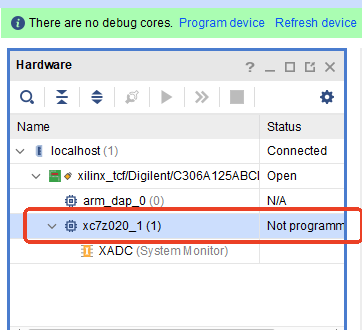

1)新建一个项目,芯片型号选择

XA7Z020 (直接选择xc7z020CLG400-1,因为系统识别到的是xc7z020-1)

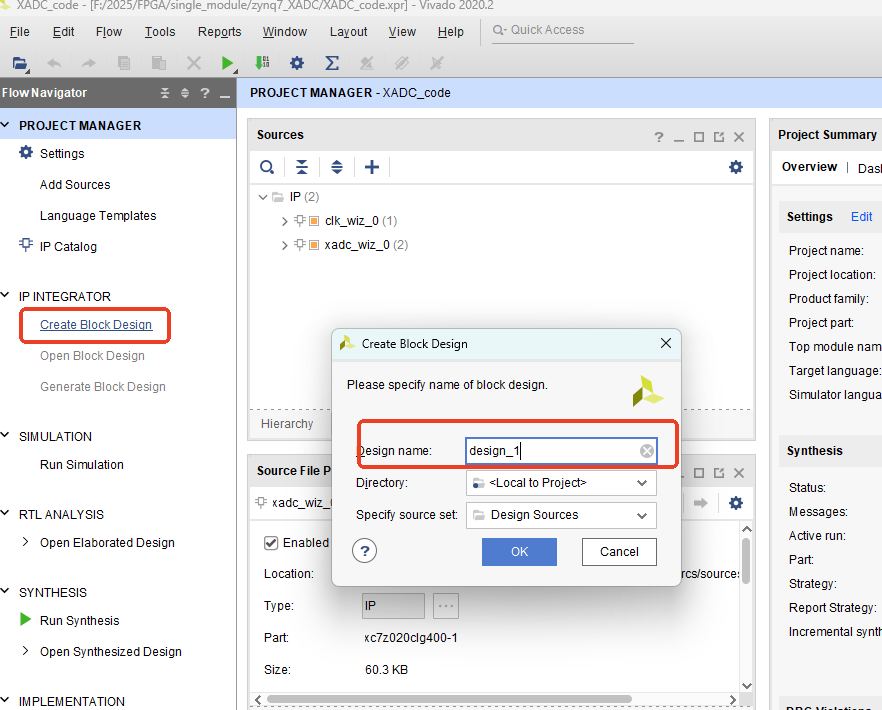

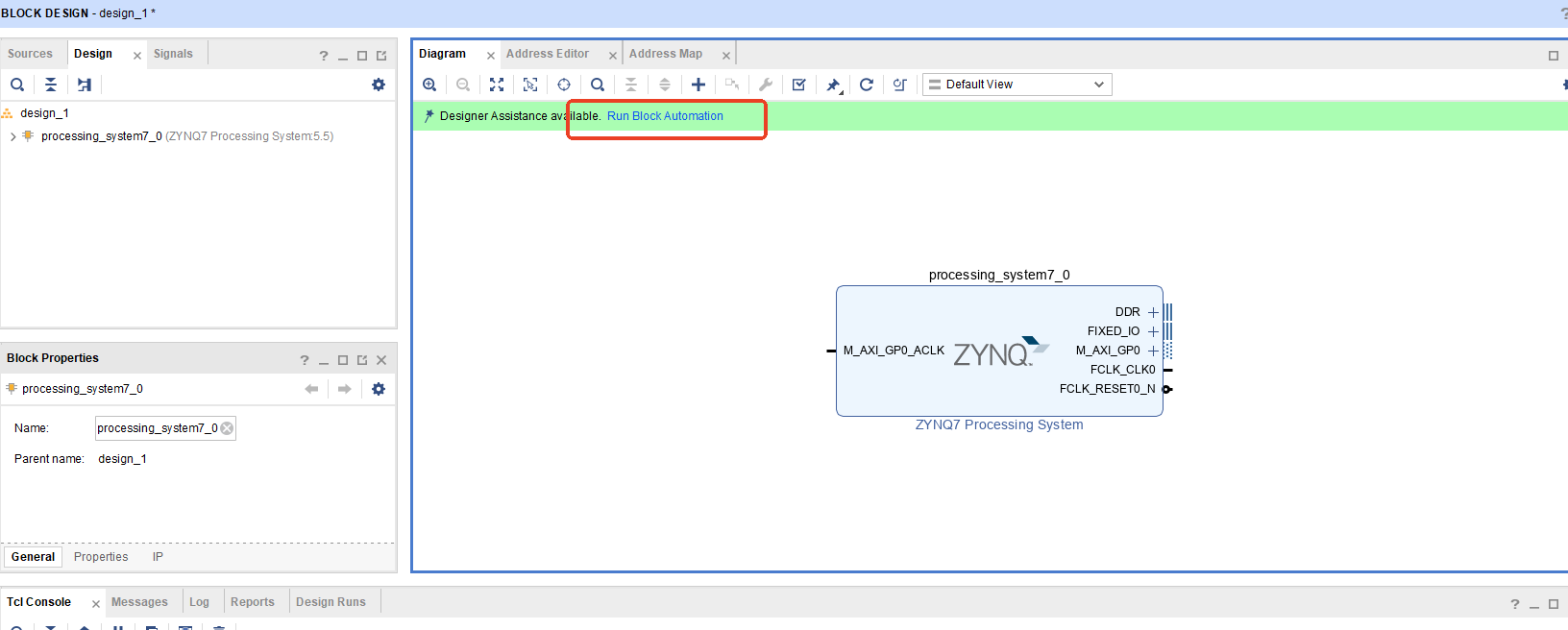

2) 创建一个BLOCK设计

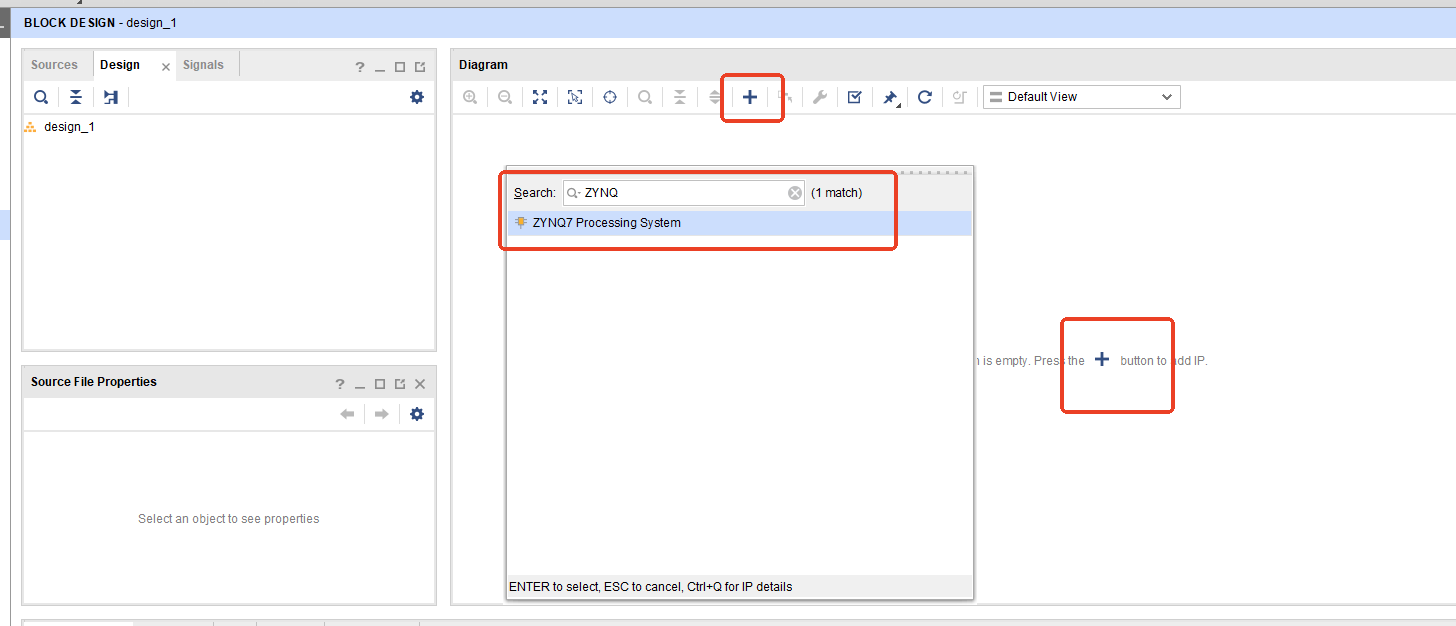

2)在右侧的窗口里 ,点击加号,在选择框里搜索ZYNQ,并找到ZYNQ7 PROCESSING SYSTEM ,双击并打开

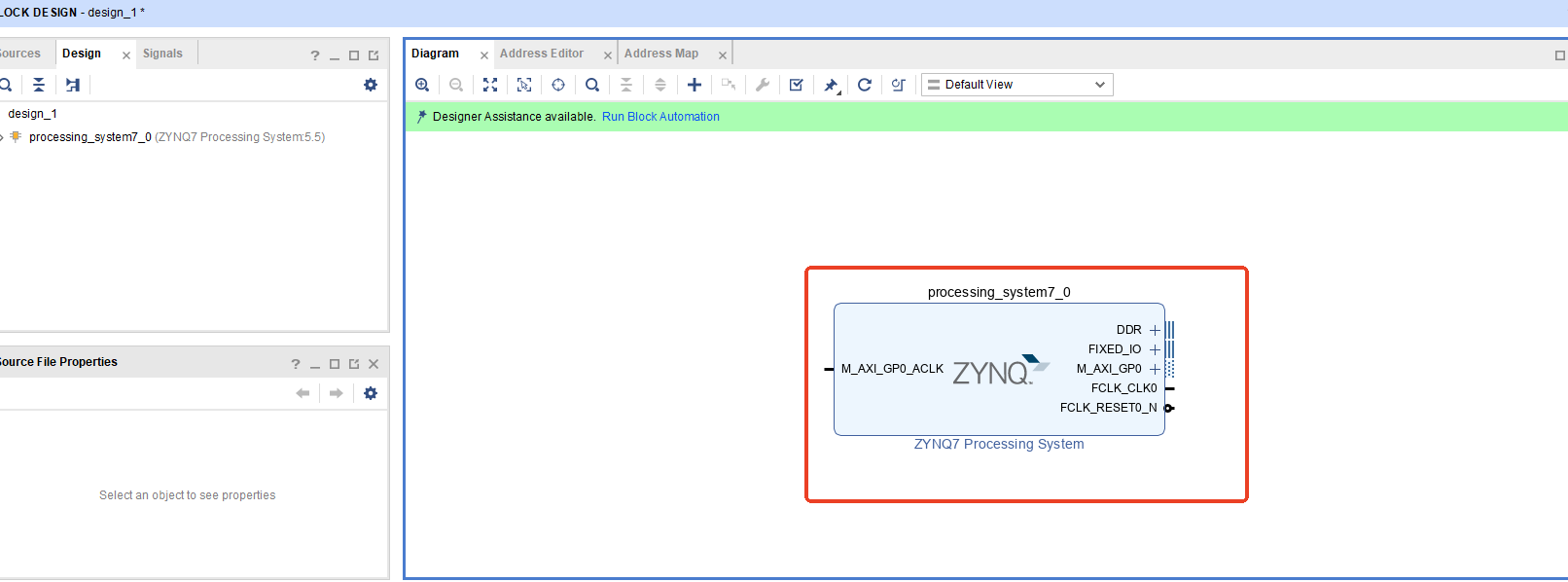

3)软件自动生成了一个 zynq的block 如下图所示,接下来要做一些相应的设置,双击下图中的ZYNQ核

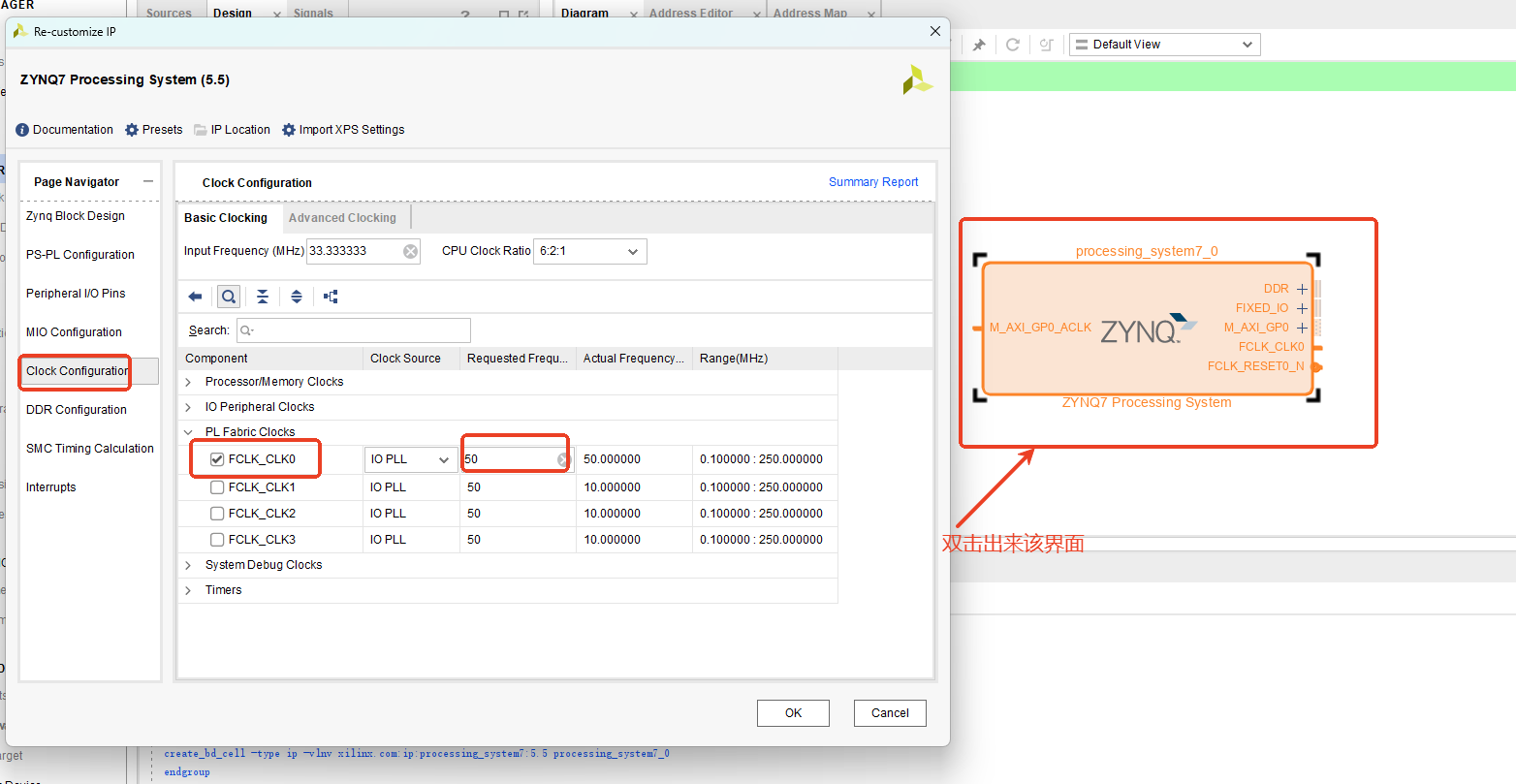

4) 在ZYNQ中设置时钟功能 :

找到 设置项目中的 Clock Configuration 选项, 在PL Fabric Clocks 设置自己需要的时钟频率,这里一共有4种频率可以设置 类似于我们的PLL功能。这里我们设置100M时钟

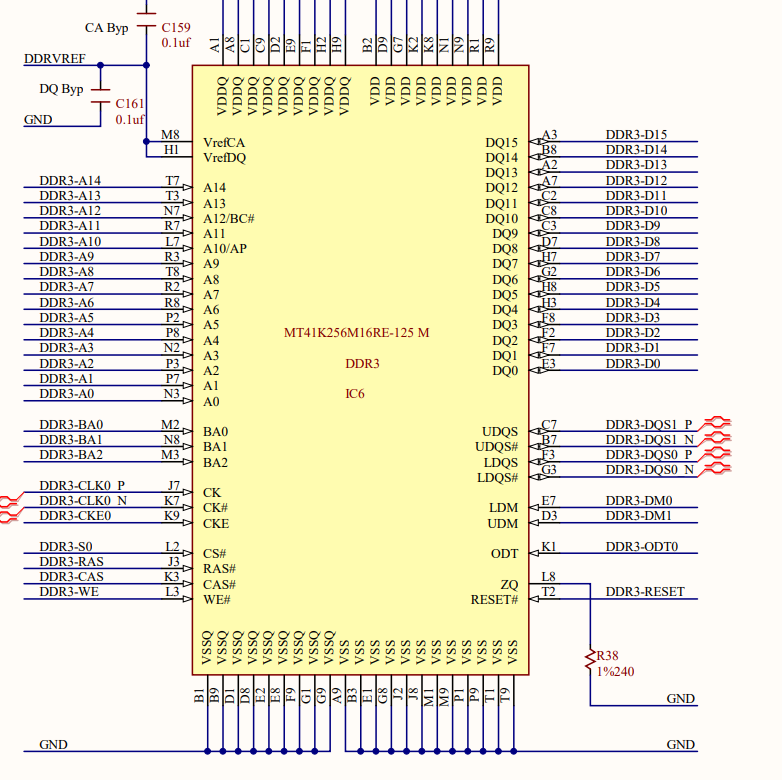

5) 在zynq中设置DDR功能 :

依次在弹窗里找到DDR Configuration→DDR Controller Configuration→DDR3,在Memory Part下拉菜单中根据自己板子上的DDR来选择相应的DDR3,本实验所用到型号:MT41K256M16RE-125,数据位宽选择16bit 最后点击“OK”,如下图所示。

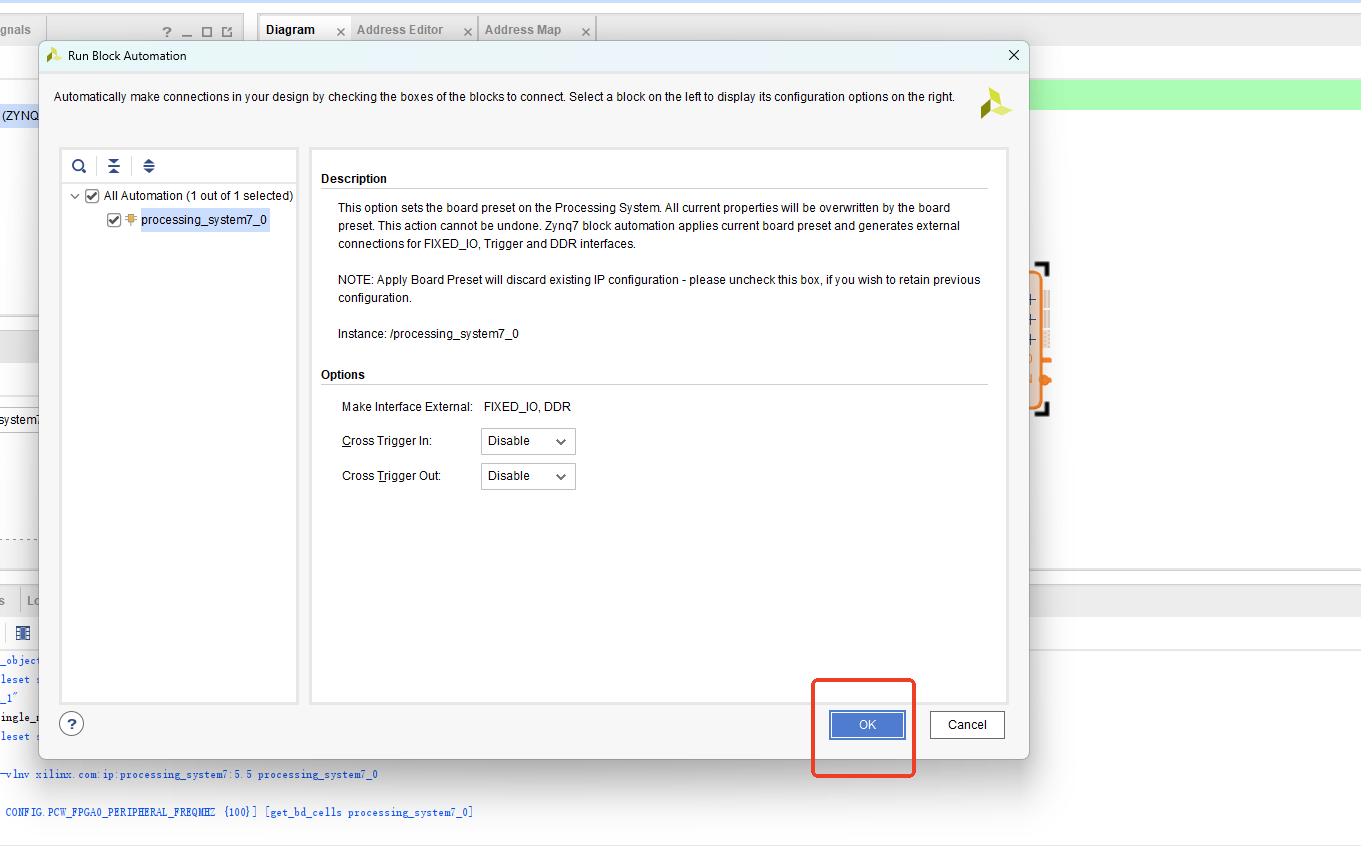

4)完成上述操作后, 点击“Run Block Automation”如下图所示

在弹出的选项中保持默认,点击“OK”,即可完成对ZYNQ7 Processing System的配置,得到如下所示

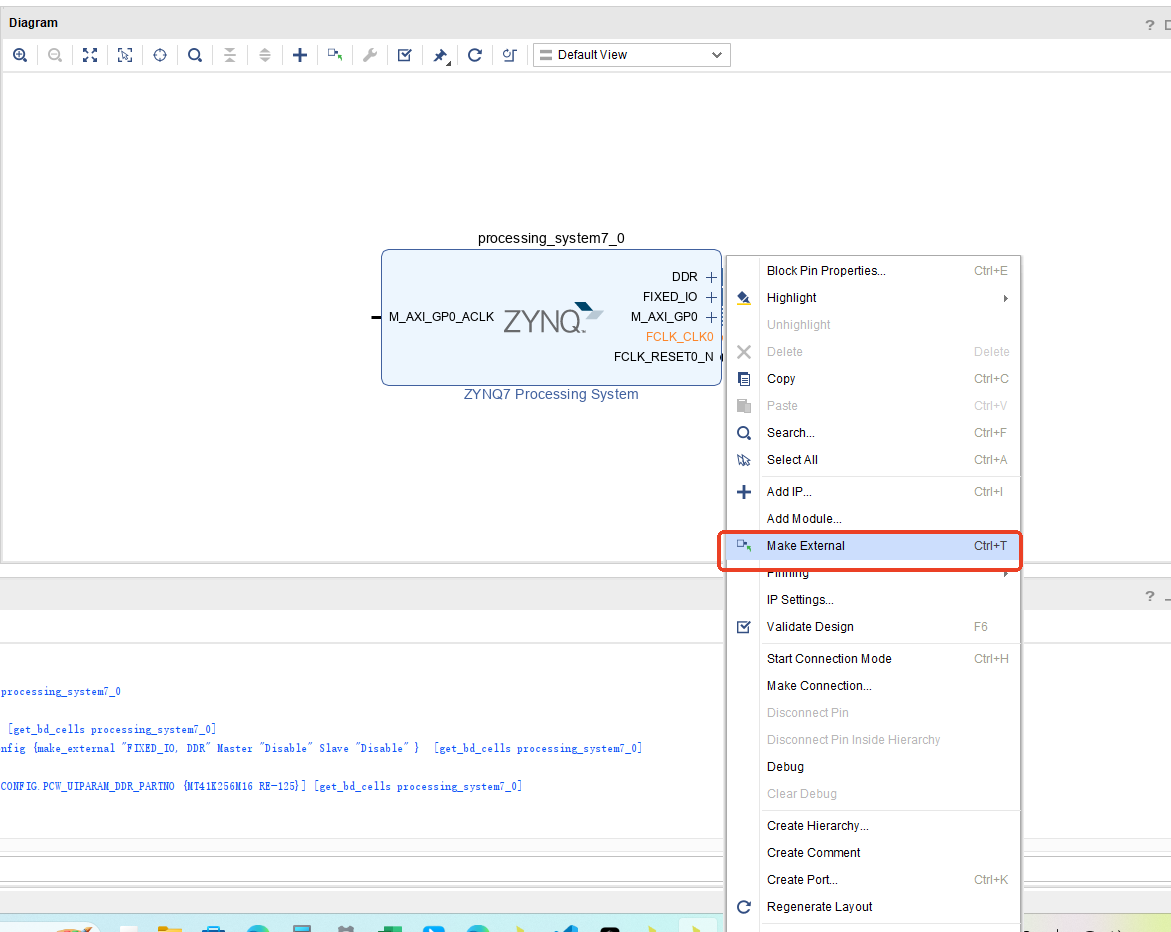

5)右键 FCLK_CLK0右边的线 ,然后点击Make External 将PS的时钟拉出,如下图所示

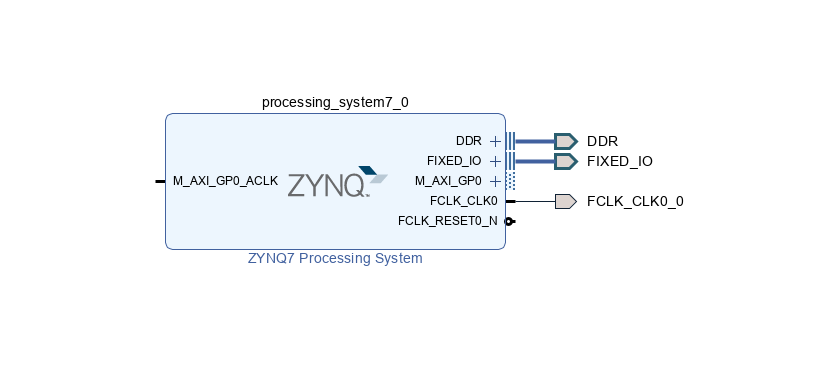

引出后 如下图所示

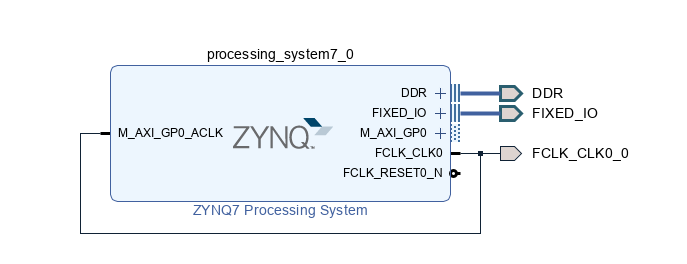

7)在FCLK_CLK0与 M_AXI_GP0_ACLK之间连接一根线,来为PS提供时钟(不连接会报错,也可以在ZYNQ设置界面禁用AXI接口,就不用连接了)

最终得到下图所示

上面已经完成了ZYNQ PS部分的设置,接下来设计自己的PL模块代码和与ZYNQ PS部分连接

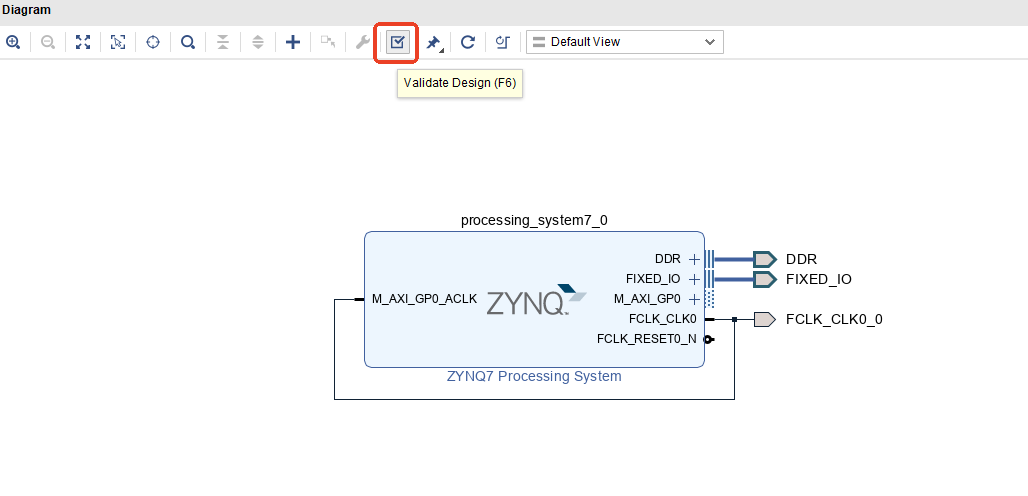

此时可以检查 block design 是否有设计错误 ,如果没有报错 正面设计是正确的

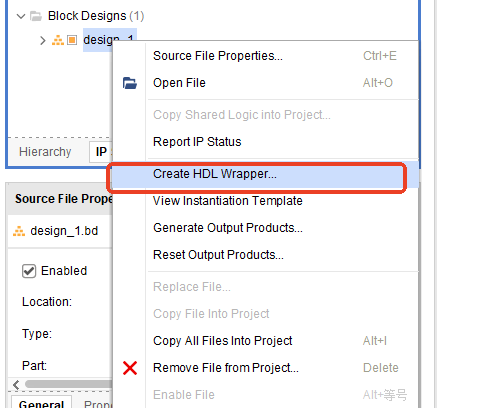

7)创建硬件描述,source→Design Source ,右键我们创建的BLOCK工程,点击create HDL wrapper如下图所示(这一步的作用相当于将图纸转换成对应的硬件描述语言的功能)

在弹出的对话框里保持默认

生成的wrapper文件会自动被设置为顶层

8)现在我们拥有了 时钟(ZYNQ 的PS模块),也拥有了 FPGA的.v模块,接下来要将两个模块结合起来,这里我们可以创建一个顶层TOP.V 模块然后在该顶层模块中例化ZYNQ

design_1_wrapper u_2(

.FCLK_CLK0_0(clk)

);

- 约束文件

PS时钟不需要约束

11)完成后点击Generate Bitstream(布线并生成二进制文件) 的操作(会提醒是否保存约束文件,点确认就好)

以上操作后,硬件PL以及PS的设置和布局已经完成,但是因为时钟是由PS端产生的,PS端的ARM运行时才能给PL提供时钟信号。直接将bit流文件下载到ZYNQ中,PS端并不会工作,也不会输出时钟给PL

想要让PS端工作,就需要在SDK创建一个工程,哪怕是个空工程也可以

以下是创建一个PS空工程的过程,详细的图文教程可以参考项目6

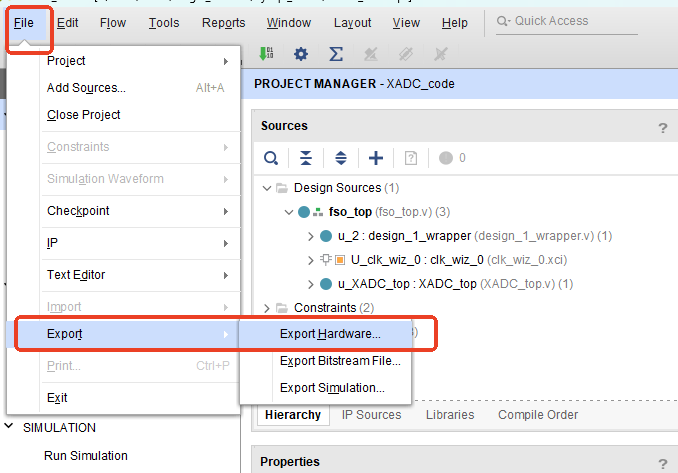

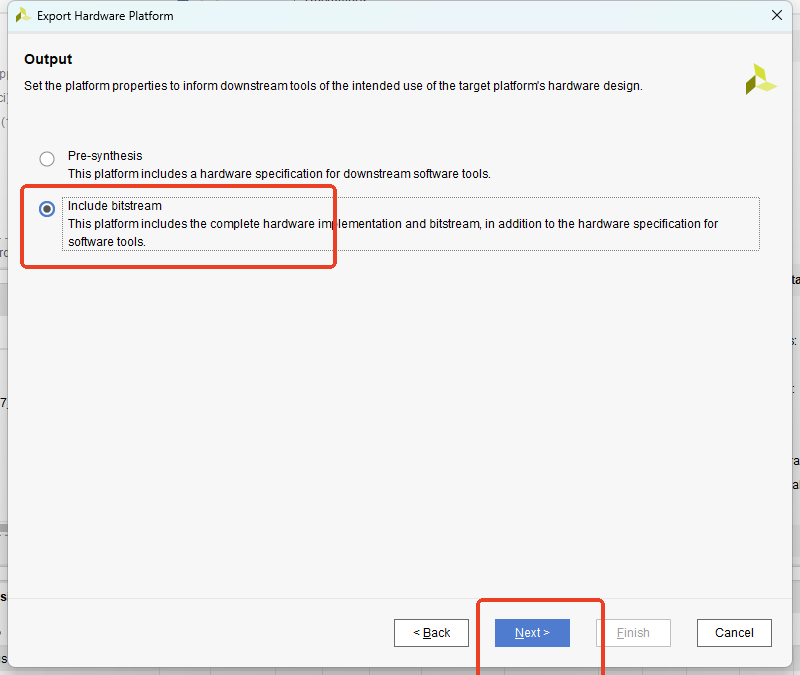

1)vivado中 选File→Export→Export hardware…,在弹出的对话框中勾选“include bitstream”,点击“OK”确认

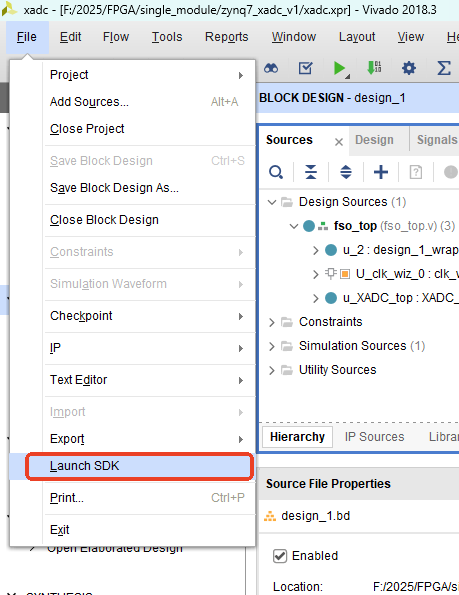

2)File→Lauch SDK,在弹出的对话框中,保存默认,点击“OK”, 系统将打开SDK工程

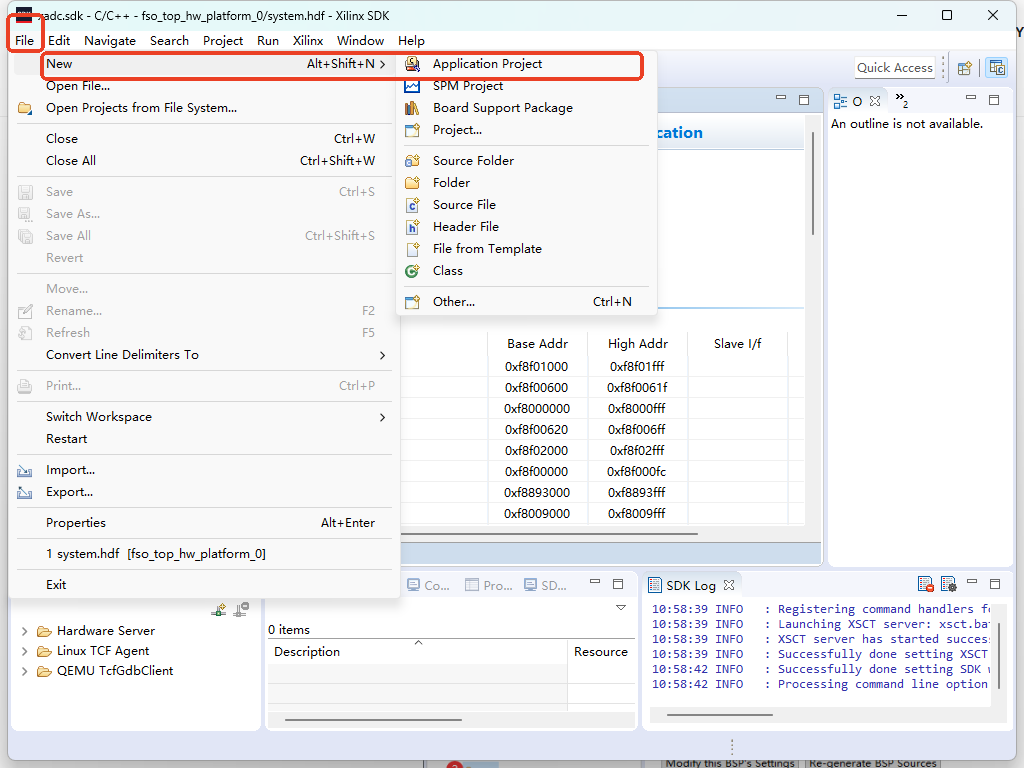

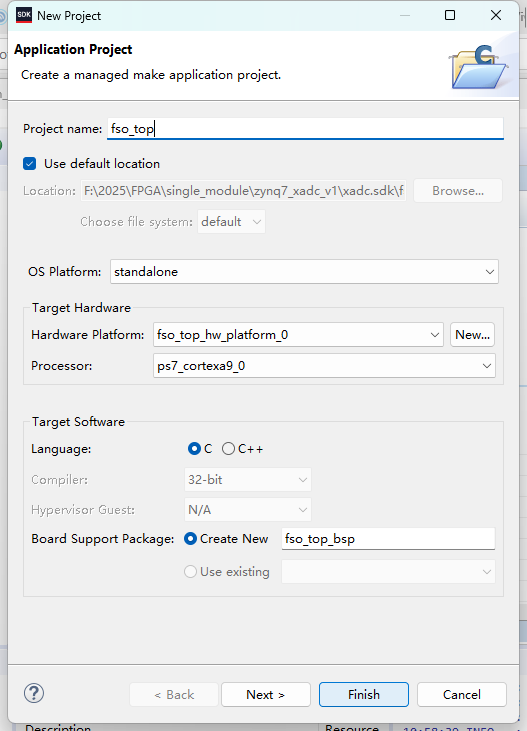

3)新建一个工程 file→new→Application Project,来新建一个“Application Project”,在新建工程中输入自己的工程名,并选择Empty Application(空应用)

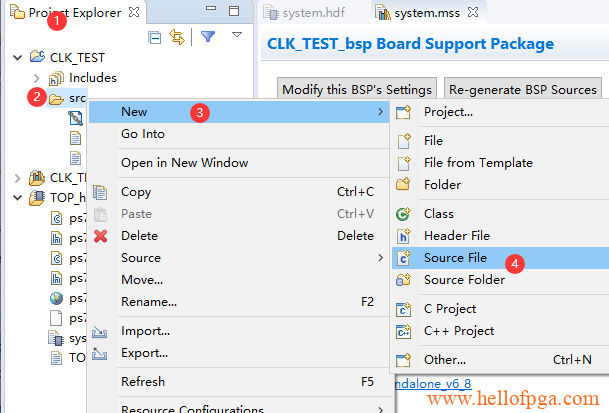

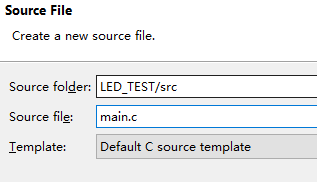

并且在空应用中创建一个main.c文件

并在里面复制以下代码(相当于创建了个空程序)

#include "xparameters.h"

#include "xplatform_info.h"

int main(void){

return 0;

}

然后点保存。

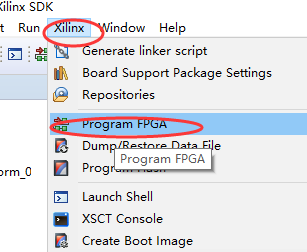

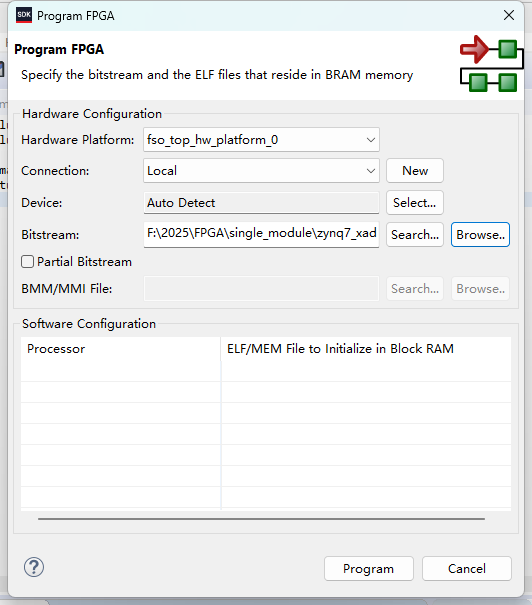

4)用之前生成的二进制文件对FPGA进行编程,Xilinx Tools -> Program FPGA 然后点击 “Program” (此时 DONE 灯被点亮,代表FPGA被配置完成)

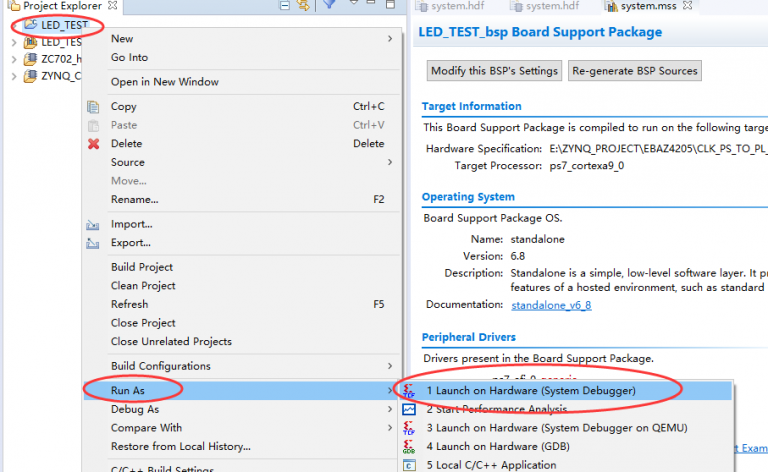

5)当FPGA编程成功后,我们需要初始化zynq中的处理器,右键点击刚才创建的空工程,选择Run As -> Launch on Hardware (System Debugger) 或者 Launch on Hardware (GDB).

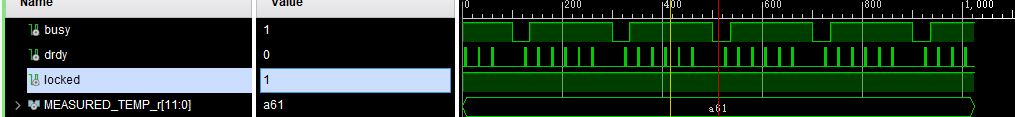

经过以上操作,可以看到ps输出到PL的locked信号正常锁定

9895

9895

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?