4 DDR5 SDRAM命令描述和操作-4

4.4 可编程的前导码和后导码

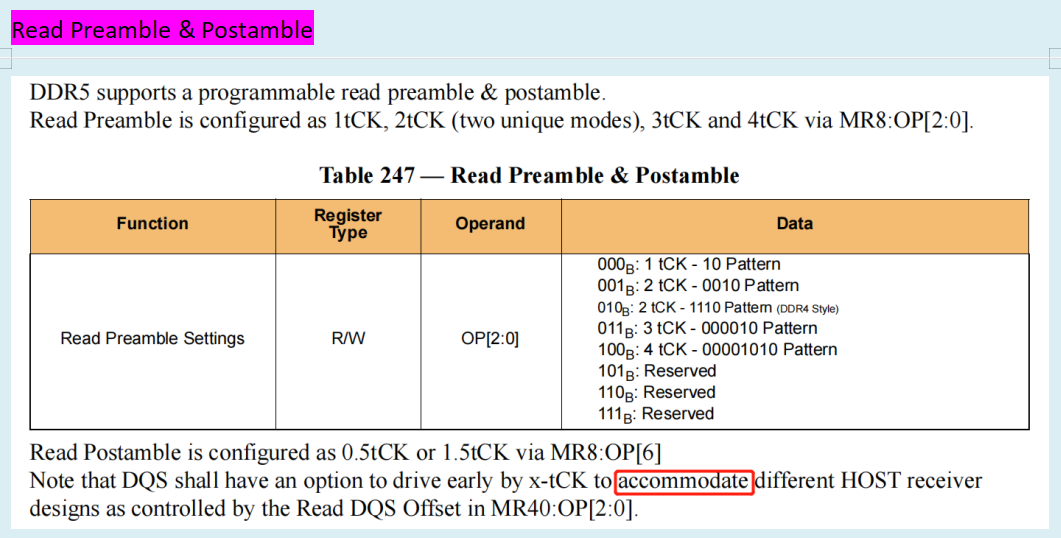

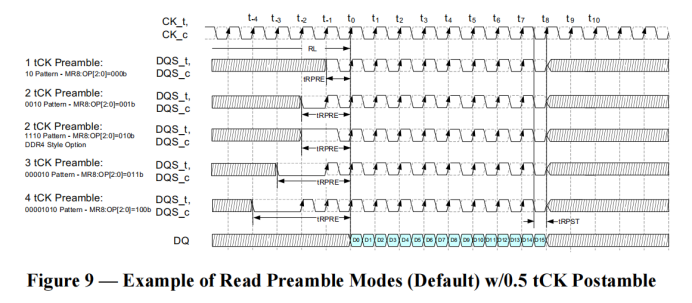

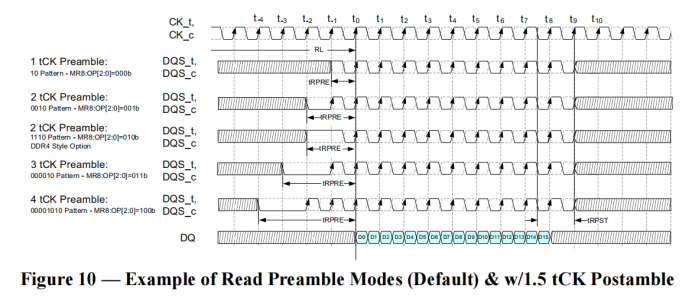

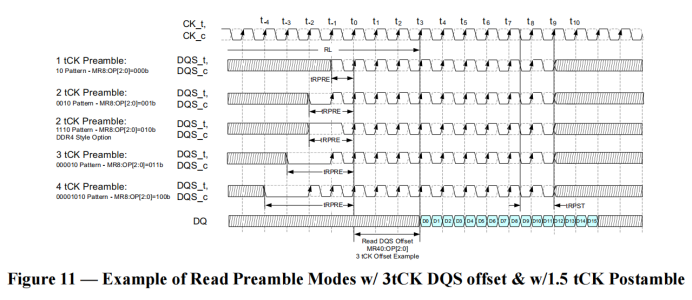

4.4.1 读前导码和后导码

accommodate:使适应,调节

Read Preamble通过MR8:OP[2:0]配置;

Read Postamble通过MR8:OP[6]配置;

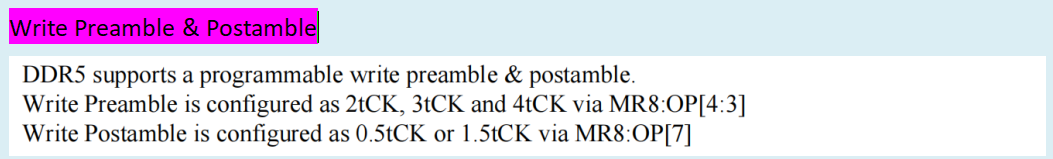

4.4.2 写前导码和后导码

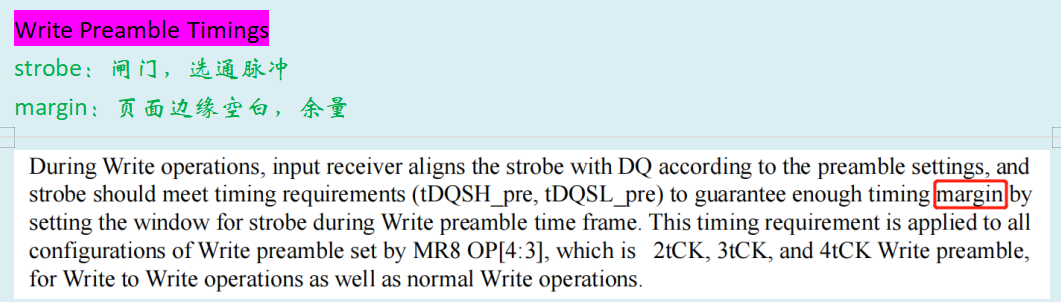

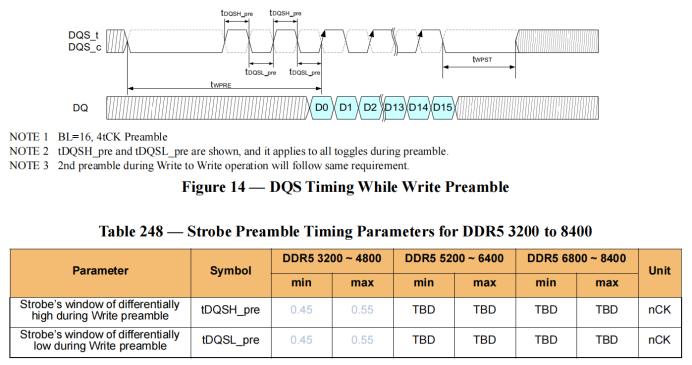

4.4.3 写前导码时序

写操作过程中,输入接收者根据前导码设定对齐选通脉冲和DQ,在写前导码时间框架,选通脉冲应通过设定

选通脉冲窗口,以满足时间要求(tDQSH_pre, tDQSL_pre)保证足够的时间裕量。

为了使连续写操作能像正常写操作一样进行,需要通过MR8 OP[4:3]对时间要求进行设定,写前导码设定的配

置有2tCK,3tCK,4tCK。

preamble的作用是这样的:DLL lock需要时间,需要给它预留这个时间窗口,让DLL完成phase alignment

(推90度相位),这样后面data采样的眼才最好,比如读dqs对在dq的正中间。

由于ODT设定、memory device驱动设定不同,总线寄生参数等影响,会导致preamble期间,dqs的三态转

换、重新assert的时间存在不确定性,如果没有postamble来“缓冲”一下,很有可能导致preamble不被采样

到或者采样出错。

但是seamless 读+读 或者seamless 写+写 (无缝的连续读读/写写同一BANK或已经激活的不同BANK)又可

以做到中间不用postamble和preamble。

主要诀窍是tCCD(CAS to CAS delay)= Min = BL/2,比如第一笔CAS发一个BL16,那么过tCCD 也就是

BL/2 = 8拍发第二笔的CAS,可以做到第二笔的数据和第一笔的数据直接无缝连接,中间不存在preamble与

postamble。

seamless读读、写写正是DDR协议为了解决preamble与postamble导致的效率损失而做出的增强,因为在连续

读读,连续写写的过程中,dqs的三态其实是不用发生转变的,可以利用前一笔的dqs,作为后一笔的

preamble,利用后一笔的dqs,作为前一笔的postamble。

当CAS超过tCCD(min)的情况下,消失的preamble与postamble又会回来。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?