4 DDR5 SDRAM命令描述和操作-22

4.22 连通性测试(CT)模式

4.22.1 简介

DDR5内存设备支持连接性测试(CT)模式,旨在极大地加快对PC板上DDR5内存设备与SoC上的内存控制器之间引脚互连电气连续性的测试速度。 CT模式被设计为与任何边界扫描设备无缝配合使用,对于所有DRAM设备,无论密度和接口宽度如何,都需要使用CT模式。这适用于x4、x8和x16接口宽度。与其他传统的基于移位寄存器的测试模式相反,在传统模式中,测试模式在每个时钟周期中逐个序列地移入和移出内存设备,而DDR5的CT模式可以同时将测试模式并行输入到测试输入引脚,并且同时从DDR5内存设备的测试输出引脚并行提取测试结果,大大提高了连接性检查的速度。

在进入CT模式之前,RESET_n被注册为高电平。通过断开测试使能(TEN)引脚,启用CT模式。

一旦通过断开TEN引脚进入CT模式,DDR5内存设备对外部控制器呈现为异步设备;在应用输入测试模式后,连接性测试结果在固定传播延迟之后可以并行提取到测试输出引脚,退出CT模式后需要对DDR5内存设备进行复位。

4.22.2 引脚映射

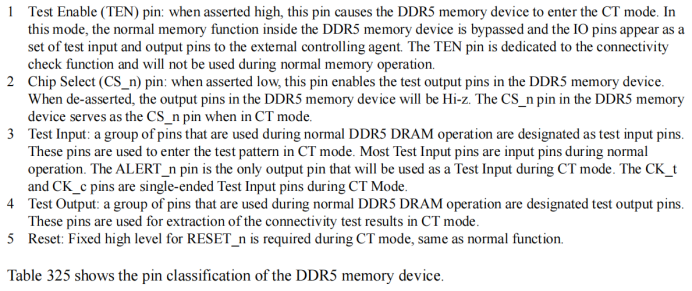

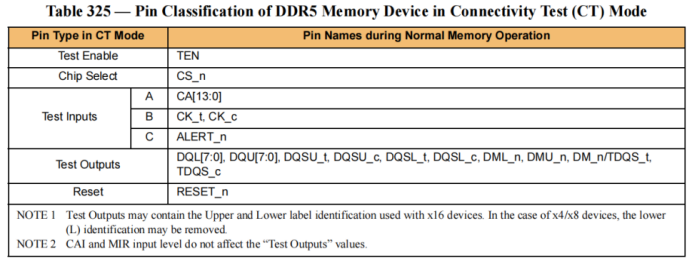

只有数字引脚可以通过CT模式进行测试。为了进行连接性检查,DDR5内存设备中用于数字逻辑的所有引脚都被分类为以下类型之一:

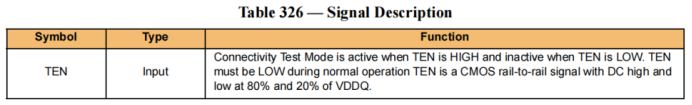

1. 测试使能(TEN)引脚:当该引脚被高电平激活时,DDR5内存设备进入CT模式。在该模式下,DDR5内存设备内部的正常存储功能被绕过,IO引脚作为一组测试输入和输出引脚对外部控制器可见。TEN引脚专用于连接性检查功能,并在正常存储操作期间不使用。

2. 芯片选择(CS_n)引脚:当该引脚被低电平激活时,DDR5内存设备中的测试输出引脚被使能。当该引脚取消激活时,DDR5内存设备中的输出引脚将进入高阻态。在CT模式下,DDR5内存设备的CS_n引脚作为CS_n引脚使用。

3. 测试输入:一组在正常DDR5 DRAM操作期间使用的引脚被指定为测试输入引脚。这些引脚用于在CT模式下输入测试模式。大多数测试输入引脚在正常操作期间是输入引脚。在CT模式下,ALERT_n引脚是唯一会被用作测试输入的输出引脚。CK_t和CK_c引脚是在CT模式下的单端测试输入引脚。

4. 测试输出:一组在正常DDR5 DRAM操作期间使用的引脚被指定为测试输出引脚。这些引脚用于提取CT模式下的连接性测试结果。

5. 复位:在CT模式下需要将RESET_n固定为高电平,与正常功能一样。

表325显示了DDR5内存设备的引脚分类。

4.22.3 逻辑方程

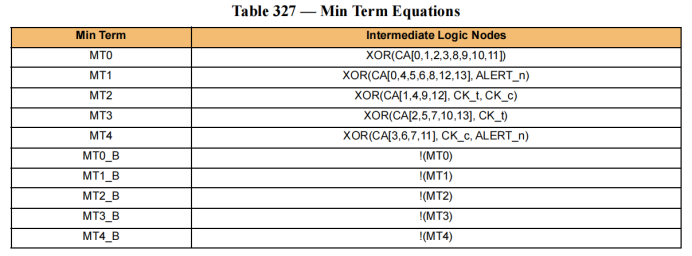

4.22.3.1 最小项方程

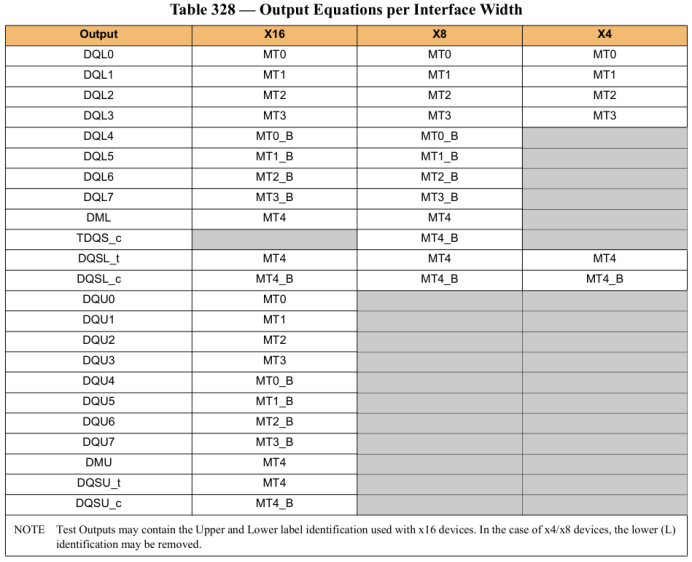

MTx是一个内部信号,用于产生驱动输出信号的信号。请参考表327。这些内部信号在所有接口宽度和密度中都是相同的。

4.22.3.2 输出方程

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?