删除debug后,实现的时候报错:

[DRC REQP-1712] Input clock driver: Unsupported PLLE2_ADV connectivity. The signal algcore_dcm/CLKIN1 pin of XXXXX with COMPENSATION mode ZHOLD must be driven by a clock capable IO.

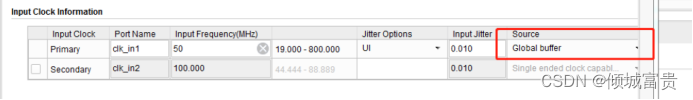

PLL IP核设置出现问题。因为从上面的代码里可以看到我的PLL的输入信号clk是来自IBUFGDS的输出信号clk,而不是来自普通的单端时钟信号。虽然我的IBUFGDS已经把差分时钟变成了单端时钟,但是它仍然不是普通的单端时钟信号,这点记住就行,因此我们需要修改PLL的clk_in1的source参数。

查找后发现很多人都说把PLL设置里的单端信号改成全局时钟:

新问题:锁相环产生的时钟被优化掉了。

解决:有可能设置debug会自动将时钟添加到全局时钟域中,将PLL设置恢复并重新设置debug后锁相环产生的时钟正常了。

1715

1715

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?