几个常见的FPGA问题之全加器

语言 :Verilg HDL 、VHDL

EDA工具: Vivado

- 关键词: Verilog HDL, generate语句,全加器

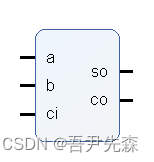

一、使用Verilog HDL语言实现1位带进位标志的全加器。全加器的真值表如下,其中ai为被加数,bi为加数,ci为低一位的进位,这3个数相加生成和sumi,及高位进位ci+1。

请根据真值表,通过卡诺图化简得到全加器的逻辑表达式;

请根据全加器的逻辑表达式编写全加器源代码;

请编写仿真代码进行测试,

请将该工程生成 IP 核。

全加器逻辑表达式:

so = a ^ b ^ ci ; co = (a & b) | (a & ci) | (b & ci);

源码

module full_adder(

input a, // 第一个加数

input b, // 第二个加数

input ci, // 进位输入

output so, // 求和结果

output co // 进位输出

);

// 求和结果so

assign so = a ^ b ^ ci;

// 进位输出co

assign co = (a & b) | (a & ci) | (b & ci);

endmodule

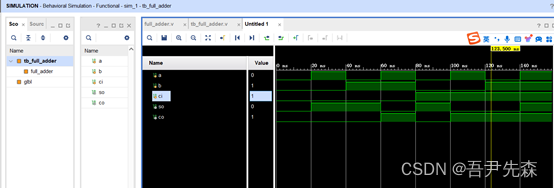

(3)仿真测试

`timescale 1ns / 1ps

module tb_full_adder( );

reg a;

reg b;

reg ci;

wire so ;

wire co;

full_adder full_adder(

.a (a), // 第一个加数

.b

本文介绍了如何使用Verilog HDL语言实现1位全加器,包括逻辑表达式、源码和仿真测试,并详细讲解了如何构建工程,调用全加器IP核实现8位全加器,包括设计过程和仿真结果。

本文介绍了如何使用Verilog HDL语言实现1位全加器,包括逻辑表达式、源码和仿真测试,并详细讲解了如何构建工程,调用全加器IP核实现8位全加器,包括设计过程和仿真结果。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

896

896

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?