一、分布延迟(Distributed Delay)

1、概念

分布延迟将延迟均匀地分布到一个元件或者一条路径的各个部分。在分布延迟模型中,信号的每一个节点或者每一段路径都有对应的延迟,信号在传输过程中会逐步积累这些延迟。这种模型更贴近实际电路中信号传播的物理特性,因为在实际电路里,信号的延迟是在整个传输路径上逐渐产生的。

2、语法与示例

在 Verilog 里,分布延迟是通过在连续赋值语句或者门级实例化语句中使用延迟说明来实现的。

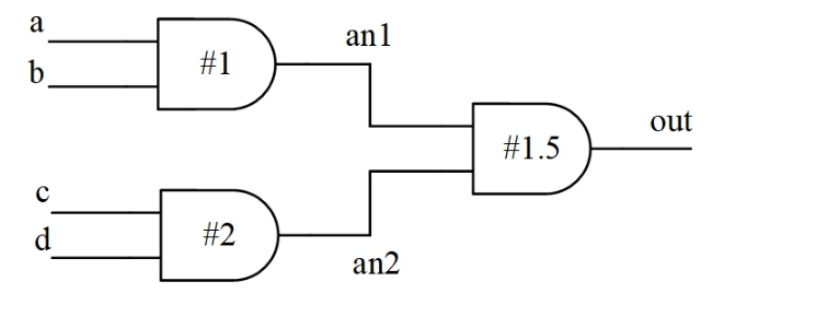

示例:

and #2 (an2, c, d); // 与门延迟2单位

assign #1.5 an1 = a & b; // assign语句延迟1.5单位

应用场景:简单电路或需要精细时序控制的模块

延迟时间分散在每个门单元上,但仍然不能描述基本单元中不同引脚上延时的差异,当设计规模变大时,结构将变的复杂;

二、集总延迟(Lumped Delay)

1、概念

集总延迟是将整个元件或者路径的延迟集中在一起进行考虑,不考虑信号在元件内部或者路径上的具体延迟分布。它把元件或者路径看作一个整体,只关注输入和输出之间的总延迟。

2、语法与示例

在 Verilog 中,集总延迟通常在门级实例化时使用。

module lumped_delay_example;

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1526

1526

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?