目录

(以下是更新版)

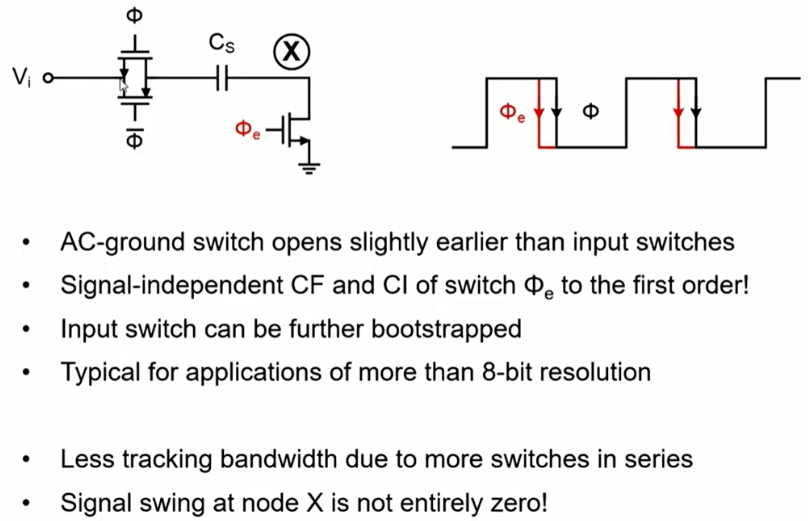

下级板采样(Bottom-Plate Sampling)

Sampling-and-Hold Amplifier (SHA)

用处:①外部输入单端信号的话,可以用运放进行单端转差分。

②外部输入信号过小,可以用运放进行放大。

③驱动能力大

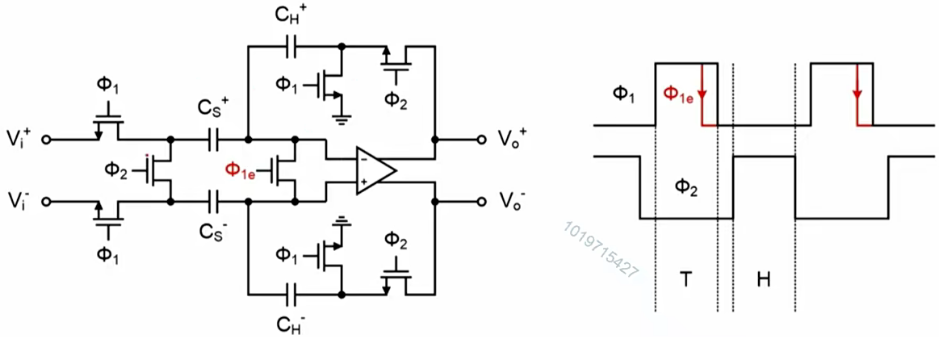

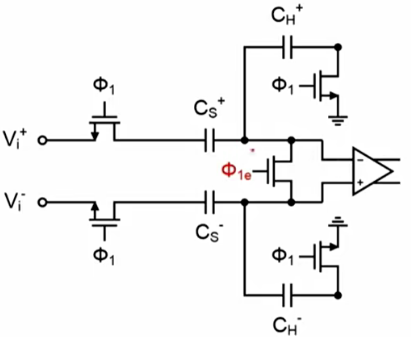

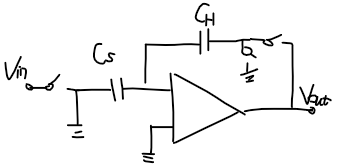

Inverting SHA

特点:反相,有增益,环路增益取决于 Cs/Ch 的比值。开关管可以换成Bootstrap

工作原理:

Track阶段:下级板采样,φ1e先断开,运放输出节点是ac地。φ1e先断开,使得开关管动作产生的distortion影响大大减小,有影响的是φ1e管子,对于差分信号,其等效成两个W/2L的管子串联,对每一端的Charge injection和clock feedthrough都较小,同时差分的话,其动作产生的CF和CI可以抵消掉。同时Ch两端都接地,Ch上电荷为0。

Hold阶段:Track时运放输入时ac_0,Hold之后,Cs另一端也是ac_0,电荷全部跑到Ch上,从而当Ch=Cs时,Vout = Vin。 相当于开关电容放大器,Vout = - (1+Cs/Ch)*Vin。

●输入和输出的共模电平不一样,可以用来做共模电平转换。

●如果Cs=Ch,signal_gain = 1;amp_gain = 2。即信号一比一复制到输出,然鹅噪声翻倍到输出。造成信噪比下降。

●方便进行single-ended to differential 单端转差分信号转换。

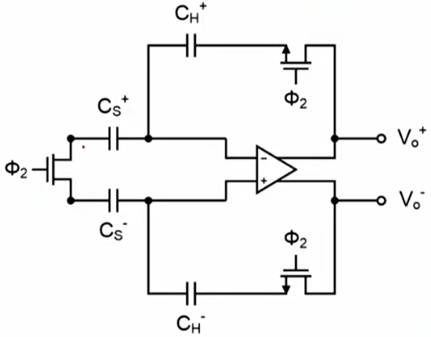

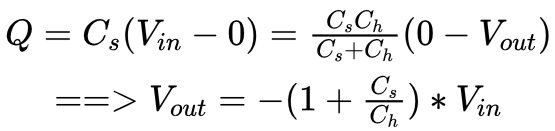

Flip Around SHA(none-inverting SHA)

信号增益和运放增益都为1,不能对信号进行放大,但是信噪比相对inverting结构较好一点。

(以下是旧版)

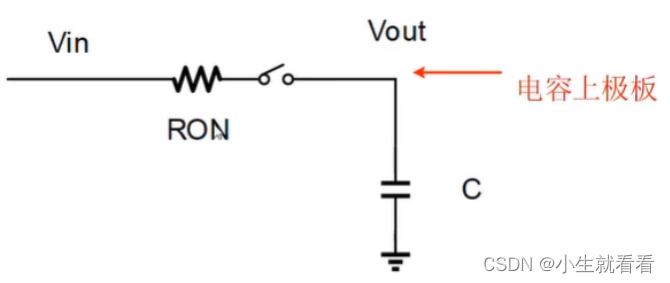

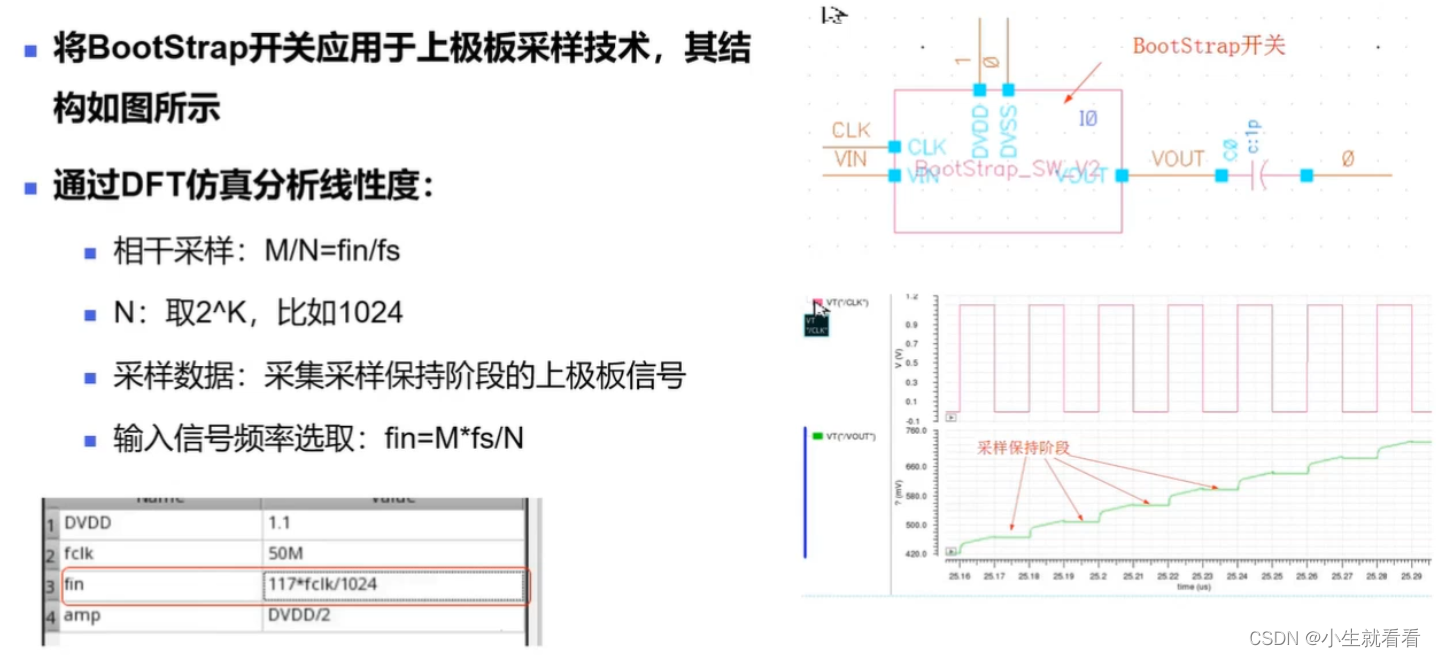

上级板采样技术

原理:

- 采样阶段:CLK = 1,电容下级板接 gnd(ac),上级板通过开关接Vin

- 采样结束:CLK下降沿!电荷存储在电容上级板,Q=Vin*C,Vin的信号存储在C上。

上级板采样非理想特性:

- 开关断开瞬间沟道电荷(共享消散)

- 时钟馈通(开关管Cgd)

- 上级板技术将采样精度限定在~10位

上级板采样技术:线性度分析

做DFT时主要采样的信号要是采样保持信号,在CLK=0的时候的稳定的信号

注意:算 fin 的时候不要自己计算确定的值,直接填为公式 fin = M*fs/N,软件会自动四舍五入。

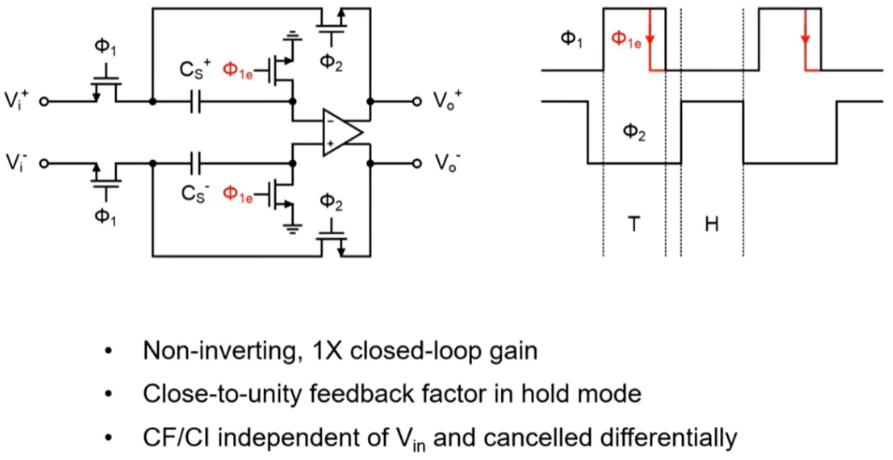

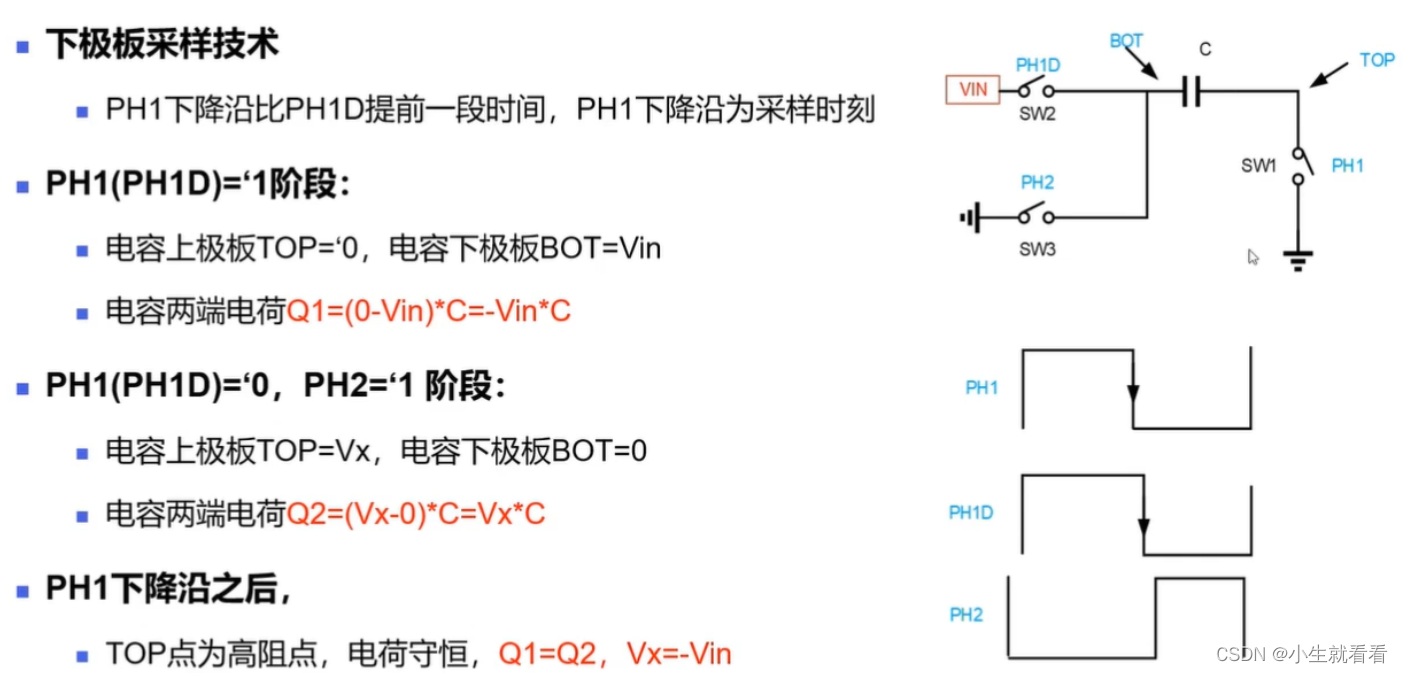

下级板采样技术--非交叠时钟

非交叠时钟:PH1D和PH2,PH1 比 PH1D 下降沿提前到来(上升沿随意),提前多长时间随意。

第一阶段:PH1=1,PH1D=1,PH2=0:

BOT = Vin;TOP = 0;电容两端电荷Q1 = (0 - Vin)*C = -Vin*C;

第二阶段:PH1=0,PH1D=1,PH2=0:(PH1提前下降)(PH1D下降沿时才会采样)

BOT = Vin+△V,TOP = △V ;TOP开始浮空,电容两端开始电荷守恒。

第三阶段:PH1=0,PH1D=0,PH2=0:(电容浮空)

TOP为高阻节点,电荷守恒,Q1=Q2,

第四阶段:PH1=0,PH1D=0,PH2=1:

BOT = 0,TOP = Vx = -Vin;电容两端电荷Q2 = (Vx-0)*C = Vx*C

直接阶段一和阶段四电荷守恒(中间状态全可忽略):Q1=Q2,Vx = -Vin

第二阶段第三阶段中间的△V,只是中间状态,不在乎,最后 初态和终态 电荷守恒,只要BOT终态为0,那么TOP终态就知道为Vin。(BOT初态:Vin,终态:0;TOP初态:0,终态Vin)

注意电路中的是 gnd_ac,是一个共模信号!(BOT的共模最好等于Vin的共模)

例如:PH2的共模为Vcm1(BOT),PH1的共模为Vcm2(TOP),最终的TOP = Vcm2 - Vin。

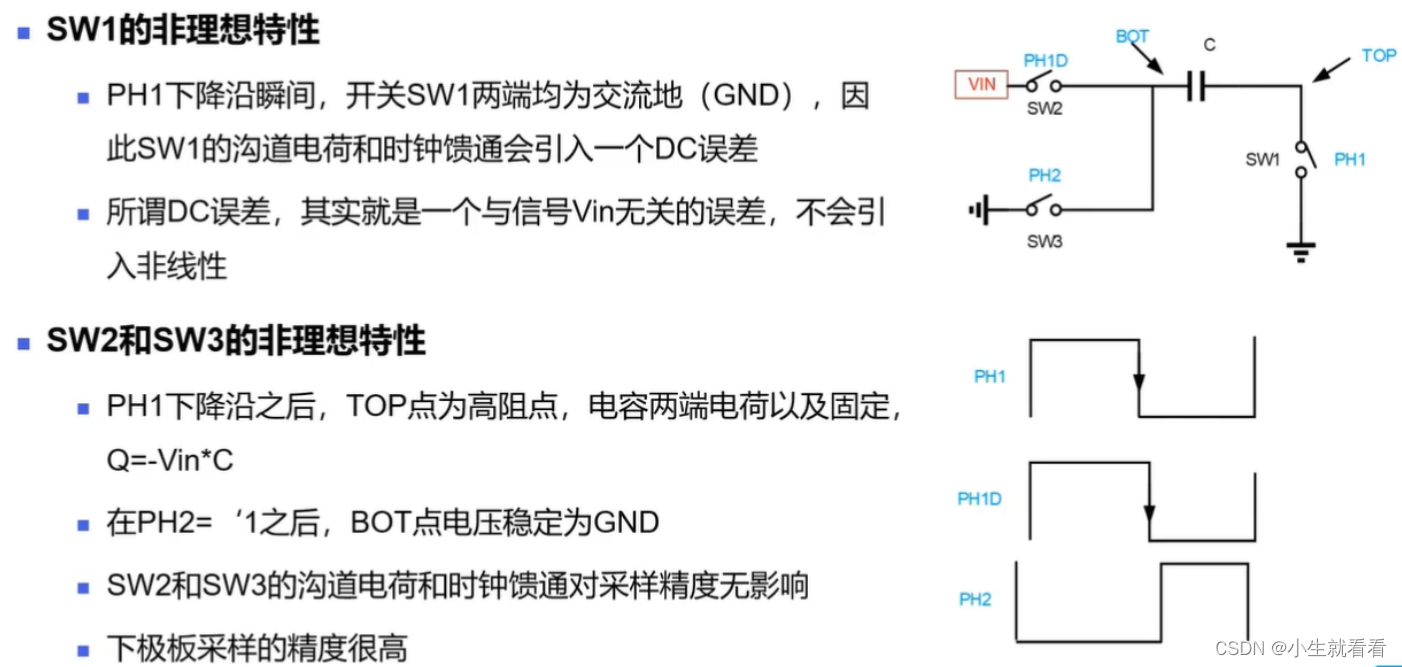

下级板采样技术误差分析

要求非交叠时钟,时序不能错

SW1:在PH1下降沿瞬间引入DC误差(Offset),不影响线性度。(全差分即可消除)

SW2:在PH1下降之后,TOP就开始电荷守恒初态,只要初态和终态确定,SW2(PH1D)动作影响的中间状态,对最终结果没有影响。

SW3:动作影响的是中间状态,对最终结果无影响,因为终态是SW3闭合恒定时。要求是驱动能力能够将BOT拉倒gnd_ac。

设计关键点:SW1和TOP点,该屏蔽的屏蔽,寄生效应该降低的降低,全差分两个SW1高度匹配

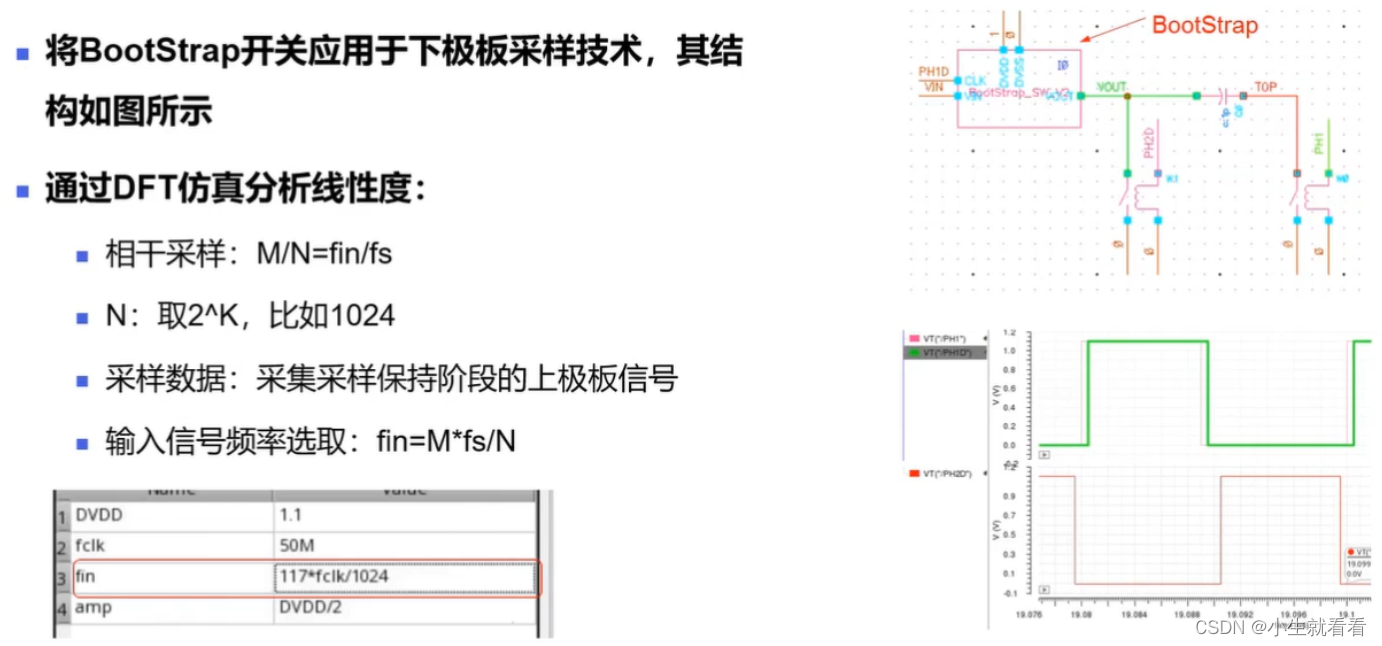

下级板采样技术:线性度分析

文章详细介绍了下级板采样技术,包括Sampling-and-HoldAmplifier的工作原理、InvertingSHA和FlipAroundSHA的特点,以及非交叠时钟在采样中的应用和误差分析。线性度分析是关注的重点,讨论了不同结构对信号复制和信噪比的影响。

文章详细介绍了下级板采样技术,包括Sampling-and-HoldAmplifier的工作原理、InvertingSHA和FlipAroundSHA的特点,以及非交叠时钟在采样中的应用和误差分析。线性度分析是关注的重点,讨论了不同结构对信号复制和信噪比的影响。

157

157

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?