目录

1、前言

PCIE(PCI Express)采用了目前业内流行的点对点串行连接,比起 PCI 以及更早期的计算机总线的共享并行架构,每个设备都有自己的专用连接,不需要向整个总线请求带宽,而且可以把数据传输率提高到一个很高的频率,达到 PCI 所不能提供的高带宽,是目前各行业高速接口的优先选择方向,具有很高的实用价值和学习价值;

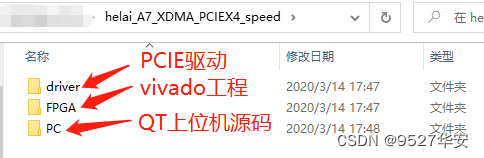

本设计使用Xilinx官方的XDMA方案搭建基于Xilinx系列FPGA的PCIE通信平台,该方案只适用于Xilinx系列FPGA,一并提供了XDMA的安装驱动和QT上位机源代码,省去了使用XDMA繁琐的驱动寻找和上位机软件开发的不知所措,并以搭建好vivado工程,省去了不知道如何使用XDMA的尴尬,使得PCIE的使用变得简单易上手,而不用关心其复杂的PCIE协议;由于我的开发板只支持PCIE X4,所以提供的代码是PCIE X4架构,若需要PCIE X1、 X2、 X8、 X16、 X32的朋友,可自行修改本工程,也可关注我,我会实时发布新的工程。

本工程实现基础的PCIE通信,和QT上位机之间进行测速试验。

本文详细描述了基于XDMA搭建PCIE通信平台的设计方案,工程代码可综合编译上板调试,可直接项目移植,适用于在校学生、研究生项目开发,也适用于在职工程师做项目开发,可应用于医疗、军工等行业的高速接口领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

2、我已有的PCIE方案

我的主页有PCIE通信专栏,既有基于RIFFA实现的PCIE方案,也有基于XDMA实现的PCIE方案;既有简单的数据交互、测速,也有应用级别的图像采集传输,以下是专栏地址:

点击直接前往

3、PCIE理论

这部分可自行百度或csdn或知乎学习理论知识,其实用了XDMA,已经不太需要直到PCIE复杂的协议和理论了。。。

4、总体设计思路和方案

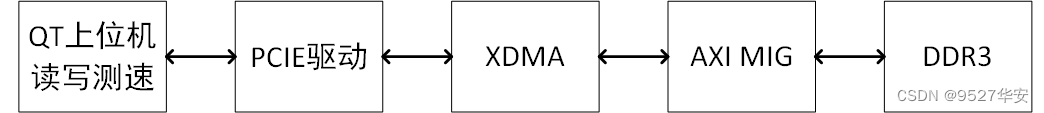

总体设计思路和方案如下:

PCIe 通信例程由三部分组成:FPGA 端程序、PCIe 卡驱动、PCIe 上位机测试程序:

FPGA 端工程:负责建立与 PCIe 通信需具备的 FPGA 框架,PCIe 通信协议的构建;

PCIe 驱动:负责上位机测试程序与 PCIe 卡的数据交换;

PCIe 上位机测试程序:此处时PCIe 测速;

PICe 时钟输入通过 PCIe 接口接入外部 PCIe 时钟 100M(如机箱 PCIe 插槽),为 PCIe 通信模块工作提供参考时钟;ddr 时钟输入模块为 DDR 控制器提供参考时钟;当 PCIe 进行写速度测试时,上位机连续发送测试数据给 PCIe 通信模块,然后把数据传给 DDR 控制器,DDR 控制器会自己把数据存入 DDR3 芯片中;当 PCIe 进行读速度测试时,DDR 控制器会获取 DDR3 芯片中数据,然后把数据传给 PCIe 通信模块,上位机连续获取来自 PCIe 通信模块测试数据;当 PCIe 进行读写速度测试时,进行 PCIe 读速度测试的同时控制 PCIe写速度测试。流程是在上述写速度与读速度测试的结合。

QT测速上位机:提供源代码和可执行程序,发开版本为QT5.6.2;

PCIE驱动:提供Win系统驱动;

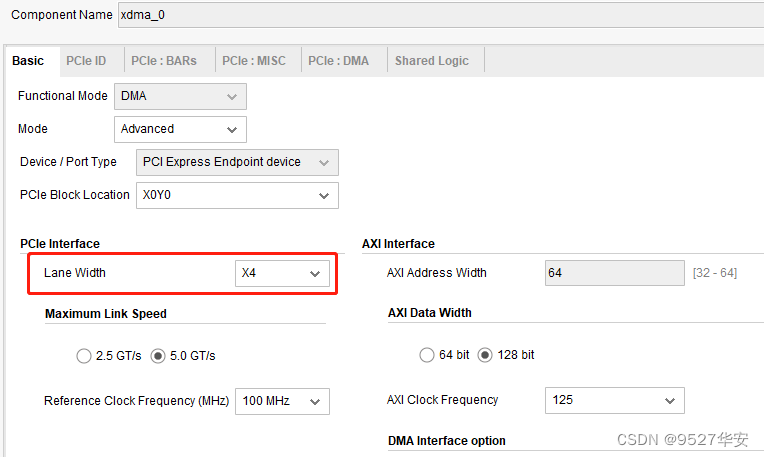

XDMA:调用官方IP,配置为X4模式;

AXI MIG:调用官方IP,作为数据缓存;

5、vivado工程详解

开发板FPGA型号:Xilinx xc7a100tfgg484-2;

开发环境:Vivado2019.1;

输入\输出:PCIE X4;

应用:QT上位机测速试验;

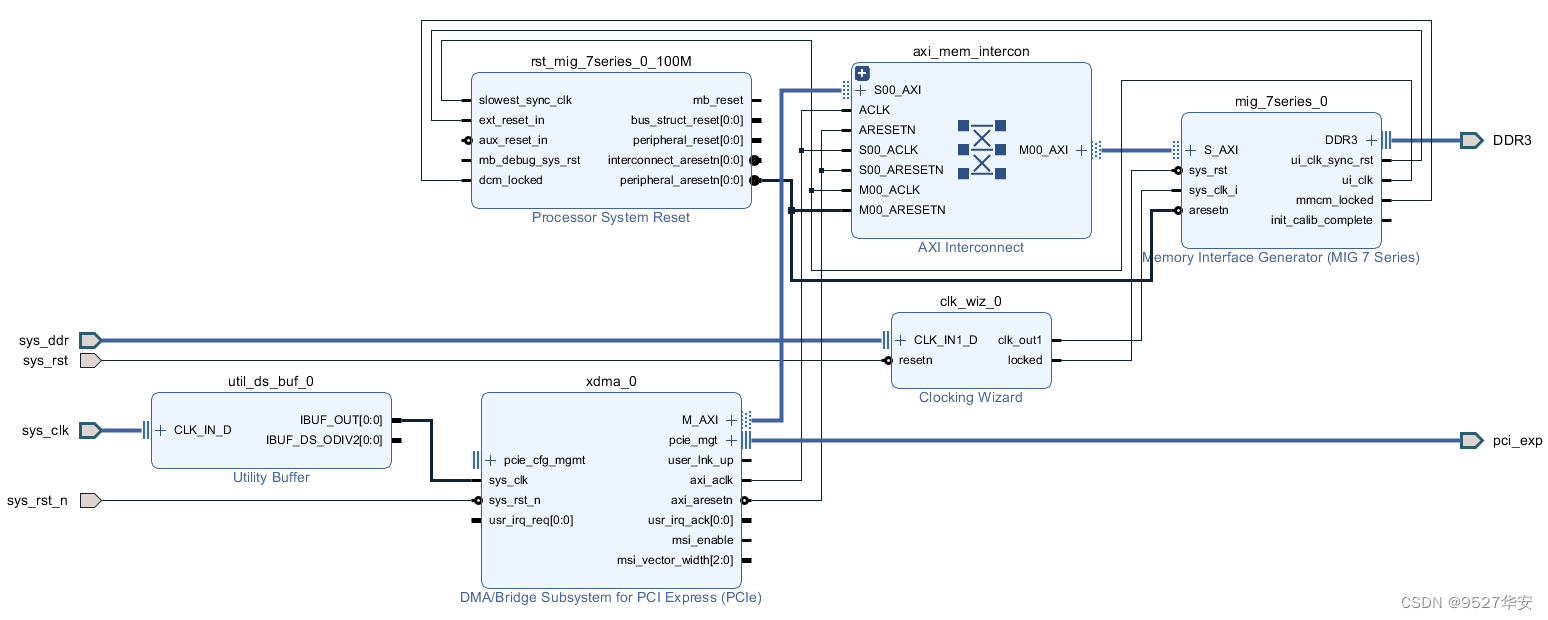

工程BD如下:

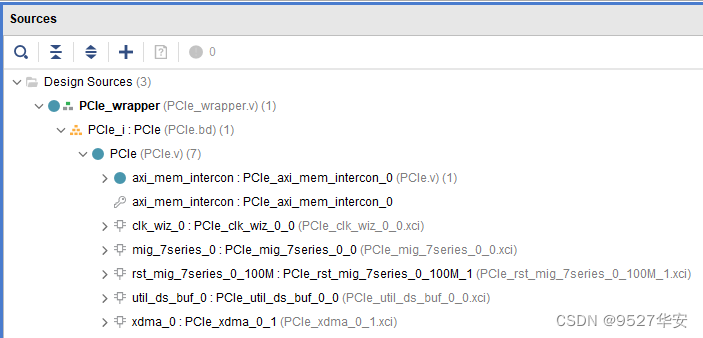

综合后的工程代码架构如下:

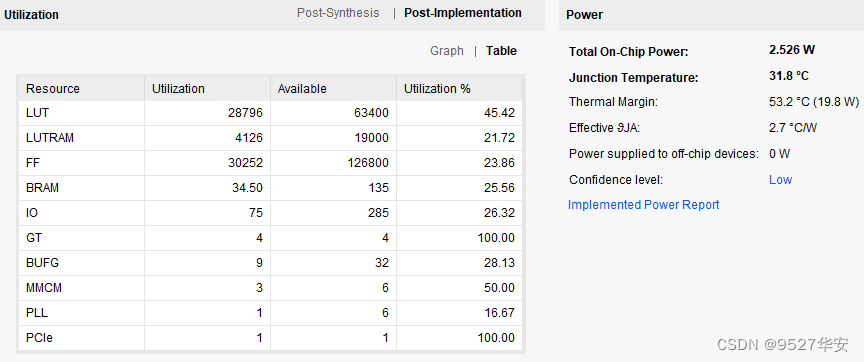

综合编译完成后的FPGA资源消耗和功耗预估如下:

6、驱动安装

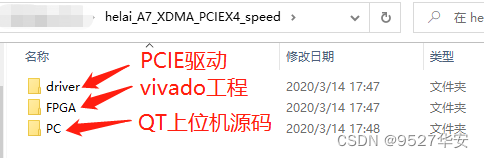

提供提供Win系统驱动,目录如下:

安装步骤:

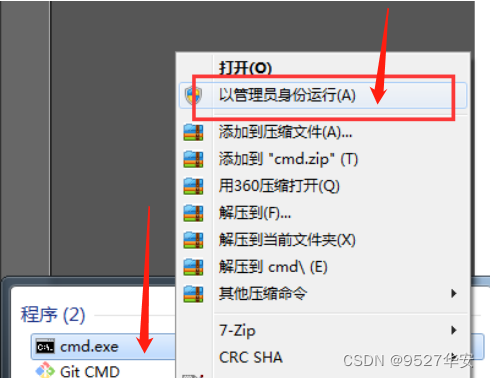

使用管理员身份运行 cmd

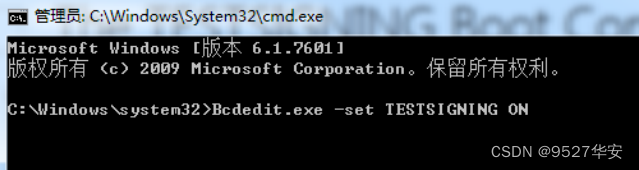

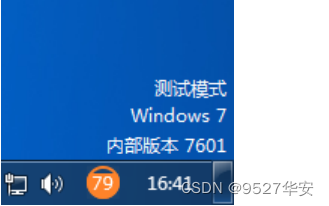

输入命令 Bcdedit.exe -set TESTSIGNING ON 打开测试模式:

重启电脑后桌面显示正在运行测试模式

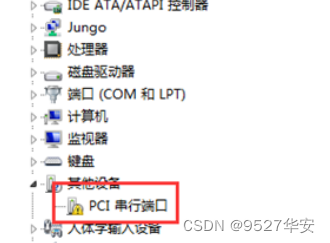

没有安装驱动时,设备管理器如下,发现一个 PCI 串行端口:

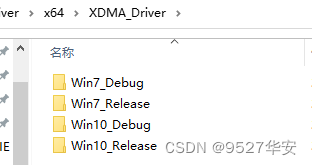

例程提供的编译好的驱动程序,在工程下的 driver 目录下(根据操作系统选择相应驱动),

在 demo 目录下的“xilinx PCIe 驱动相关资料”提供了 xilinx 官方的 Windows 和 linux 驱动源码及

测试程序,有兴趣的自己可以研究研究:

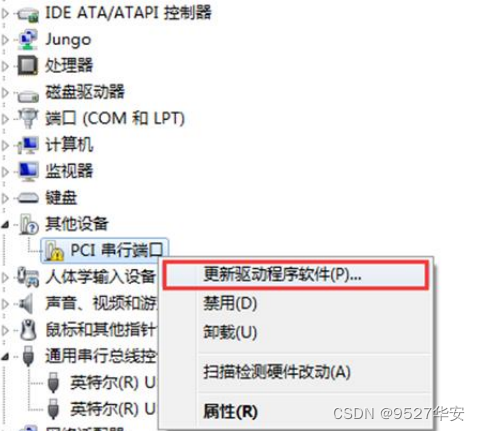

选择设备,右键更新驱动

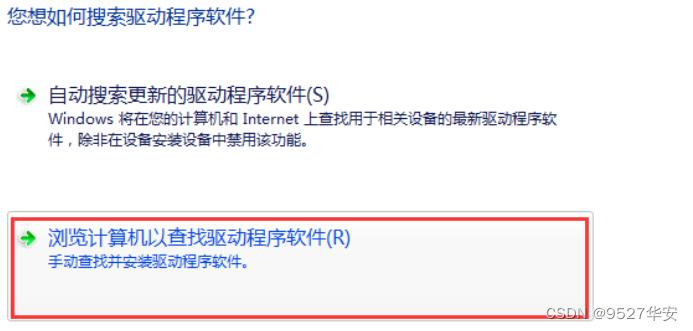

浏览计算机以查找驱动程序软件

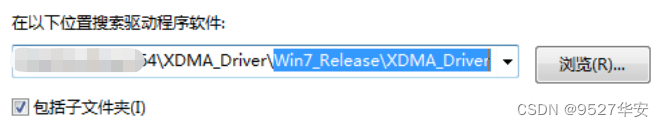

测试电脑安装的是 win7,这里使用 Win7_Release 版本,win10系统则换为Win10_Release 版本:

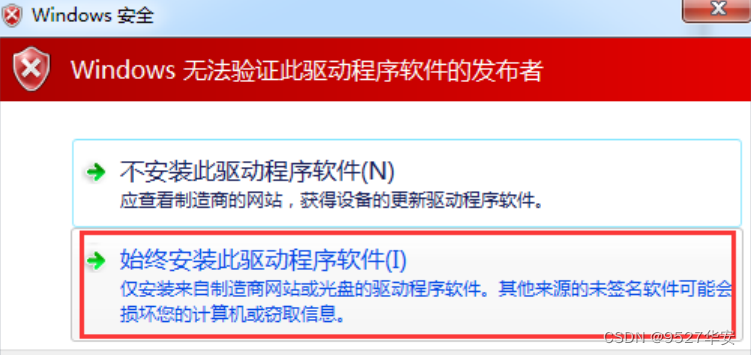

有个安全警告,选择安装:

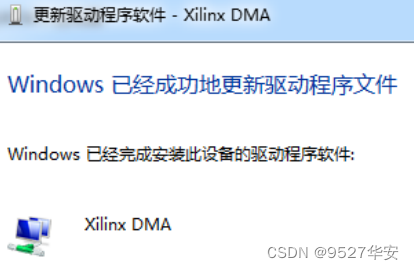

正确安装了设备驱动

7、QT上位机软件

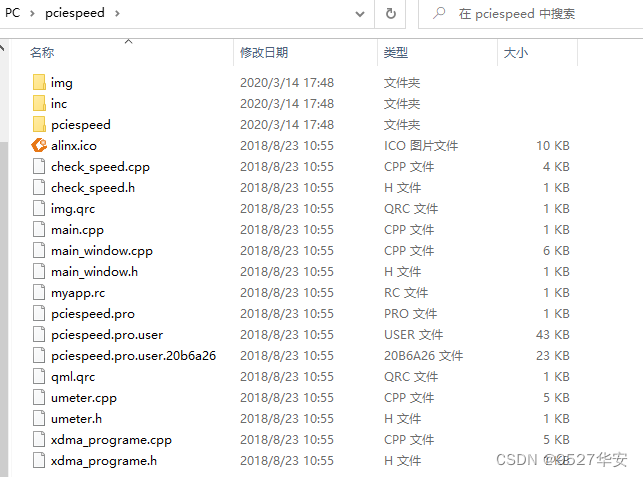

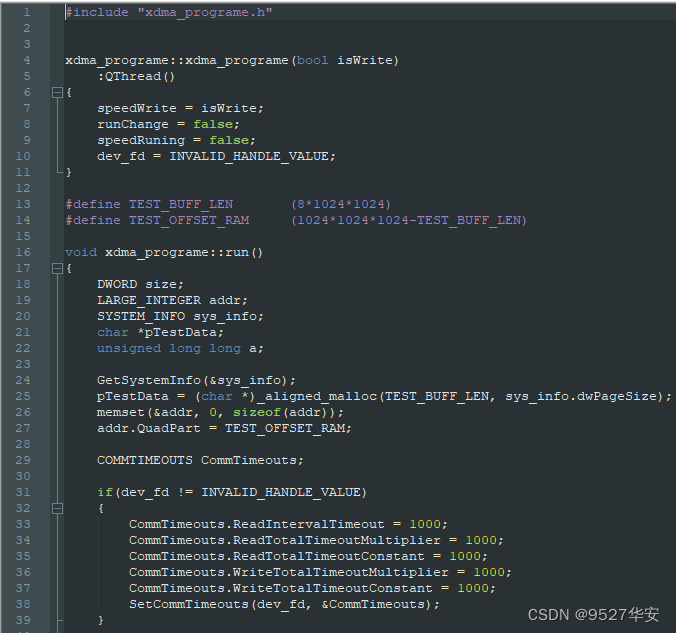

QT测速上位机:提供源代码和可执行程序,发开版本为QT5.6.2;位置如下:

部分源码截图如下:

8、工程移植说明

vivado版本不一致处理

1:如果你的vivado版本与本工程vivado版本一致,则直接打开工程;

2:如果你的vivado版本低于本工程vivado版本,则需要打开工程后,点击文件–>另存为;但此方法并不保险,最保险的方法是将你的vivado版本升级到本工程vivado的版本或者更高版本;

3:如果你的vivado版本高于本工程vivado版本,解决如下:

打开工程后会发现IP都被锁住了,如下:

此时需要升级IP,操作如下:

FPGA型号不一致处理

如果你的FPGA型号与我的不一致,则需要更改FPGA型号,操作如下:

更改FPGA型号后还需要升级IP,升级IP的方法前面已经讲述了;

其他注意事项

1:由于每个板子的DDR不一定完全一样,所以MIG IP需要根据你自己的原理图进行配置,甚至可以直接删掉我这里原工程的MIG并重新添加IP,重新配置;

2:根据你自己的原理图修改引脚约束,在xdc文件中修改即可;

3:纯FPGA移植到Zynq需要在工程中添加zynq软核;

9、上板调试验证

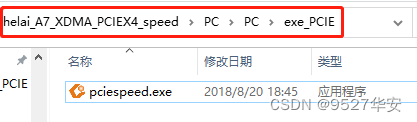

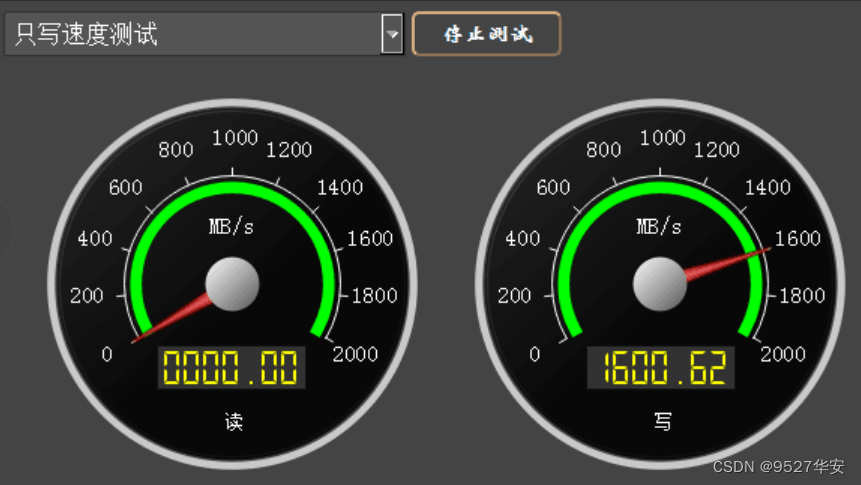

开启上位机测程序进行 PCIe 速度测试,打开下图的测速软件 pciespeed,测速软件在如下位

置,实验结果如下:

读写同时进行测试:

只读测试:

只写测试:

10、福利:工程代码的获取

福利:工程代码的获取

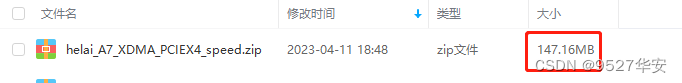

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

1785

1785

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?