超详细的quartusⅡ调用PLL IP核过程与原理讲解,实现倍频

任务要求

输入为50MHz的时钟信号,要求使用pll 产生一个150MHz核80MHz的输出信号,并包含90度与80度的相移

quartusⅡ 调用pll ip核的过程

ip核的选择

首先选择ip核,在右边的 IP-Catalog目录里输入PLL,选择ALTPLL,在工程文件夹下建立新的文件夹起名ipcore_dir存储该文件,在存储的时候就把ip核的名字起好

ip核参数的设置

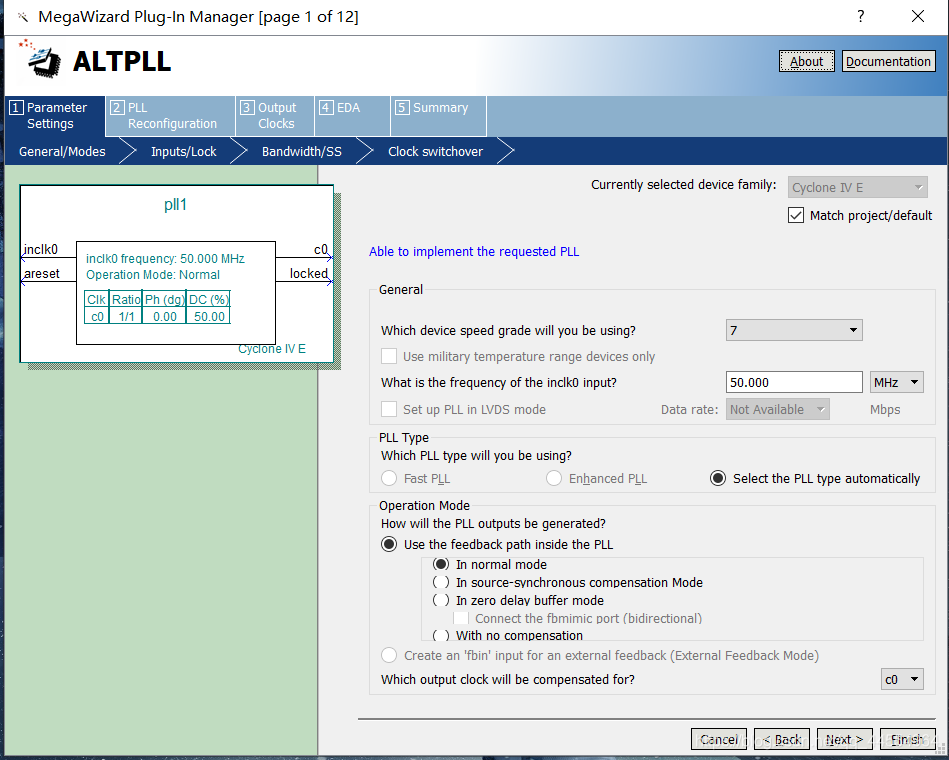

在第一部分parameter setting部分,device speed 就是根据你所选芯片的速度去选择,输入时钟频率根据要求去设置

模式的选择

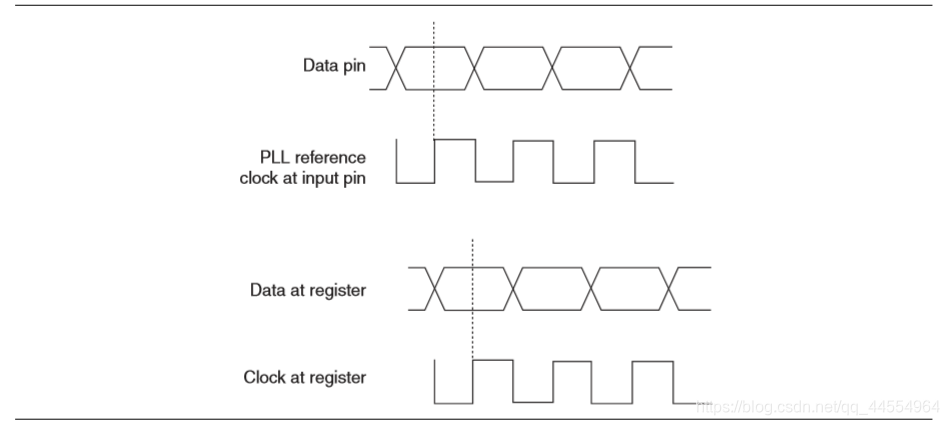

源补偿模式:是指在输入的时候输入时钟和输入数据是什么样的关系,那么在寄存器中时钟和数据还会保持同样的关系(原数据同步传输的时候就采用该模式)

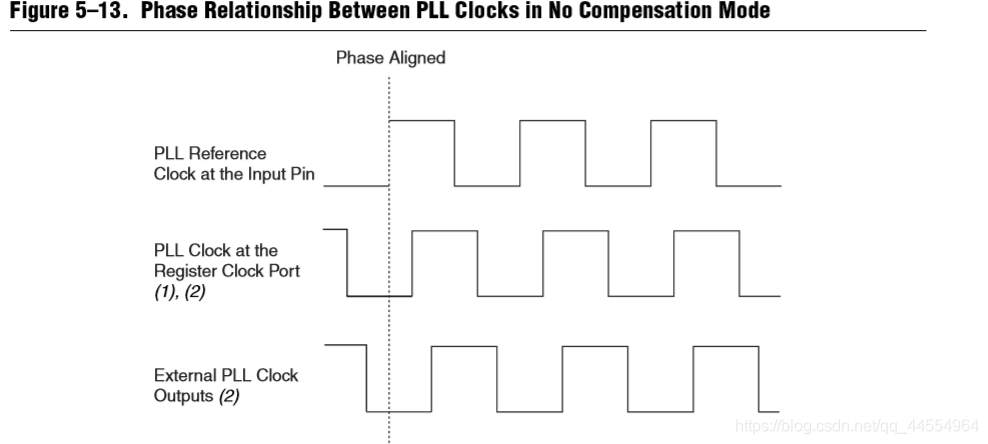

无补偿模式:是指在整个过程中不会实现补偿,其时钟该是多少延时就会有多少延时,该模式很少用

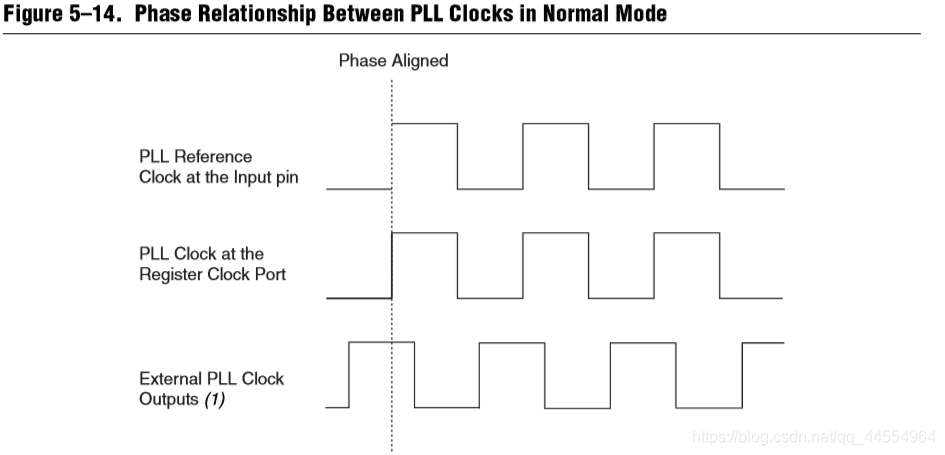

普通模式:是指在寄存器一端的时延和输入端口的时延是一致的,但是pll的输出端口确实包含时延的(如果用于内部寄存器就使用该模式)

0延时模式:输出时钟和我们的参考时钟一致(要想让输出的时钟和输入的时钟同相位,就采用这种模式)

这次是用于内部寄存器,所以选择normal模式就可以

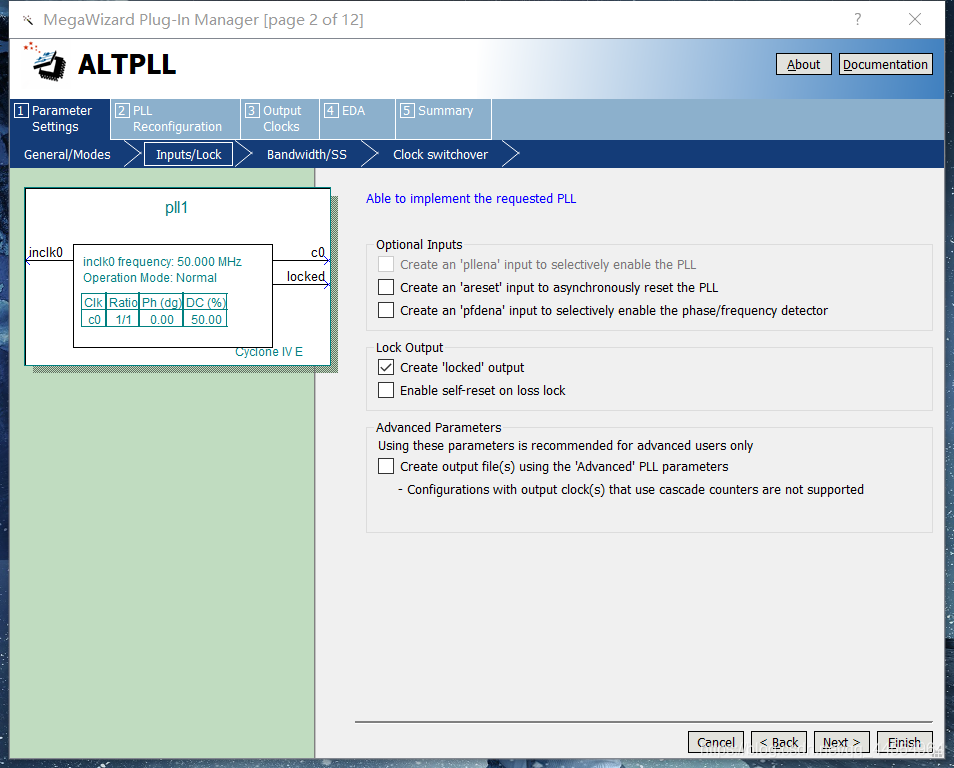

后续ip核参数设置

一般设置pll的时候,不要(异步复位)reset,加上整个端口不好控制;自动复位也不要加

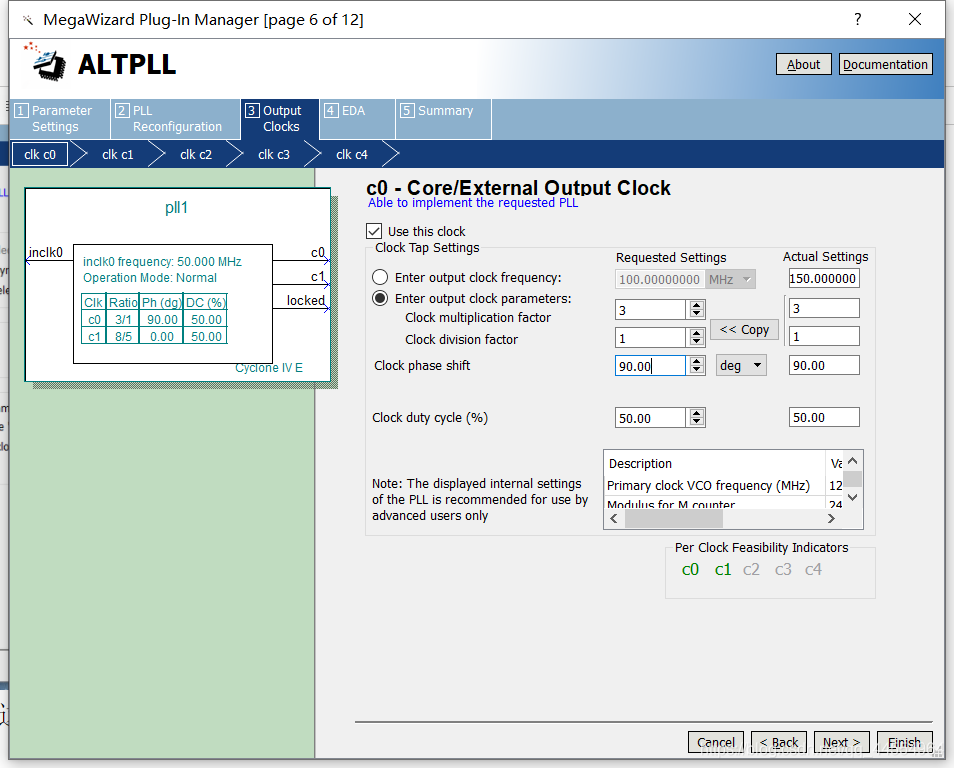

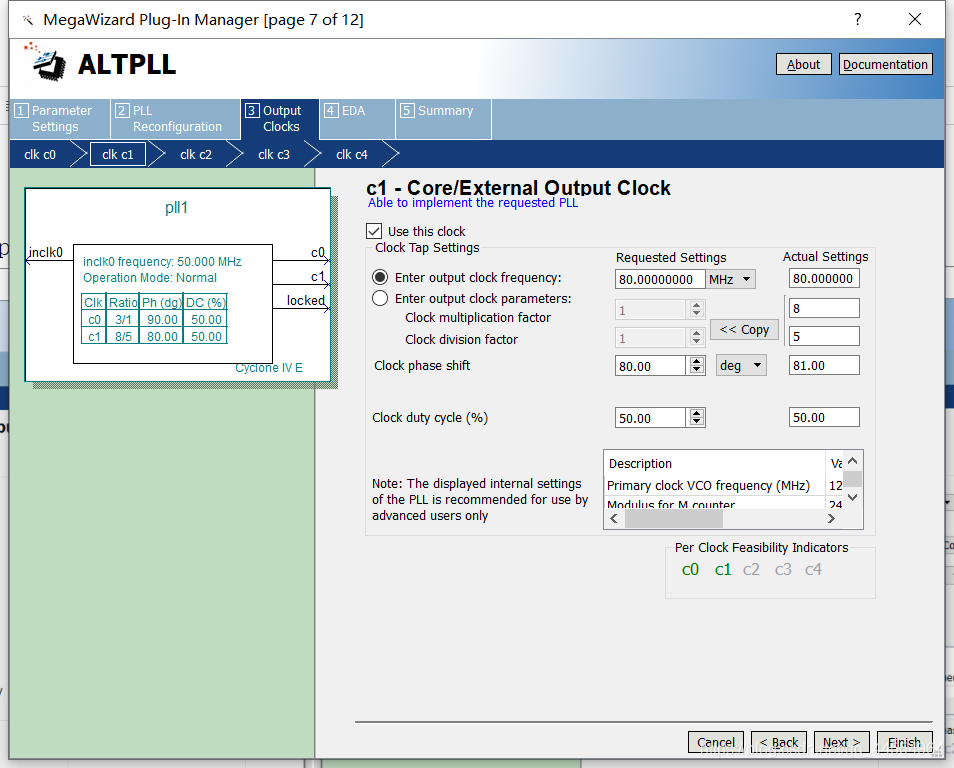

一直默认next,直到设置output clock,这个参数里面有五个时钟可以设置,每个的界面都是一样的,

clock multiplcation factor 是倍频参数

clock division factor 是分频参数

我们就可以通过设置这两个参数来实现我们需要的输出

phase division factor 是相移

clock duty shift 是占空比

除了设置分频倍频参数还可以在enter output clock frequency直接设置输出参数

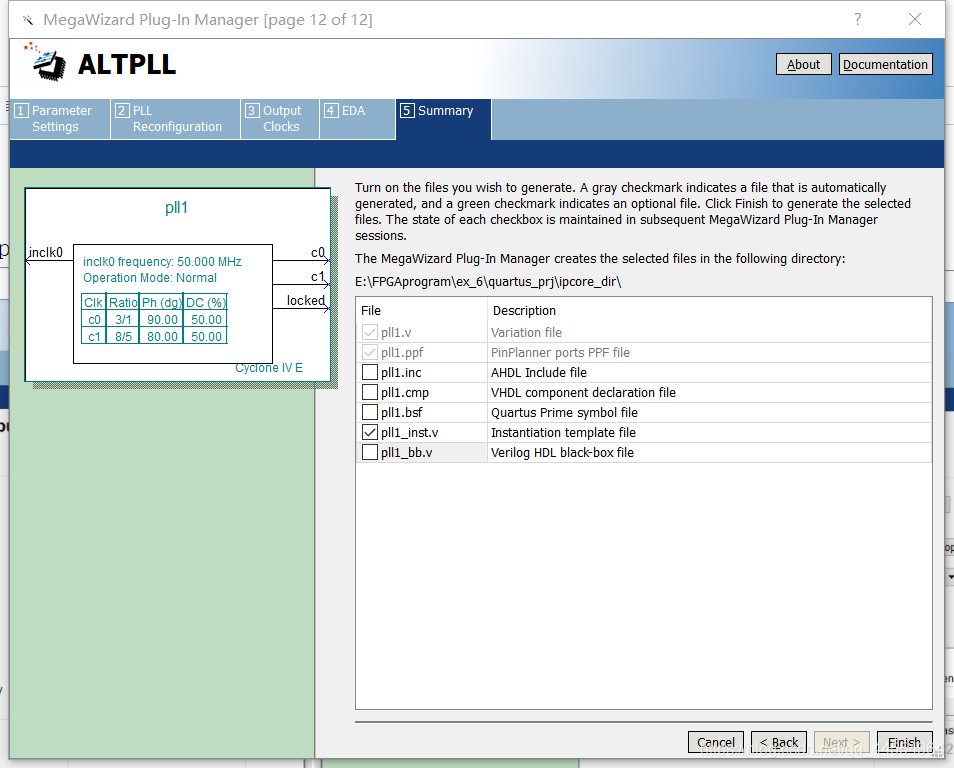

然后一直next 直到最后的summary,只要一个模板文件就可以

这时就可以看到在文件中就包含了ip核的文件,切记这里就是.qip文件,千万不能加成.v文件

编写.v文件、测试文件与do仿真文件

编写.v文件

然后把这个ip核例化到之前的顶层文件中去,具体的ip核是怎么定义的去看他的.v文件,或直接打开那个inst文件

module ex_ipcore(

input wire sclk,

output wire oclk1, //这里面输出变量定义为wire类型是因为,他要例化到后面的括号里面

output wire oclk2,

output wire locked

);

pll1 pll1_inst (

.inclk0 ( sclk ),

.c0 ( oclk1 ),

.c1 ( oclk2 ),

.locked ( locked )

);

endmodule

编写测试文件

`timescale 1ns/1ns

module tb_ex_ipcore;

reg sclk;

wire oclk1,oclk2,locked;

initial

begin

sclk = 0;

end

always #10 sclk = ~sclk;

ex_ipcore ex_ipcore_inst(

.sclk(sclk),

.oclk1(oclk1),

.oclk2(oclk2),

.locked(locked)

);

endmodule

编写do文件

编写do文件进行仿真,这里面需要对逻辑文件,ip核,ip核对应的库,测试文件四个文件进行编译,重点是要先找到这个库在哪里,找的方式为点击hierarchy下面的IP component 选择我们的IP核 双击,在ip核设置的EDA目录下就可以看到需要编译的库,然后在安装文件里找到对应的库,并把它复制到sim文件夹下,一般是在sim文件夹下在添加一个altera_lib文件夹,放到该文件夹下

quit -sim

.main clear

vlib ./work

vmap work ./work

vlog -work work ./tb_ex_ipcore.v

vlog -work work ./altera_lib/*.v

vlog -work work ./../design/*.v

vlog -work work ./../quartus_prj/ipcore_dir/pll1.v

vsim -voptargs=+acc work.tb_ex_ipcore

add wave tb_ex_ipcore/ex_ipcore_inst/*

run 1000ns

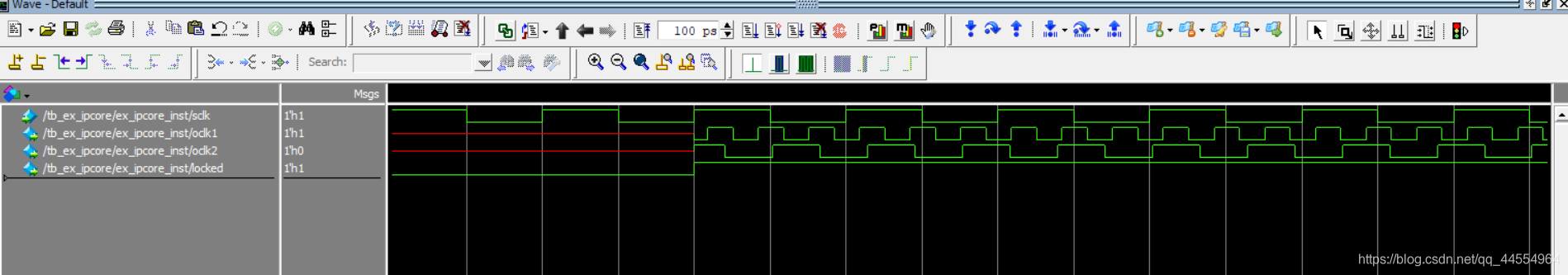

仿真结果

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?