Quad时钟块

最近在使用Kintex Ultrascale系列XCKU040做项目,其中用到JESD204B接口,硬件连接部分看的一直很迷糊,通过查阅手册收获了很多,现在开始记录一下

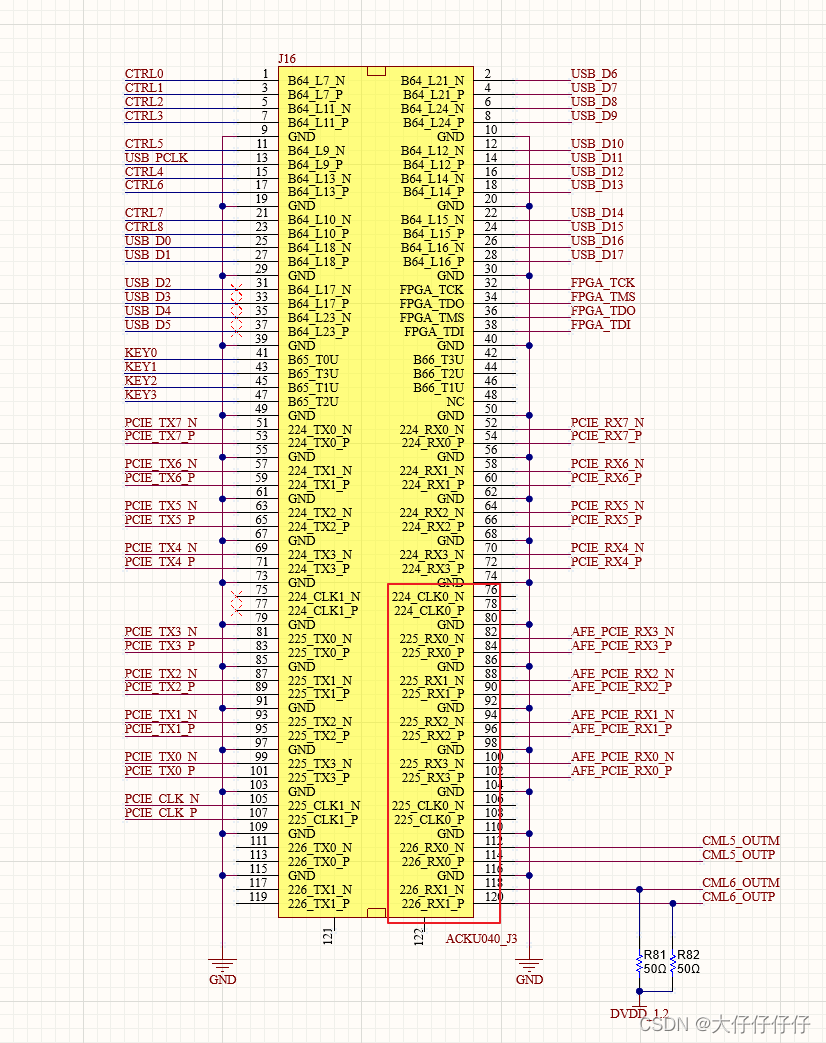

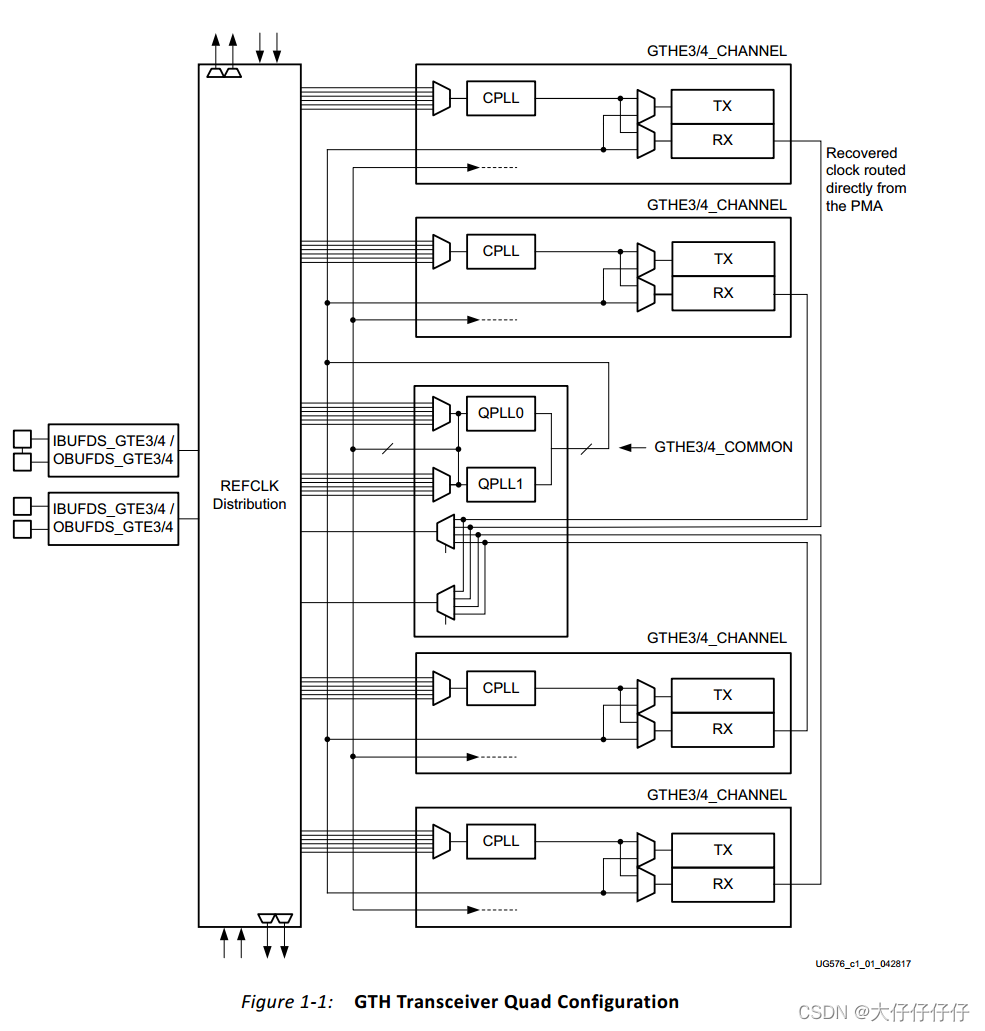

我们先从Quad讲起,Quad:4个GTX位1组,称为Quad,也就是如下图,我使用的XCKU040一共有五个Quad,共计20个高速收发器

由这个图我们不难看出,

Quad:

包含4个Channel(每个channel包含一个GTX),1个QPLL,2个差分输入参考时钟;

QPLL :

也就是一个Quad共用的PLL

Channel:每个channel就是一个GTX,包含一个CPLL和一对收发器;

CPLL : 每个Channel独有的PLL

CPLL最高支持线速6.6 G,而QPLL可更高;一般的,超过3.125G我们便推荐使用QPLL。在通道线速较大时,IP核会自动使用QPLL。

我们项目因为需要用到单个时钟驱动多个Quad,查阅手册可知,

本文详细解释了在使用XCKU040KintexUltrascale开发项目中,如何理解和利用Quad时钟块结构,包括GTX、QPLL和Channel的工作原理。重点讨论了时钟驱动多Quad的连接规则,以及高速收发器的AC耦合电容在信号传输中的作用和最佳实践,涉及LMK048时钟芯片的使用和接口匹配技巧。

本文详细解释了在使用XCKU040KintexUltrascale开发项目中,如何理解和利用Quad时钟块结构,包括GTX、QPLL和Channel的工作原理。重点讨论了时钟驱动多Quad的连接规则,以及高速收发器的AC耦合电容在信号传输中的作用和最佳实践,涉及LMK048时钟芯片的使用和接口匹配技巧。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1461

1461

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?