前言:之前我一直以为clock gating check只涉及AND/OR gate,直到前阵子后仿发现了min width pulse violation,才从后端口中了解到MUX作为gating cell也可以做clock gating check。TO后对此研究了一番,先把基本概念搞清楚放这儿,后面再写解决该violation的两个方法。

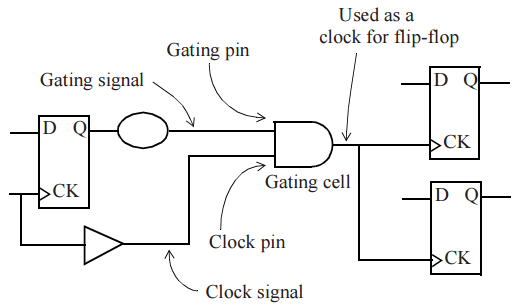

clock_gating_check是一种对ICG cell做timing check的约束,可以用户设置,也可由工具推断,目的是保证穿过ICG cell的clock没有glitch。

clock gating check可以分为active-high和active-low两种类型(指的是激活clock pin的gating pin的逻辑状态),gating cell是AND gate的clock gating check类型就是active-high type,OR gate对应的是active-low,另外还有复杂一些的gate,如XOR或MUX。

对于AND/OR gate clock gating check,一般可由工具推断,也就是STA会通过默认的约束要求,保证通过gating cell的时钟没有glitch。

如何做到的呢?STA会把所有的clock gating check归入一个path group,即clock_gating_default。以AND gate为例,会在clock pin为低电平期间检查gating pin跳变的时刻是否满足setup/hold。

需要说明的是,下图中驱动gating cell的SEQ cell可以是上升沿或下降沿触发,但下降沿触发对AND gate clock gating check的时序收敛更友好。(这里SEQ cell可以是DFF或Latch)。

理解了这点,也就理解了ICG stdcell为什么设计成fall edge Latch+AND gate或rise edge Latch+OR gate了。

对于XOR或MUX,clock gating check不会自动推断了,STA会报no clock gating check的warning,如果用户确认需要做check,那么可以用set_clock_gating_check的命令来做约束。

如果MUX是从I0切到I1,那么S就是由0变1,此时MUX作为gating cell,gating pin是S,clock pin是I1,属于active-high type;

如果MUX是从I1切到I0,那么S就是由1变0,此时MUX作为gating cell,gating pin是S,clock pin是I0,属于active-low type;

注意,MUX前级的reg通常是上升沿采样,如下图所示,hold是半周期check,timing比较难收敛。

6774

6774

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?