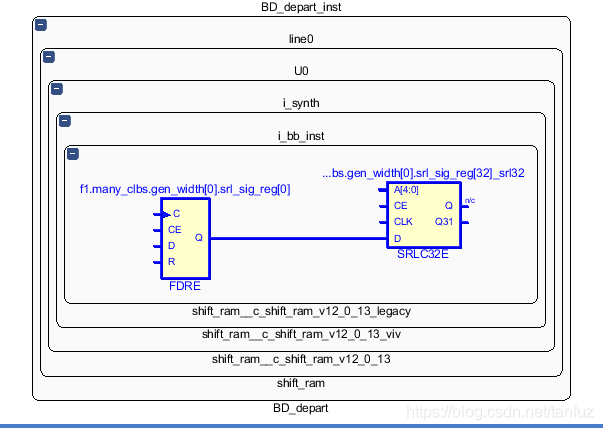

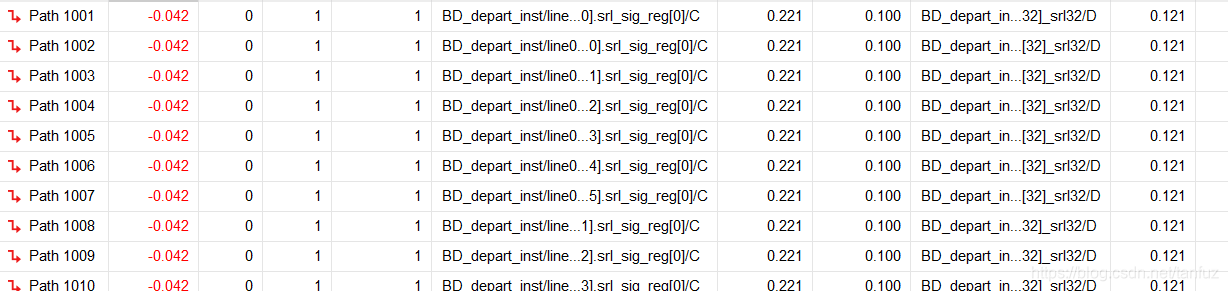

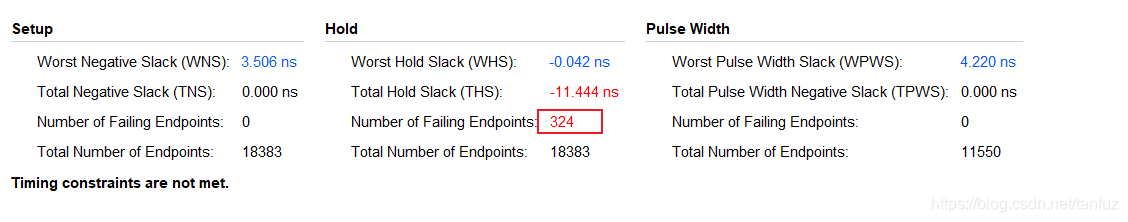

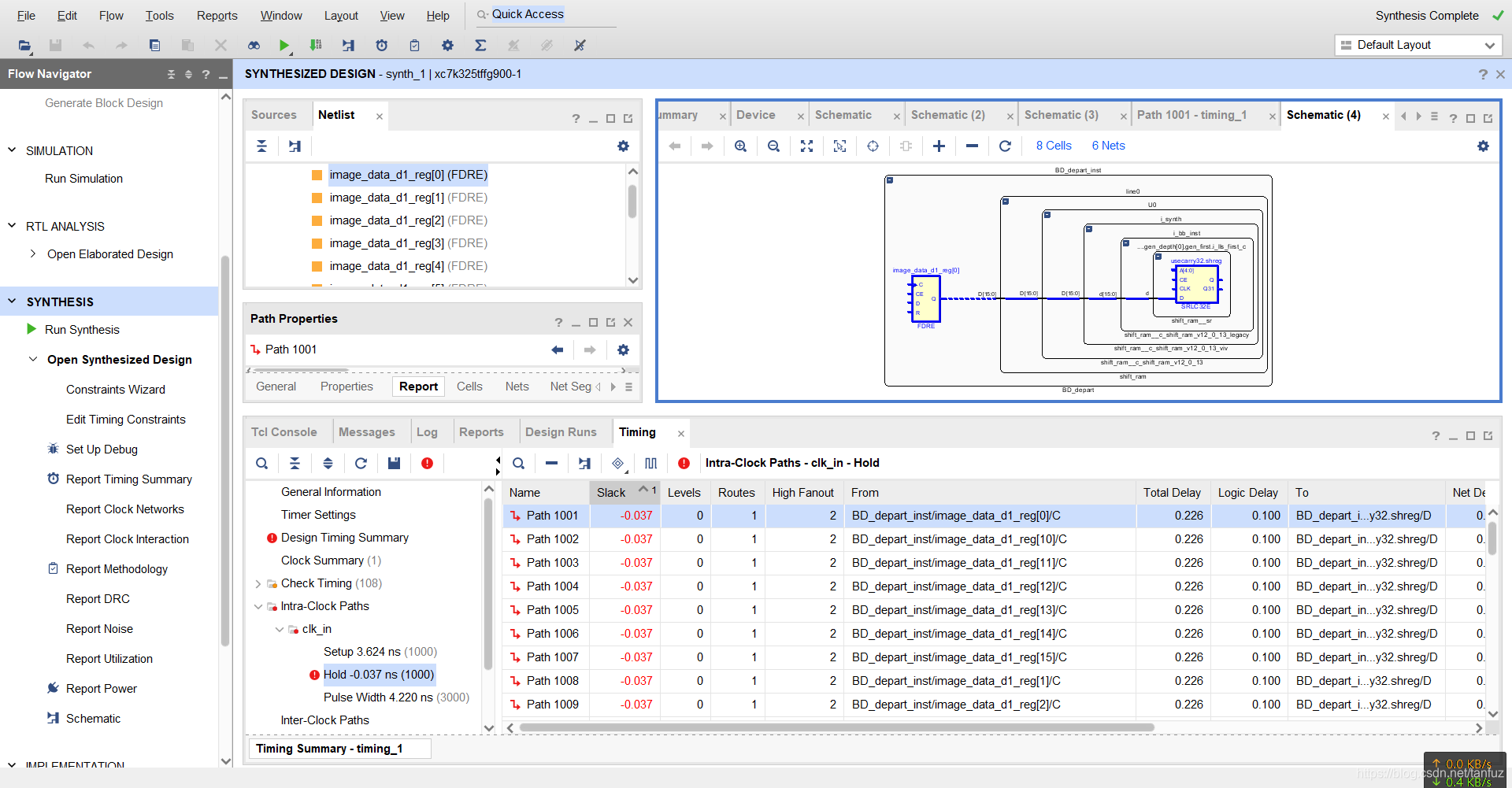

在项目设计中用到了shift_register,设计完成后发现时序问题出现在shift_register内部,如下图所示:

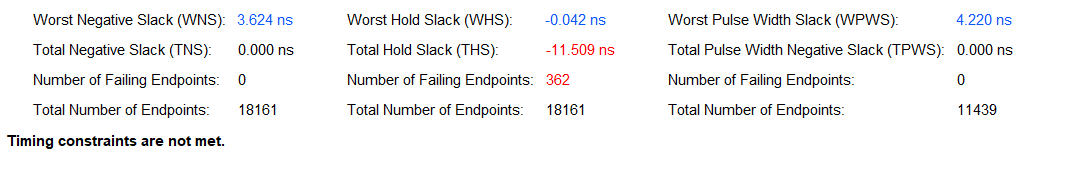

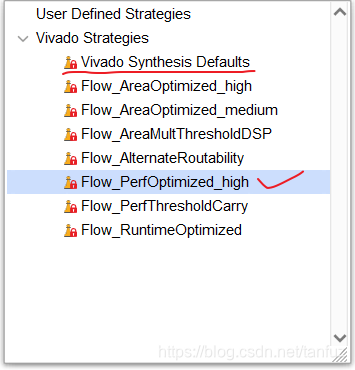

- 尝试将综合策略由默认改为性能最优

保持时间的时序问题由原来的362减少为324,但是仍然没有解决根本问题

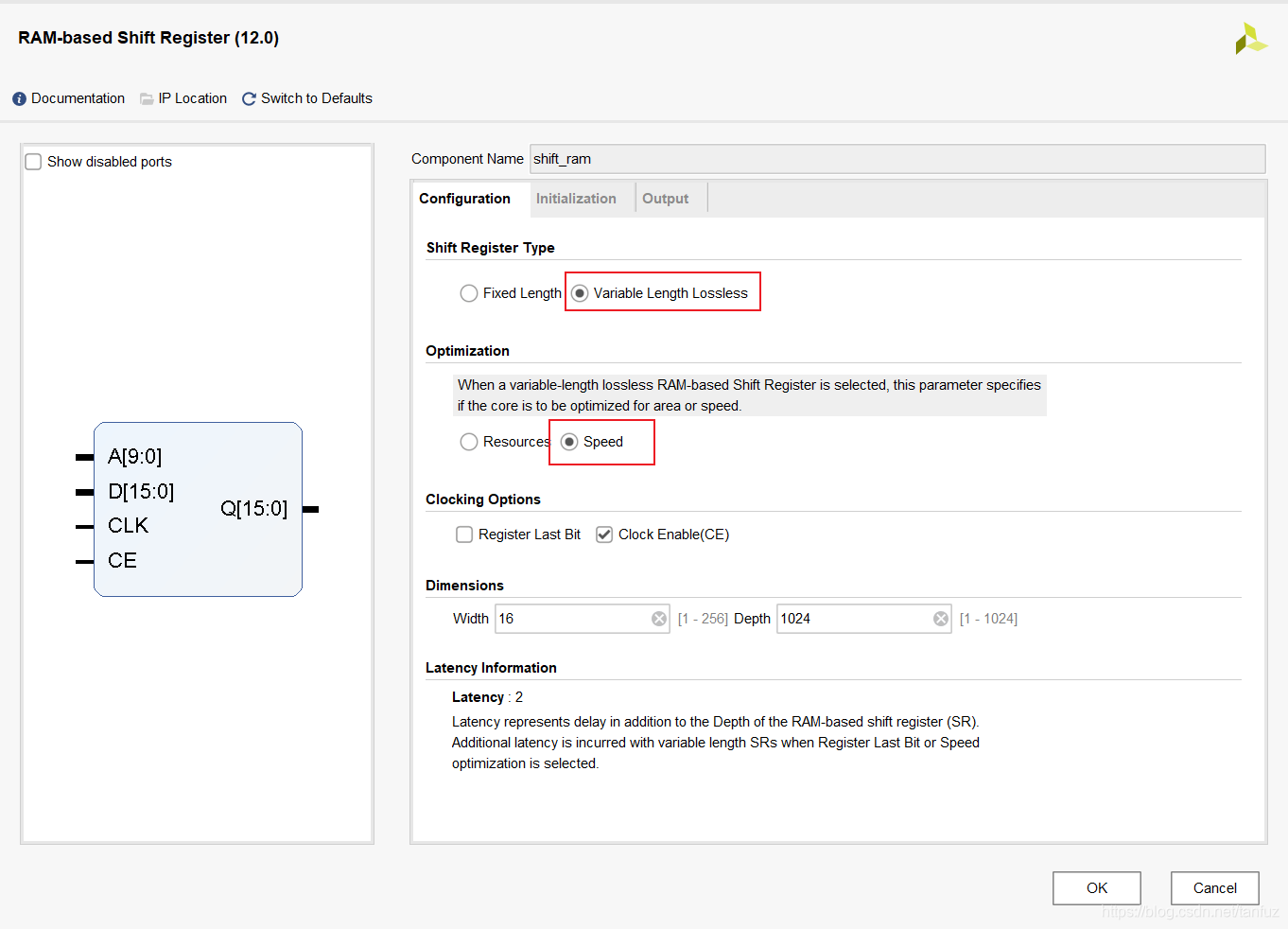

又对IP的设置进行了更改,由于上面的综合结果是选择Fixed length综合出来的,这个选项的Optimization只有Resource而没有Speed,因此,我将其改为了Variable length Lossless,然后选用Speed模式,下图是更改后的,

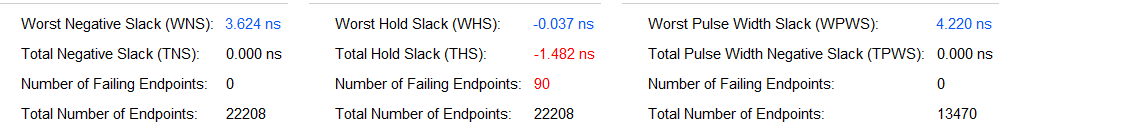

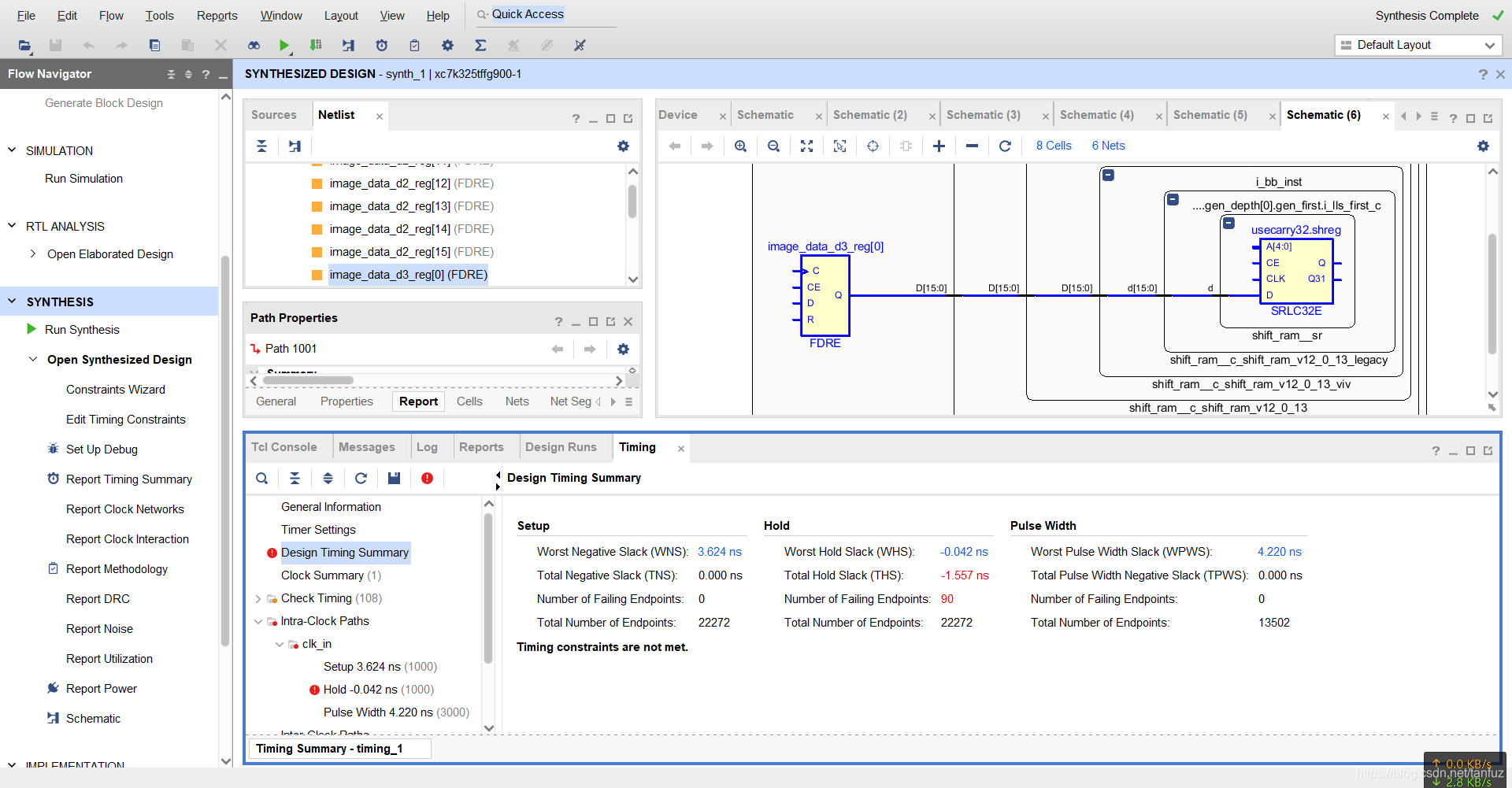

从下图可以看到时序违例由362个减少为了90个。

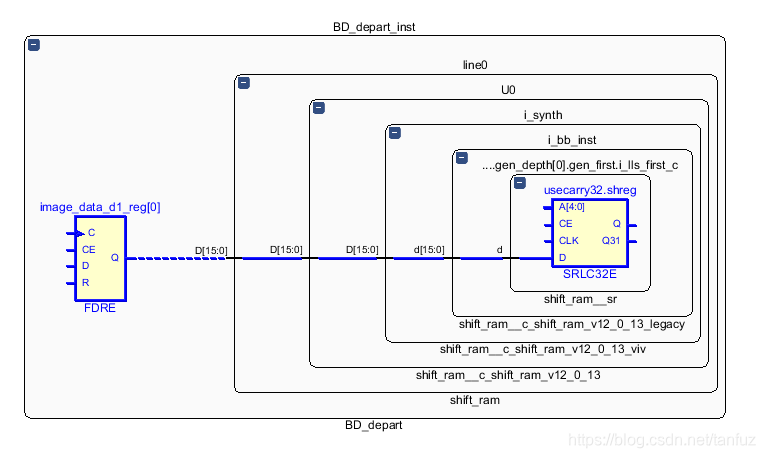

关键路径也由IP内部转变为了输入寄存器与IP之间:

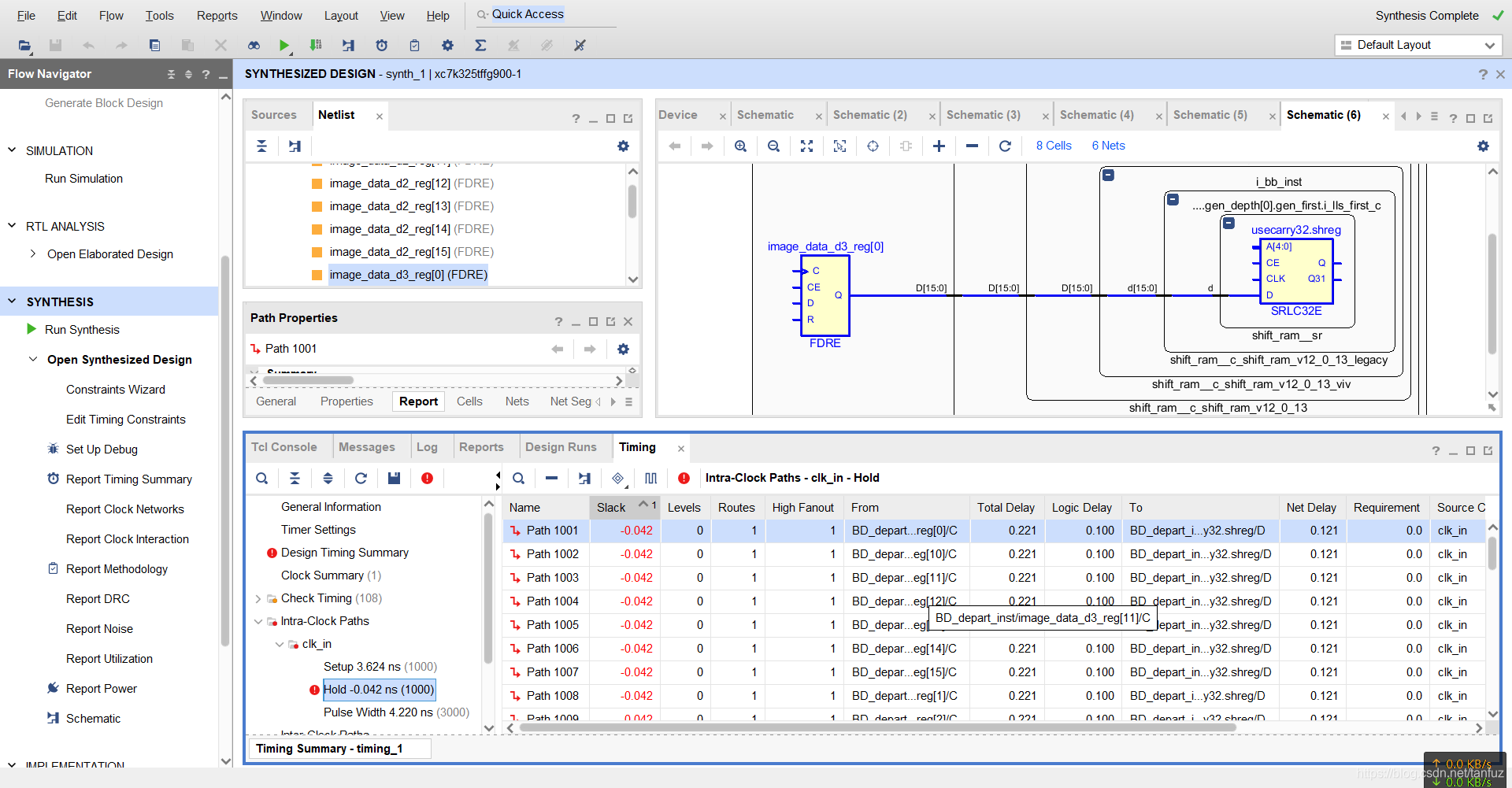

输入打3拍的结果,发现并无效果

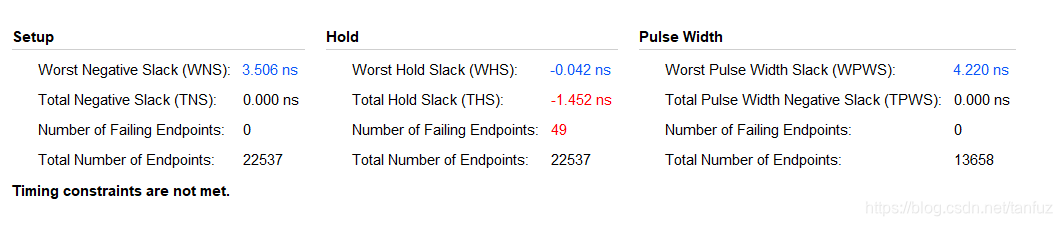

改变综合策略后,违例数量由90减少为49

在观察Netlist 网表信号时发现vivado综合工具将我的某些打拍信号给优化掉了,导致我打拍没有作用,因此在打拍信号前面加入

(* keep = "true" *)

(* keep = "true" *) reg [15:0] image_data_shift_out_d1;

(* keep = "true" *) reg [15:0] image_data_shift_out_d2;

(* keep = "true" *) reg [15:0] image_data_shift_out_d3;

(* keep = "true" *) reg [15:0] image_data_shift_out_d4;

(* keep = "true" *) reg [15:0] image_data_shift_out_d5;

(* keep = "true" *) reg [15:0] image_data_shift_out_d6;

(* keep = "true" *) reg [15:0] image_data_shift_out_d7;

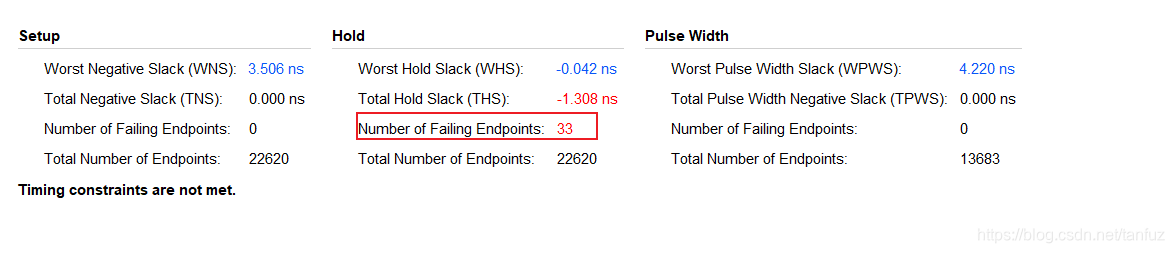

时序问题由49个再次减少为33个

剩下的问题主要是输入到shift_register IP时造成的时序违例问题,实在是改不动了,最终的解决方案为:参考下面的解决方案

解决方案参考3

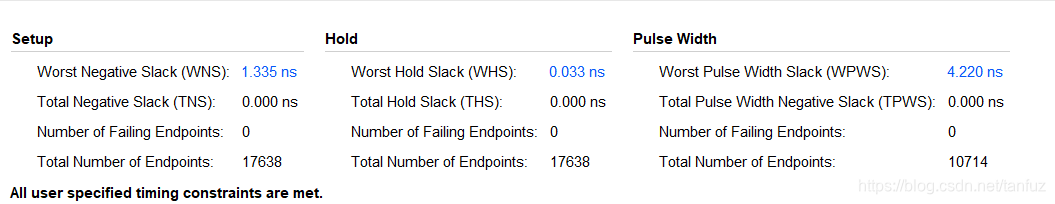

- 但你现在关注的这一点不是问题,这个hold error是综合后没有布局布线信息情况下的估算值,这一点点slack在implementation过程中基本工具就fix了。你的SDx工程最后实现的结果中,应该这些hold error都不存在了

- 如果是综合后的时序分析,请继续往下跑implementation。综合后只是估计值,此时逻辑的优化,布局布线还都未完成。估计结果来看,setup有很多余量,hold只是很小的违例,跑完implementation应该是可以满足的。

- 针对综合后的时序报告,对于同一个时钟域下的300ps 以下的hold time vioaltion 都可以暂时略过. (你目前就是这种情况)

implementation完成之后时序问题不存在了

本文详细讲述了在项目中遇到的shift_register时序问题,通过调整综合策略、设置变量长度、保持关键信号不变以及优化综合选项,逐步缩小违例数。最终通过实施阶段解决了实际时序问题。关键步骤包括解决资源优化与速度冲突,以及应对工具对打拍信号的优化调整。

本文详细讲述了在项目中遇到的shift_register时序问题,通过调整综合策略、设置变量长度、保持关键信号不变以及优化综合选项,逐步缩小违例数。最终通过实施阶段解决了实际时序问题。关键步骤包括解决资源优化与速度冲突,以及应对工具对打拍信号的优化调整。

729

729

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?