本文描述了如何使用Xilinx的Vivado Design Suite环境中的工具来定制和生成AXI Interconnect IP 核。Vivado Design Suite是一个强大的FPGA设计和开发环境,它允许用户定制和配置各种IP核以适应他们的特定设计需求。

以下是针对如何定制IP核的步骤的简要概述:

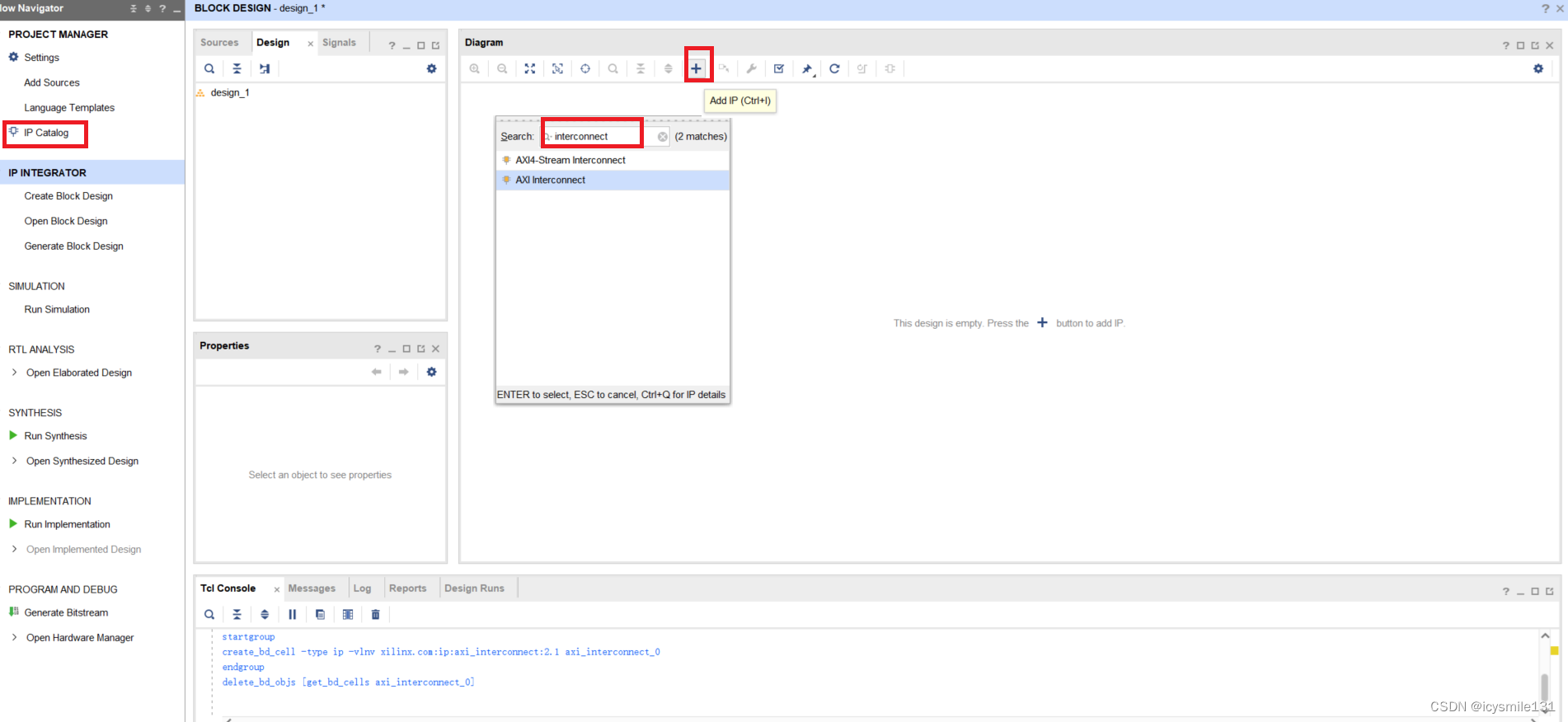

1. 从IP Catalog中或Diagram的“+”中选择IP。

2. 定制IP核

双击选择的IP核,或者从工具栏或右键菜单中选择“Customize Block”命令,打开IP核,开始设置与IP核相关的各种参数值。

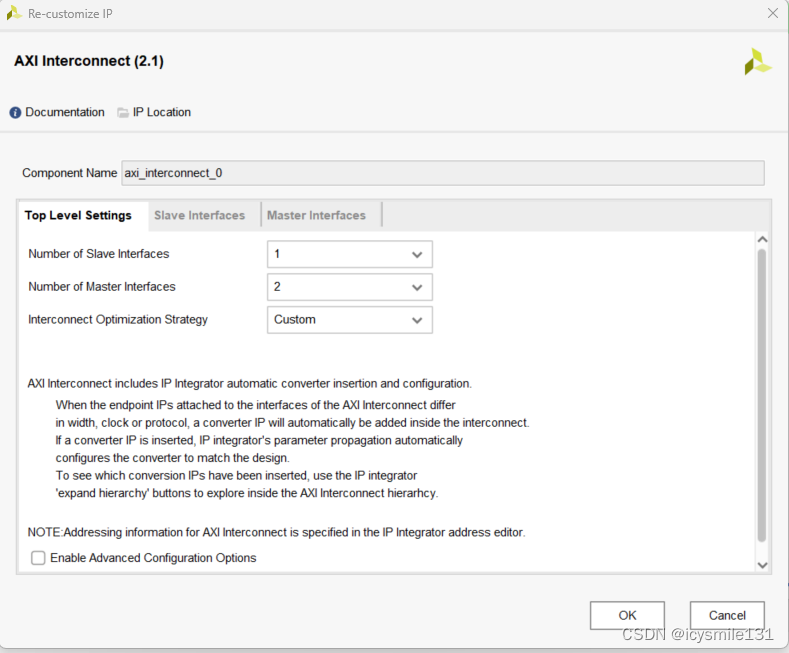

在Xilinx的Vivado Design Suite中,AXI Interconnect IP核的参数通常被分为几个类别,以便用户根据设计需求进行定制。

(1)Interconnect Optimization Strategy(互联优化策略)

(1)Interconnect Optimization Strategy(互联优化策略)

描述:

- 如果参数值设置为Custom(0),互联将根据其他配置页面中的参数设置进行配置。这意味着用户可以详细定制互联的行为和特性。

- 如果参数值设置为Minimize Area(1),将启用能够最小化互联实例中使用的基础设施IP核心(Infrastructure IP Cores)面积的特性。具体来说,互联内的交叉开关(Crossbar)将被配置为SASD(共享访问)模式,这种模式可以减少所需的硬件资源,从而减小面积。

- 如果参数值设置为Maximize Performance(2),将启用能够最大化互联实例中使用的基础设施IP核心性能的特性。具体来说,互联内的交叉开关将被配置为SAMD(交叉开关)模式,所有SI(Slave Interface,从接口)接口上都将启用包模式FIFO(First In First Out,先进先出队列),并且所有交叉开关的接受和发布阈值都将增加,以允许每个连接的主从设备之间进行多个未完成的事务。

格式/范围:

整数(0, 1, 2)

默认值:

0(Custom)

注意:

选择哪种优化策略取决于特定的应用需求和资源限制。如果需要节省FPGA的面积,可能会选择Minimize Area选项。如果需要最大化性能,尤其是在需要高带宽和低延迟的应用中,可能会选择Maximize Performance选项。而Custom选项则提供了最大的灵活性,允许用户根据具体需求进行定制。

(2)Number of Slave Interfaces(从接口数量)

从接口是用于接收数据或命令的接口。它们可能连接到其他设备或系统,并从那里接收信息。

- 格式/范围:整数(1-16)。这意味着从接口的数量可以是1到16之间的任何整数。

- 默认值:2。如果没有特殊设置,设备或系统将默认配置2个从接口。

(3)Number of Master Interfaces(主接口数量)

主接口则通常用于发送数据或命令。它们可能是设备或系统的主要通信点,用于与其他设备或系统进行交互。

- 格式/范围:这是一个条件性的范围。

- 当从接口数量为1时,主接口的数量可以是1到64之间的任何整数。

- 当从接口数量大于1时,主接口的数量可以是1到16之间的任何整数。

- 默认值:1。这意味着在没有特殊设置的情况下,设备或系统将默认配置1个主接口。

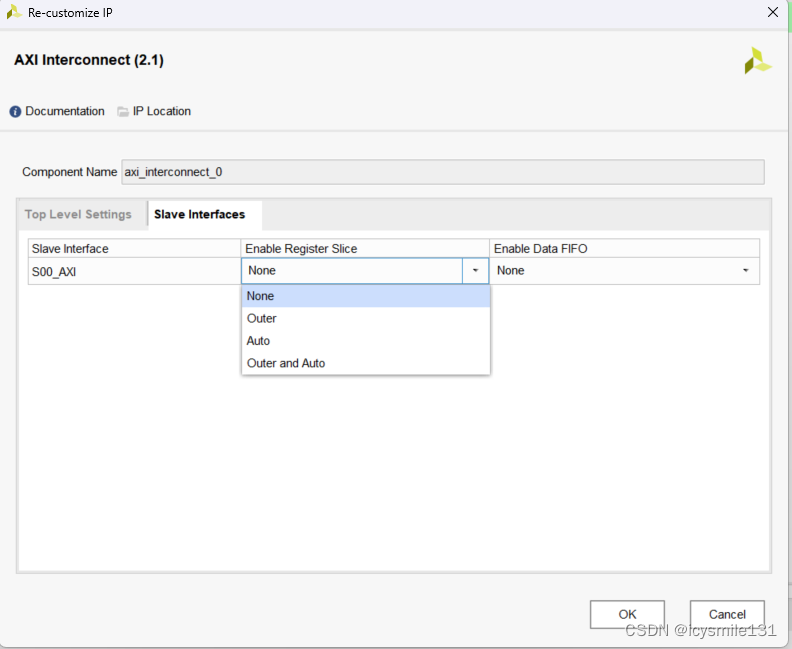

(4)Enable Register Slice

Enable Register Slice 是一个控制选项,用于在AXI接口上控制寄存器切片的插入。寄存器切片(Register Slice)通常用于解决时序问题,减少时钟域之间的延迟,并确保数据在跨时钟域传输时的正确性。

以下是关于Enable Register Slice选项的详细描述:

-

描述:控制是否在SI(可能是指某个特定的接口或模块,如Stream Interface或Slave Interface)上插入AXI寄存器切片。

-

选项:

None (0):不插入寄存器切片。Outer (1):在SI耦合器(coupler)单元层次的SI侧插入一个寄存器切片。这通常用于确保从外部接口到内部逻辑的数据同步。Auto (2):如果检测到具有共同时序路径的SI耦合器单元,则自动在SI耦合器单元层次中插入寄存器切片。Outer and Auto (3):在SI耦合器单元层次的SI侧插入一个寄存器切片,并且如果检测到具有共同时序路径的SI耦合器单元,则还可以插入额外的寄存器切片。

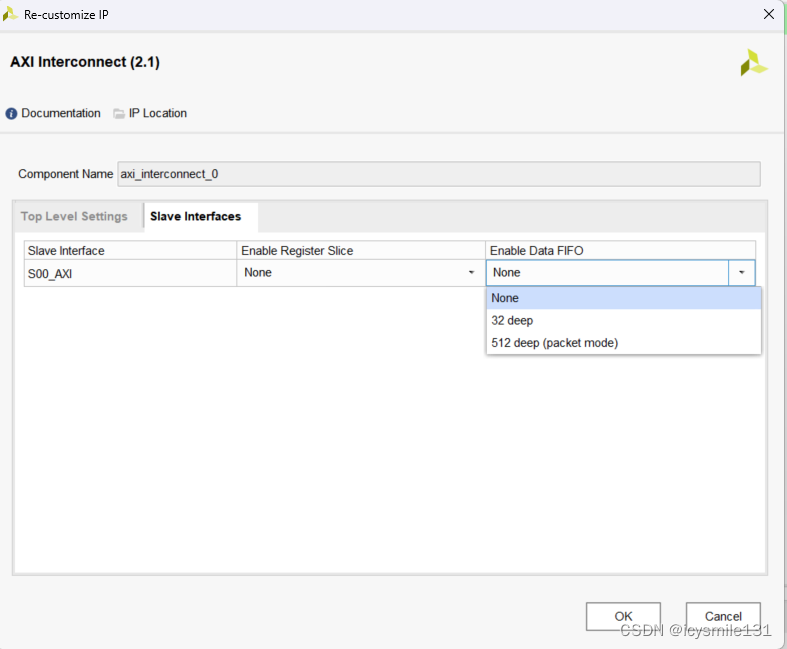

(5)Enable Data FIFO

描述:

这个参数控制是否在SI(可能是Slave Interface或某个特定的数据接口)上插入AXI数据FIFO(First-In-First-Out)缓存。数据FIFO在数字设计中用于处理不同模块之间的数据速率不匹配,或者用于平滑数据流的波动。

选项:

- 如果参数值为0,则不插入数据FIFO。

- 如果参数值为1,则插入一个深度为32的数据FIFO。

- 如果参数值为2,则插入一个深度为512的数据FIFO,并且启用其包模式(packet mode)特性。包模式通常用于处理以数据包为单位的数据流,其中每个数据包都有特定的开始和结束标记。

格式/范围:

- 参数为整数,可以取的值为0, 1, 或 2。

默认值:

- 默认不插入数据FIFO,即默认值为0。

使用场景:

- 当源和目的地的数据速率不一致时,可能需要插入数据FIFO来平衡数据速率。

- 如果数据流存在波动(例如,由于外部因素导致的延迟或抖动),数据FIFO可以平滑这些波动,确保数据能够稳定地传输到下一个模块。

- 在某些应用中,数据是以数据包的形式传输的,这时可能需要启用包模式特性来处理这些数据包。

注意:

- 插入数据FIFO会增加系统的复杂性和延迟,因此应根据具体的应用需求来权衡是否使用数据FIFO。

- 在选择数据FIFO的深度时,也需要根据应用的需求来确定。如果FIFO的深度过小,可能会导致数据溢出;如果FIFO的深度过大,可能会浪费硬件资源。

- 包模式特性可能需要根据具体的数据包格式和传输协议来配置,因此在使用前需要仔细阅读相关的文档或手册。

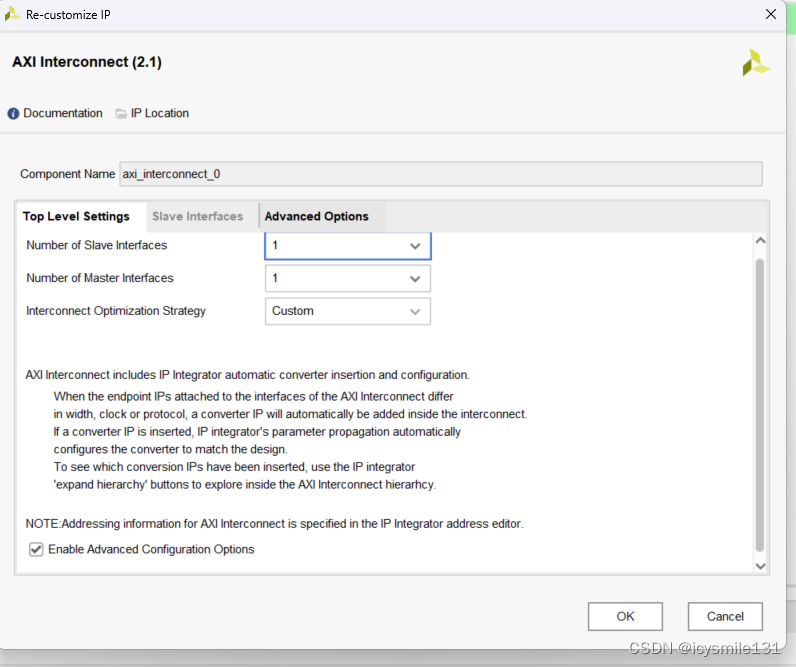

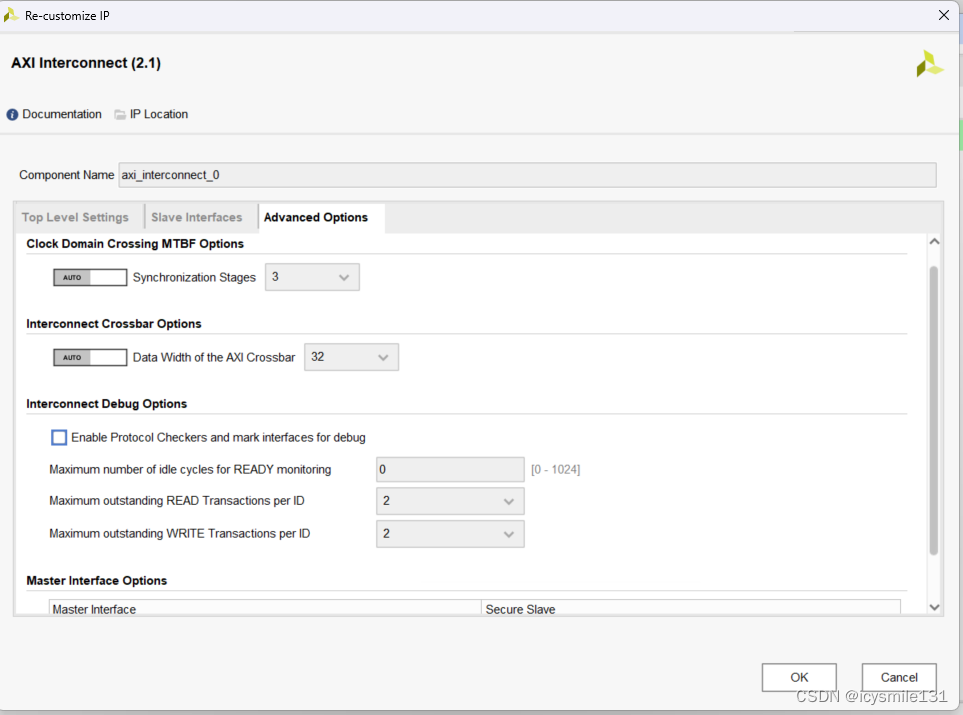

(6)Advanced Options

如果在Top Level Setting选项页选择了Enable Advanced Configuraiton Options,会出现Advanced Options选项页。

Clock Domain Crossing (CDC) MTBF Options 和 Synchronization Stages 在数字设计中涉及跨时钟域信号的处理。以下是对这些选项的详细解释:

① Clock Domain Crossing (CDC) MTBF Options:

MTBF (Mean Time Between Failures): 平均无故障工作时间,是衡量一个产品(尤其是电子产品)可靠性的指标。在数字设计中,特别是在跨时钟域信号传输时,MTBF可以衡量由于信号不同步或亚稳态等问题导致的故障之间的平均时间。

在跨时钟域设计中,由于时钟信号的不匹配或数据的不稳定传输,可能会出现数据错误或亚稳态。为了解决这些问题,可能需要使用多级同步器或FIFO(First-In-First-Out)缓冲区来确保数据的正确传输。

MTBF Options 可能涉及到如何配置这些同步器或FIFO,以最大化MTBF,即减少故障发生的频率。这可能包括选择同步器的数量、FIFO的深度和配置等。

② Synchronization Stages:

是指在AXI互联核心内实例化的任何异步时钟域转换耦合器所使用的同步阶段数量。

范围:整数(2-8)。这意味着可以配置从2到8个同步阶段。

默认值:2。即默认情况下,使用两个同步阶段。

在跨时钟域设计中,同步阶段用于确保信号在不同时钟域之间正确传输。通过增加同步阶段的数量,可以增加信号同步的可靠性,但也会增加延迟和硬件资源的使用。

每个同步阶段可能包括一个或多个寄存器,用于缓存和稳定跨时钟域的信号。通过多个阶段的缓存和比较,可以减少由于时钟不匹配或数据不稳定导致的错误。

在Interconnect Crossbar的选项中,关于AXI Crossbar的数据宽度(Data Width)是一个重要的参数。当您手动指定这个值时,它会覆盖AXI互联实例内AXI Crossbar的DATA_WIDTH参数的任何IP集成器自动设置值。

具体来说,AXI Crossbar的数据宽度决定了它一次可以处理的数据位数。例如,如果数据宽度设置为32位,那么AXI Crossbar一次可以处理32位的数据。这个参数对于系统的性能和效率有重要影响,因为它直接决定了数据传输的带宽和速度。

当勾选Enable Protocol Checkers and mark interfaces for debug时,AXI协议检查器IP核会在AXI互联核内部实例化,并与每个启用的AXI主接口(Master Interface)和AXI从接口(Slave Interface)连接。此外,每个AXI互联核的AXI接口也会被标记为用于调试。这样做的好处是可以在运行时监控和检查AXI接口的数据传输是否符合AXI协议规范,有助于发现潜在的问题并进行调试。

① Maximum number of idle cycles for READY monitoring:

这个参数指定了在所有启用的协议检查器中,READY监控的最大空闲周期数。当AXI接口处于空闲状态时,如果READY信号保持低电平的时间超过了这个设定的周期数,那么协议检查器就会报告一个错误。这个参数的设置可以根据具体的系统需求来调整。

②Maximum READ Transactions per ID 和 Maximum Write Transactions per ID:

这两个参数分别指定了每个ID的最大未完成的读事务和写事务数量。在AXI协议中,每个读或写事务都会有一个唯一的ID用于标识。如果某个ID的未完成事务数量超过了这两个参数设定的值,那么协议检查器就会报告一个错误。这有助于防止因为事务堆积而导致的系统性能下降或资源耗尽。

这个选项指示每个主接口(MI)插槽是否连接到安全的从设备(需要TrustZone安全访问)。TrustZone是一种硬件级别的安全机制,可以在同一颗处理器上创建两个独立的执行环境:一个用于执行安全的代码(如操作系统、支付应用等),另一个用于执行非安全的代码(如普通应用、游戏等)。如果启用了这个选项,那么主接口只能与具有TrustZone安全访问权限的从设备通信。

Slave Interface Options - Arbitration Priority:

当启用了多个从接口(SI)时(即NUM_SI > 1),这个选项可以为每个启用的从接口在AXI交叉开关(Crossbar)上分配一个仲裁优先级。仲裁优先级决定了在多个从接口同时请求访问主接口时,哪个从接口的请求会被优先处理。这个参数的设置可以根据具体的系统需求和性能要求来调整。

2583

2583

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?