1.编码方式:

不同于 NRZ 编码,PCIe 6.0 采用 PAM4 编码方式

NRZ,不归零调制(Non-Return-to-Zero),是PCIe 1.0至PCIe 5.0所采用的调制方式。在新一代的PCIe 6.0中,并未采用传统的NRZ,而是采用了PAM4调制,即四电平脉冲幅度调制(Pulse Amplitude Modulation 4-levels)。

如上图所示的对比可以看出,NRZ只有0,1两个电平,形成一个眼,而PAM4会有0,1,2,3共4个电平,形成了3个眼。所以PAM4每个符号能携带2个bit的信息,比NRZ每个符号只能携带1个bit信息,传输能力提高了一倍。

PCIe 6.0的调制改为PAM4还有另一个优势的地方,就是传输64GT/s的速率,依然可以和PCIe 5.0的奈奎斯特频率(Nyquist Frequency)保持一致,而通道IL从PCIe 5.0的36 dB变为了PCIe 6.0的32 dB,所以这从另一个角度来看,PAM4还有助于降低通道的损耗。从以上图4可知,PAM4的4个电平(Level0,1,2,3)进行格雷编码(Gray Coding),4个电平对应的格雷编码分别是00,01,11,10,格雷编码的方式是要求相邻符号,每次只能变化一位,且首尾符号也只是变化一位,这样的编码方式可以有效改善误码率。PAM4信号里还定义了4个电平的DC Balance Values,以满足直流平衡设计需求。另外,虽然PCIe 6.0采用了PAM4的调制,但PCIe 6.0依然向下兼容之前所有版本的速率。

2.DOE

2.1 说明

在PCI Express® Base Specification Revision 6.0中,数据对象交换(Data Object Exchange,DOE)是一种可选机制,允许系统固件/软件与功能(Function)或根复合块(Root Complex Read/Write Block,RCRB)之间进行数据对象的交换。软件通过数据对象交换 (DOE) 扩展能力发现 DOE 支持。因为 DOE 依赖于配置请求,所以它不能直接用于Functions间的peer-to-peer操作,尽管系统软件可以提供一种机制来在Functions之间中继数据对象,如果这样的话能力是需要的。当 DOE 在 RCRB 中实现时,允许通过实现特定的方式阻止peer-to-peer操作。

2.1.1 DOE的主要要素:

可选机制:DOE作为系统固件/软件的可选功能,可以帮助它与Functions进行数据交互。

通过配置请求发现:DOE的支持通过配置请求(Configuration Requests)进行发现,这使得在功能之间无法直接进行点对点的操作。虽然系统软件可以中介这个过程以便在功能间转发数据对象。

实现灵活性:DOE可以在RCRB中实现,并且允许在多种功能类型中实现。它可以在一个功能或RCRB中实现多次。

相关协议的指定范围:使用数据对象的协议必须指定它在相关功能中的适用范围。

非D0状态使用:尽管DOE协议可以在非D0状态下使用,特定数据对象协议可以限制在非D0状态下的操作。

2.1.2 应用场景:

固件/软件与硬件的通信:DOE可以用于系统固件/软件与PCIe功能之间交换配置信息、状态更新、性能指标等,是实现高效通信的重要手段。

数据对象的传递与管理:在系统中允许通过DOE来传递特定的数据对象,能够支持多种协议的互操作性,尤其是在复杂的多功能设备中。

为组件测量和认证提供支持:DOE是系统固件/软件访问组件测量和认证(CMA)所需支持的先决条件,后者基于SPDM(安全产品数据管理)。

解决悬挂事务的问题:在进行功能级重置(Function-Level Reset, FLR)时,DOE的使用有助于处理可能导致数据损坏的悬挂事务,保证数据的完整性与系统的稳定性。

特定协议的需求:在某些情况下,特定协议可能要求功能实现一个唯一的DOE实例,这样可以确保数据交换的安全和规范。

3.FEC (Forward Error Correction)机制

前向纠错(FEC, Forward Error Correction)是一种通过在发送的数据中增加冗余信息来实现数据纠错和恢复的技术。具体的FEC处理流程通常包括以下几个步骤:

- 数据分块:将待发送的数据流分成若干个块(通常称为码块),每个块在后续步骤中将被处理以生成冗余信息。

- 编码:对每个数据块应用特定的编码算法,生成冗余码。常见的FEC编码算法包括汉明码、里德-所罗门码、低密度奇偶检查码(LDPC)等。编码过程中会根据所需的纠错能力生成相应数量的冗余码字。

- 数据发送:将原始数据块和生成的冗余码一起发送到接收端。接收方将接收到的数据流进行处理,包括这部分冗余码。

- 接收和数据块重建:在接收端,接收到的数据块和冗余码会被分离,并存储起来。

- 解码:接收端根据冗余码进行解码。这个过程在一定的错误条件下能识别和纠正错误。若接收到的符号包含错误,FEC解码算法能够通过冗余信息恢复原始数据。

- 数据组合和输出:解码后的数据会被重新组合成完整的数据流,并输出到上层应用或服务。

4.L0p新的接口/低功耗状态

4.1 L0p的引入

PCIe 5.0中低功耗状态有:L0s,L1、动态链路宽度切换、速度切换。L0p是PCIe 6.0新引入的一种低功耗状态,工作在L0p状态下PCIe设备可以在不中断数据发送的情况下完成链路宽度切换,从而提升链路的带宽利用率、降低功耗。

0p在LTSSM中的位置如图1所示,其不是LTSSM主状态之一,L0p其实也是L0的一部分

4.2 L0p的目的和意义

● Flit Mode只支持L0p。PCIe 6.0工作在Flit Mode时不支持L0s,转而采用L0p。

● 采用L0p时,不中断数据传输即可实现链路宽度切换。非Flit Mode下,或没有L0p时,调整链路宽度需要LTSSM从L0 -> Recovery -> Configuration,此间几us内数据流被中断。

● L0p下被关掉的lane的功耗与L0s几无差别,这样一来,既能保证链路的带宽率利用率,也能链路降低功耗。

● 上调链路宽度从L0p回退到L0时,PHY无需重新训练。

4.3 L0p的适用范围

L0p适用于工作在Flit Mode的PCIe设备,是一项可选的功能,PCIe设备可以通过设备控制寄存器3的L0p Enable位(图2)来决定是否开始L0p功能。对于采用PCIe 6.0的Retimer,其端口必须支持L0p。

L0p 的宽度是对称的。支持 L0p 的端口必须支持所有合法宽度(x1、x2、x4、x8、x16),直至配置的链路宽度。当链路处于 L0p 时,每个方向至少有一个通道必须处于活动状态。仅在 LinkUp=0b 的 Configuration.Complete 状态下协商 L0p 支持。

4.4 L0p Ack和Nak规则

◦ 如果未设置 L0p.Priority,即L0p,Priority为0 ,则允许端口拒绝接受 L0p 请求,以获得比当前宽度更低的宽度。

◦ 如果端口由于热节流或可靠性原因而请求减小链路宽度,则应在 L0p 请求中设置 L0p.Priority。如果链路伙伴未请求更改 L0p 宽度或将在下一个 Flit 中请求更改 L0p 宽度,则必须确认优先级 L0p 请求,该请求必须在 100 纳秒内显示在发送器引脚中,并在 L0p 请求中设置 L0p.Priority。

◦ 任何请求减小链路宽度并从其链路伙伴收到 Ack 的端口最终负责在基本条件不再禁止链路以全宽运行时发起增大请求。

◦ 如果两个端口同时请求链路宽度更改,则适用以下规则来确定哪个请求获胜。

▪ 如果两个请求都设置了 L0p.Priority,则宽度较低的请求获胜。

▪ 如果一个请求设置了 L0p.Priority,则它获胜

▪ 如果双方均未设置 L0p.Priority:

▪ 宽度较高的请求获胜;否则,如果双方请求的宽度相同,则下游端口获胜

◦ 如果未设置 L0p.Priority,则端口可以拒绝比当前 L0p 宽度更低的宽度请求。

◦ 进入恢复状态将导致链接达到其配置的最大宽度。

5.PCIe Flit Mode

5.1 Flit 组成

从协议来看PCIe 6.0 Flit 由 236B TLP + 6BDLP+ 8B CRC + 6B ECC 共 256B 组成,在物理层的逻辑子层进行 Flit 打包及解包(Packing / Unpacking),以及latency 优化的half-flit mode。

Flit Mode 时不再使用 STP、SDP、END 等 Packet Marker 及 Frame Token。

从 Flit Size 看,目前(PCIe 6.0)仅支持 256B 固定长度的 Flit。

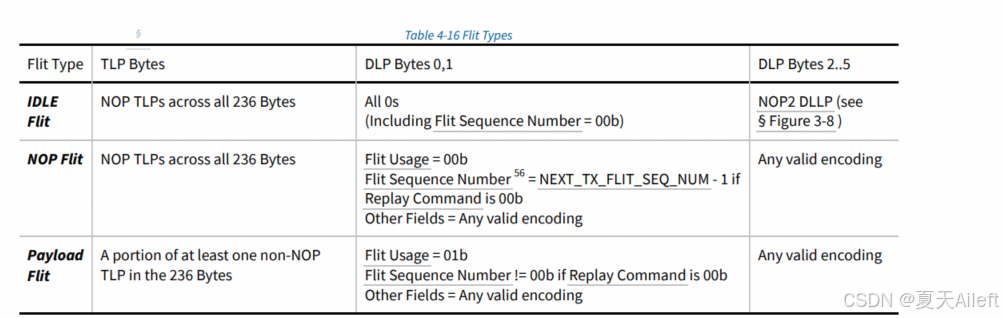

按照 Flit Type 分类,Flit Mode 支持 3 中 Flit,分别为 Idle Flit、NOP Flit 及 Payload Flit。

- IDLE Flit: ○ 描述: IDLE Flit是一种特殊的Flit,表示在链路上没有有效的数据传输。它用于保持链路的活跃状态,防止链路进入空闲状态。 ○ 内容: NOP

TLPs(无操作传输层包)填充整个236字节(bytes)数据字符,内容是全0(二进制形式为00b)。 ○ 用途:

用于保持链路的活跃并避免空闲。- NOP Flit: ○ 描述: NOP Flit也包含NOP TLPs,但与IDLE Flit不同的是,它在特定条件下使用,通常用于信号传输和流量控制。 ○ 内容: 同样填充了整个236字节的NOP

TLPs,但在DLP(Data Link Protocol)字节中,Flit Usage字段设置为00b。 ○ 用途:

主要用于流量控制和信号处理,它携带比IDLE Flit更多的信息。- Payload Flit: ○ 描述: Payload Flit是包含至少一个非NOP TLP的数据包。它用于实际的数据传输。 ○ 内容: 其内容包含有效有效负载数据,而不是全0或NOP TLPs。DLP字节中的Flit Usage字段设置为01b。 ○ 用途:

主要用于传输有效的数据和信息,是PCIe协议进行通信的主要数据单位。

由于flit mode,而增加的内容:

● Completer_Segment[7:0] Flit Mode 时,用以指示 Conpleter 所在的 Hierarchy,位于 OHC-A5 中。

● Destination_Segment[7:0] Flit Mode 时,用以指示 ID 路由的 TLP 的 Detination 所在的 Hierarchy,位于 OHC-A3/A4/A5 中。

● DSV[0:0] Destination Segment Valid,出现于 Flit Mode。

● Requester_Segment[7:0] Flit Mode 时,用以指示 Requester 所在的 Hierarchy,位于 OHC-C 中。

● RSV[0:0] Requester Segment Valid,出现于 Flit Mode。

● AMA[2:0] ATS Memory Attributes,出现于 Flit Mode,为优化 Memory 或 Cache 性能提供 Hints。

● AV[0:0] AMA Valid,出现于 Flit Mode,用以指示 AMA 字段是否有效。

● HV[1:0] Hints Valid,出现于 Flit Mode,用以指示 PH 及 ST 相关字段是否有效。

● PASID[19:0] Process Address Space ID,跟 Requester ID 一起作为 Request TLP 渎职空间的唯一标识。Non-Flit Mode 时位于 TLP Prefix 中,Flit Mode 时位于 OHC 文本中。

● PV[0:0] PASID Valid,用于 Flit Mode。

● OHC[4:0] Orthogonal Header Content,正交头内容,用以来指示其后是否存在 OHC、是何种 OHC,是 PCIe Flit Mode 下新加的一个 TLP 字段。

● 取消了 Fmt,合并到 Type,Type 种类更多。

● 新加了 TS (Trailer Size),用来指示 Trailer Size。目前,TS=000b 时表示没有 Trailer,TS=001b 时表示当前 TLP 包含 1DW 的 ECRC。OHC-C 时,TS=101b 指示 3DW IDE MAC,TS=110 指示 4DW IDE MAC 及 PCRC。其他的预留。

● TLP Prefix 相关内容合并到 OHC 中,通过 OHC 来指示。

● 预留了 Suffix 后缀。

● InitFC1 DLLPs for VCx增加了 InitFC1-P [Shared] (fourth)、InitFC1-NP [Shared] (fifth)、 InitFC1-Cpl [Shared] (sixth),initFC2也是一样

5.2 Flit Packing流程

先从 Transaction Layer 及 Data Link Layer 拿到待传输的 TLP 及 DLLP 并按一定规则填充到 TLP Bytes 及 DLP Bytes,然后基于 236B TLP Bytes 及 6B DLP Bytes 计算出 8B CRC,最后三者作为输入计算出 6B ECC。至此,完整的 Flit 打包完毕。

5.3 Flit UnPacking流程

接收端与发送端类似,只是方向相反。在将 PAM4 电压转换为 2 位对齐量后,如果适用,它会进行接收端预编码,然后解码格雷码,如果适用,则在单比特级别进行解扰。数据流 (Flit) 在所有通道上聚合,并进行 FEC 解码和校正,然后进行 CRC 校验,然后发送事务和数据链路有效负载。

Rx Pins: 接收引脚(Rx Pins)是接收数据的输入点。它接收通过通道传输的信号,并将其传送到下游的数据处理链路。

PAM-4 电压转换 (PAM-4 Voltage Conversion to 2-bit aligned): 首先,接收到的信号将被转换为PAM-4编码所定义的电压电平。从PAM-4编码中,接收到的电压信号将被解码为相应的比特流,通常是2比特的对齐格式。

Rx Precoding: 这是一个用于改善信号质量的重要步骤。通过对接收到的信号进行预编码,可以降低信号失真的可能性,以提高传输的可靠性。

Gray Code 解码 (Gray Code Decoding - 2-bit aligned): 在接收过程中,数据流将通过格雷码解码器。格雷码是一种二进制编码形式,当数值有变化时,只有一个比特改变,有助于降低在数据转换过程中的错误率。此处会将解码后的数据进行2比特对齐。

去散列 (Descrambling): 数据在传输过程中可能会被打乱,因此需要通过去散列过程恢复数据的原始顺序。这个过程通常涉及一种算法,用于对数据流进行逆散列处理。

TSO OS (Transport Segmentation Offload Ordered Set) 或 预编码禁用 (Precoding Disabled): 在这些步骤中,系统决定是否应用传输分段卸载(TSO)以及有序集合(Ordered Sets)的处理。这是为了确保数据完整性和传输的顺序。

未打乱的有序集合 (Symbols of Ordered Sets or Patterns that were scrambled): 在数据流中,可能包含特定的有序集合或模式,即使它们已经被打乱后仍然具有特定含义。这些集合会被重新识别并处理,以确保数据的完整性。

Lane N-1 和 Lane 0: 类似的处理流程适用于所有接收通道(Lane),具体的实现步骤可能会因通道数量和具体的硬件架构而有所不同。

CRC生成 (CRC Generation): 在数据流的接收和处理过程中,会进行循环冗余校验(CRC)生成,以确保数据的完整性和准确性。CRC用于检测传输过程中的错误。

FEC: ECC字节生成 (FEC: ECC Bytes Generation): 纠错编码(Error Correction Code, ECC)用于对接收的数据进行额外的纠错处理,避免数据因噪声和干扰而导致的错误。

TLP(Transaction Layer Packet): 最终的数据包以事务层包的形式组装,包含了用户有效载荷的数据(例如,事务ID、数据长度等信息)。

6.Data Object Exchange (DOE)

Data Object Exchange (DOE) 是一种可选机制,允许系统固件/软件与功能或根复合设备(RCRB)之间进行数据对象交换。通过数据对象交换,系统软件可以更高效地与 PCIe 设备进行交互。以下是对 DOE 内容的解释及其作用的总结:

6.1 DOE 的功能和工作机制

- 可选支持:

○ DOE 是一种可选接口,意味着设备制造商可以选择实现该功能,而不是必须实现。 - 发现 DOE 支持:

○ 软件可以通过“数据对象交换扩展能力结构”来发现是否支持 DOE。这给系统固件提供了一种方式来识别和利用 DOE。 - 操作限制:

○ DOE 依赖于配置请求,因此它不能直接用于功能间的点对点操作。系统软件可以在需要时提供机制来在功能间中继数据对象,但这些都是间接的。 - 对 CMA 的要求:

○ DOE 是实现系统固件/软件通过配置请求进行组件测量和认证(CMA)访问的前提。这一过程建立在 SPDM(安全与可用性数据管理)之上。 - 灵活实现:

○ DOE 允许在任何类型的功能或 RCRB 中实施,尽管并非所有协议都必须适用于所有功能。一个功能或 RCRB 中可以实现多个 DOE 实例。 - 协议作用域:

○ 使用数据对象的协议必须指明其作用范围,例如协议是仅与功能自身相关还是与多功能设备中的特定功能相关。 - 多实例支持:

○ 协议可以要求功能为特定协议实现 DOE 的独立实例,或者允许共享 DOE 实例给一定的协议集。 - 非 D0 状态下的使用:

○ 虽然 DOE 可以在非 D0 状态下使用,但某些特定数据对象协议可能会限制在非 D0 状态下的操作。

6.2 DOE 的作用

- 数据交换:

○ DOE 提供了一种标准化的方法来交换数据对象,使系统固件可以与 PCIe 设备高效通信。 - 支持高级功能:

○ DOE 为实现如 CMA 等高级功能提供了基础,增强了系统对设备的管理能力。 - 灵活性和可扩展性:

○ DOE 的设计允许在多种设备和协议中实现灵活性,使得设备制造商可以根据需求定制实现。 - 增强互操作性:

○ DOE 定义了在多功能设备中的数据对象使用的范围,确保不同协议和功能之间的互操作性。

6.3 DOE Operation - 请求/响应协议与数据对象

● 请求/响应结构:DOE协议支持请求/响应类型的交互,例如CMA)。请求/响应协议是指一个实体(如主设备)发出请求后,另一个实体(如函数或设备)必须在合理的时间内返回相应的响应。

● 非请求/响应结构:除了请求/响应结构,DOE也允许其他类型的数据对象协议,例如可能的单向通知或广播这些。 - 协议操作的约束

● 数据对象协议需要自行限制其操作,以确保正确性和避免潜在的破坏性操作。例如,如果一个响应在没有对应请求的情况下被生成,这可能会导致数据混乱或错误。 - 响应时间要求

● 一旦接收到数据对象,DOE实例必须在1秒内完成处理,并在需要响应的情况下生成响应。此时,应该在DOE状态寄存器中设置数据对象就绪位(Data Object Ready bit)。

● 如果在1秒内无法完成这些操作,必须在同一时间段内设置DOE错误位(DOE Error bit)。

● 一旦系统固件或软件设置了DOE中止位(DOE Abort bit),DOE实例必须在1秒内清除数据对象就绪位(如果未清除)和DOE错误位(如果已设置)。 - 数据对象缓冲要求

● 数据对象的缓冲要求由支持的数据对象协议决定,协议必须明确规定最大数据对象的大小,以确保不会超出规定的边界。 - DOE中止位的可靠性

● 强烈建议实现确保DOE中止位功能的鲁棒性,意味着即使设备固件出现故障,该功能仍然应该得到维护。这是为了在出现问题时能够及时安全地终止操作,避免进一步的不稳定。 - FLR(功能级重置)处理

● 对功能的FLR将导致任何正在进行的DOE传输被中止。数据对象协议需要指定FLR的处理方式,以及其他影响数据对象协议的条件。

● FLR不一定会导致内部处理引擎的重置,这意味着设备可以在不完全重置的情况下恢复正常操作。 - DOE错误的定义

● DOE错误主要指DOE操作中的错误,而不包括与数据对象协议相关的错误。必须触发DOE错误位的事件包括:

○ 对任何DOE寄存器进行污染性配置写入(Poisoned Configuration Write)。

○ 写数据邮箱机制的溢出(Overflow)。

○ 读数据邮箱机制的缺失(Underflow)。

○ 如果相关的数据对象协议没有提供替代机制,转移与预期长度不符的数据对象。

2666

2666

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?