三、 ram based shift register

3.1 概述

顾名思义,对输入的数据进行延时

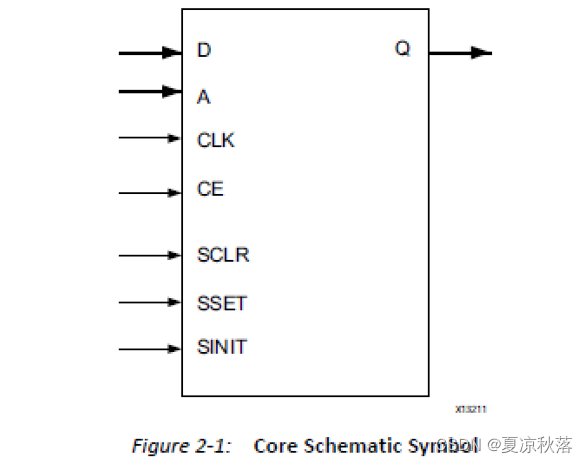

3.2 端口说明

3.3 ip核的生成

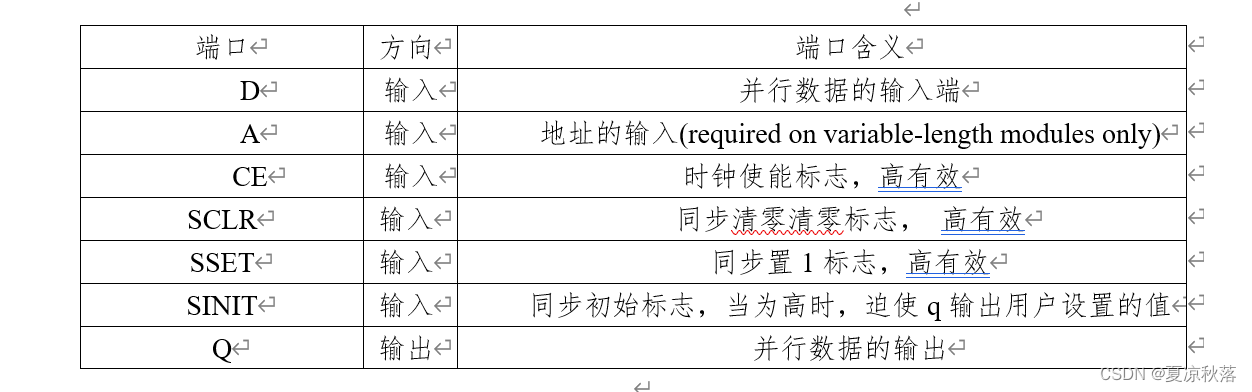

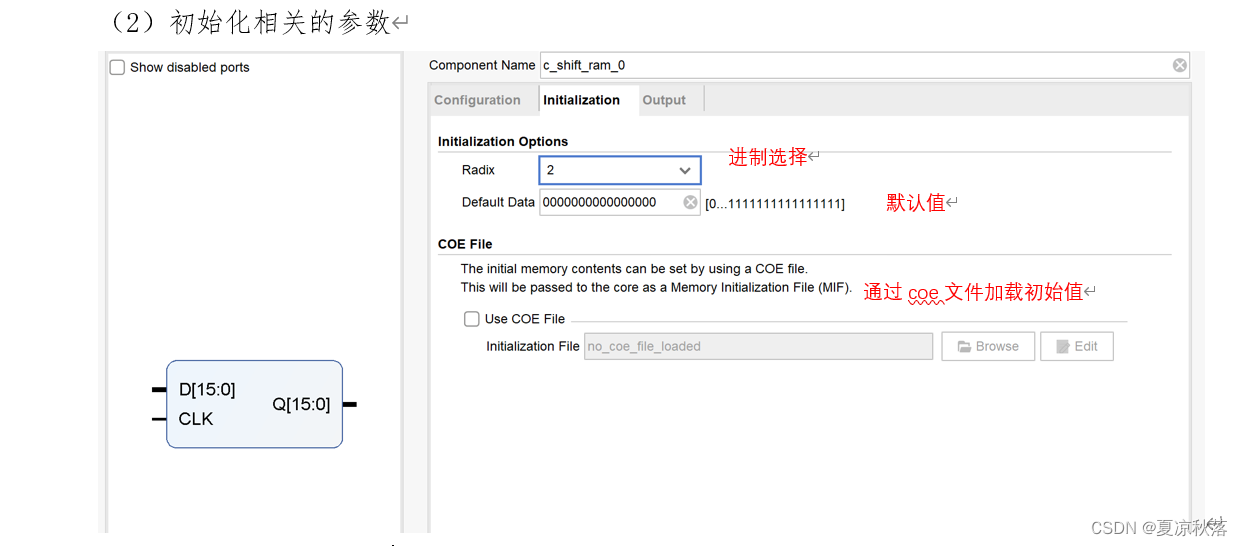

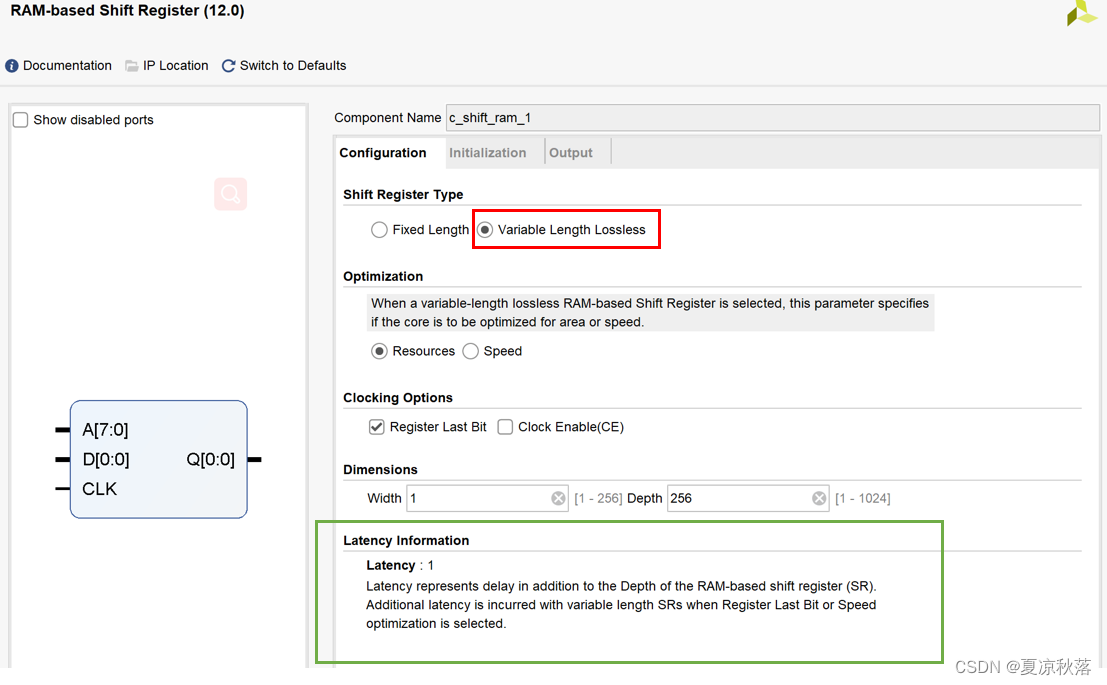

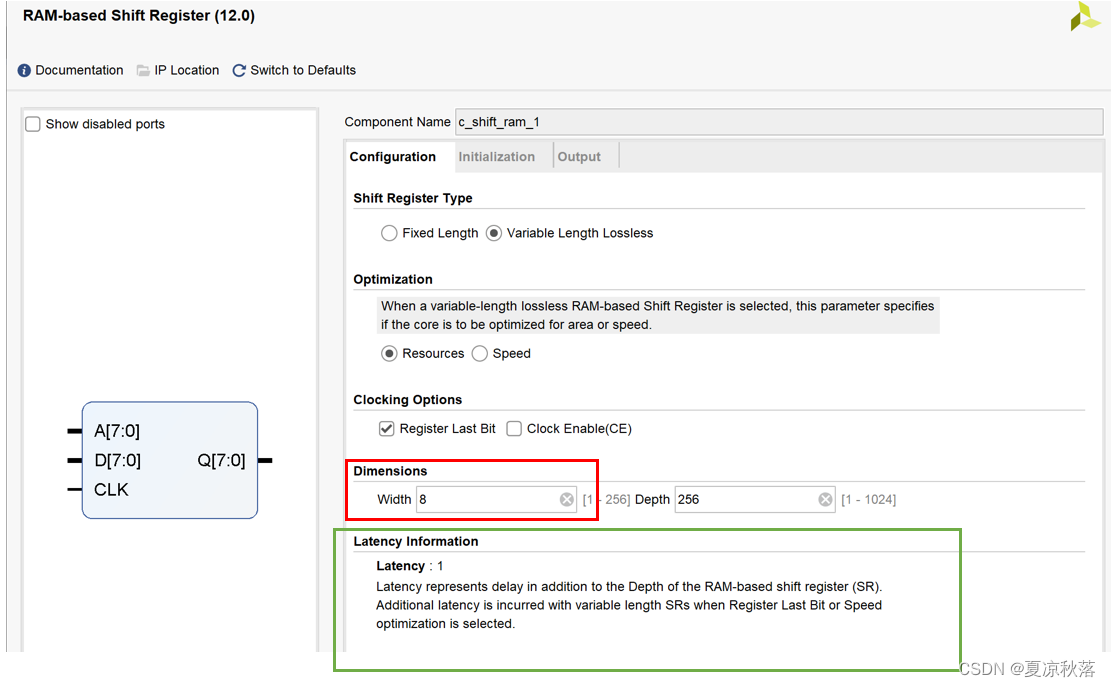

(1)configuration 选项的配置(本次width选1,depth选8)

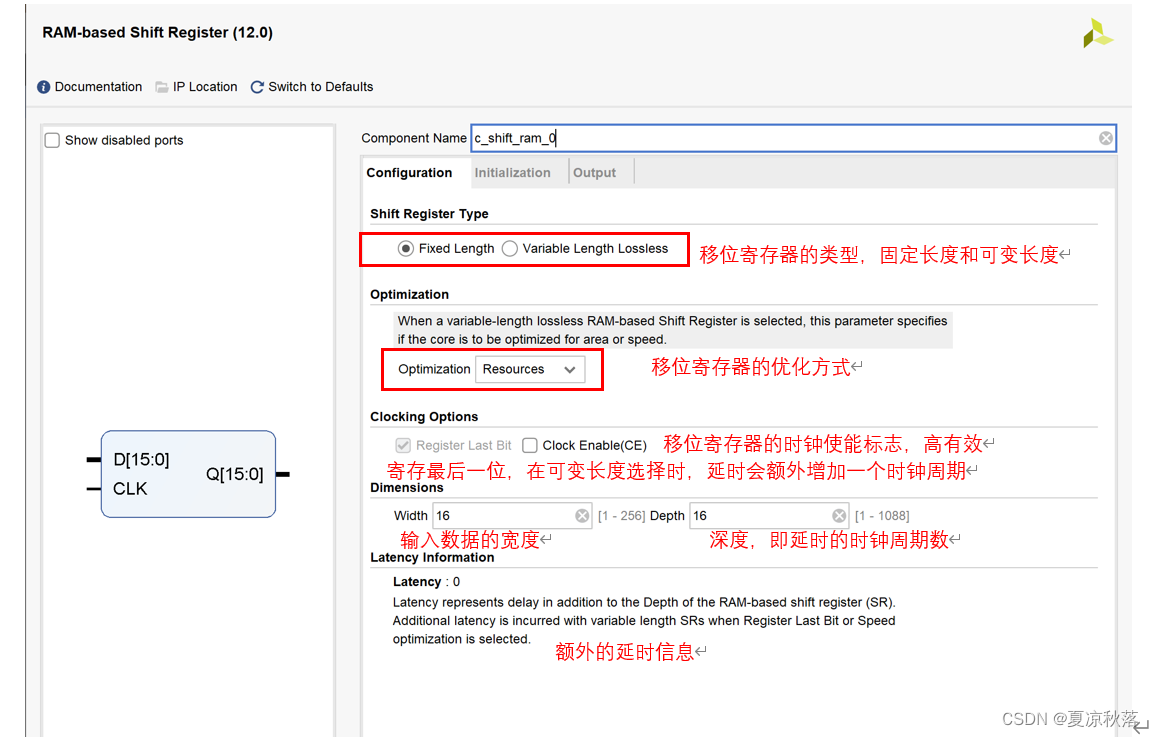

(2)初始化相关的参数

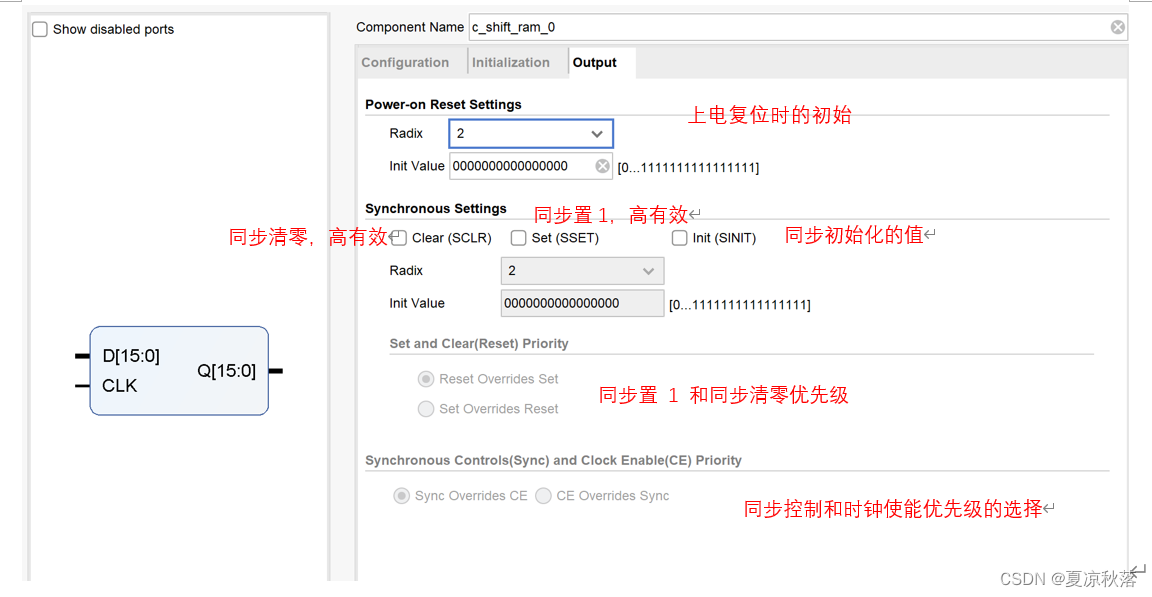

(3)输出选项卡的配置

3.4 代码的生成

例子1:固定长度

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/04/30 16:40:00

// Design Name:

// Module Name: shift_tb

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module shift_tb();

reg D;

reg CLK;

wire Q;

c_shift_ram_0 your_instance_name (

.D(D), // input wire [0 : 0] D

.CLK(CLK), // input wire CLK

.Q(Q) // output wire [0 : 0] Q

);

initial CLK =1;

always #5 CLK=~CLK;

initial begin

D=0;

#10;

D=1;

#10;

D=0;

end

endmodule

例子2:可变长度

module shift_lengthvariable_tb( );

reg D;

reg CLK;

reg [7:0] A;

wire Q;

c_shift_ram_1 your_instance_name (

.A(A),

.D(D), // input wire [0 : 0] D

.CLK(CLK), // input wire CLK

.Q(Q) // output wire [0 : 0] Q

);

initial CLK =1;

always #5 CLK=~CLK;

initial begin

D=0;

A=8'd10;

#10;

D=1;

#10;

D=0;

#30;

end

endmodule

例子2:多bit数

module shift_lengthvariable_tb( );

reg [7:0] D;

reg CLK;

reg [7:0] A;

wire[7:0] Q;

c_shift_ram_1 your_instance_name (

.A(A),

.D(D), // input wire [0 : 0] D

.CLK(CLK), // input wire CLK

.Q(Q) // output wire [0 : 0] Q

);

initial CLK =1;

always #5 CLK=~CLK;

initial begin

D=0;

A=8'd15;

#10;

D=8'b10101100;

#10;

D=0;

#30;

end

endmodule

3.5 仿真结果

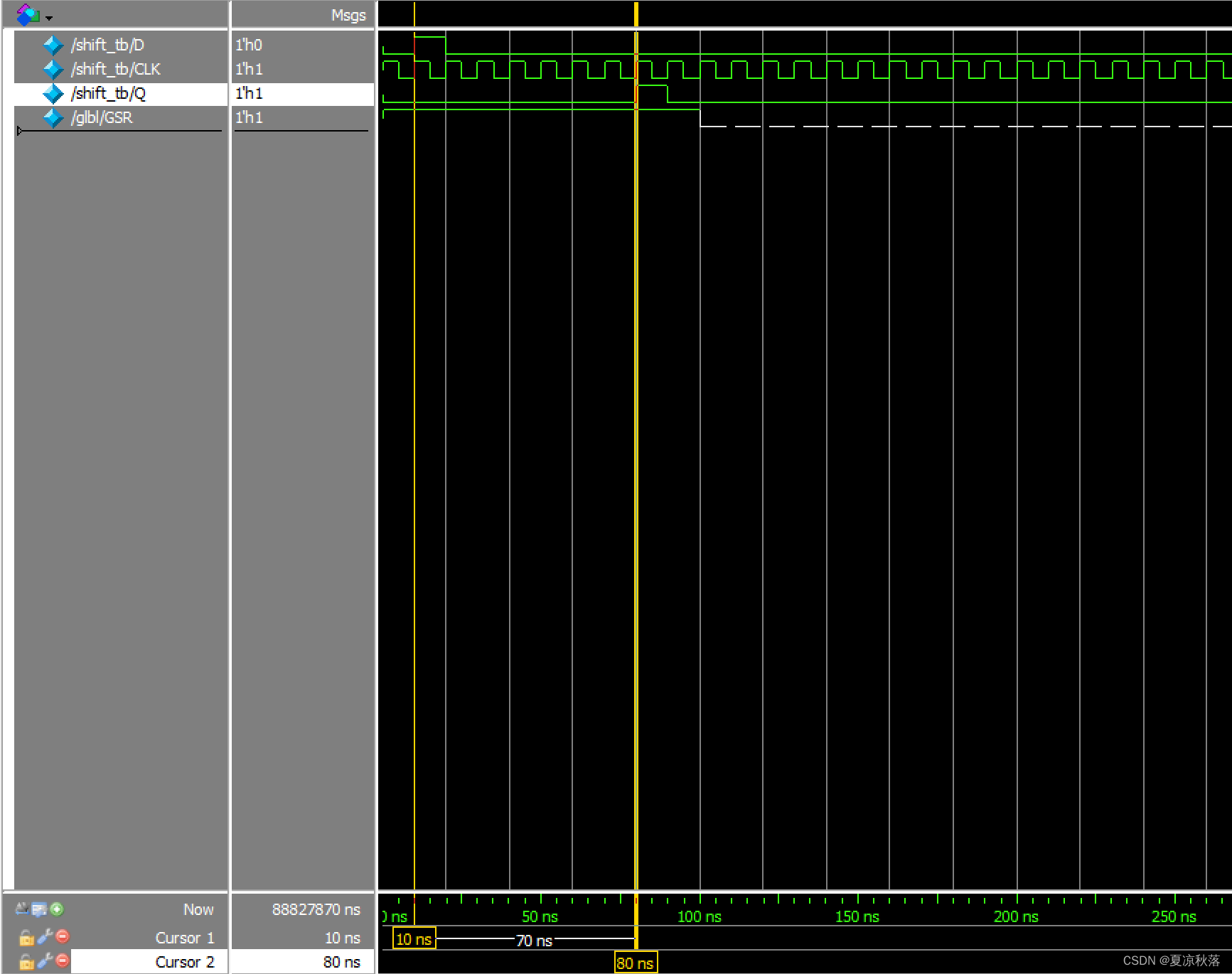

例子1

总结:ip核的深度设置为8,实际输出比输入延时了7个时钟周期

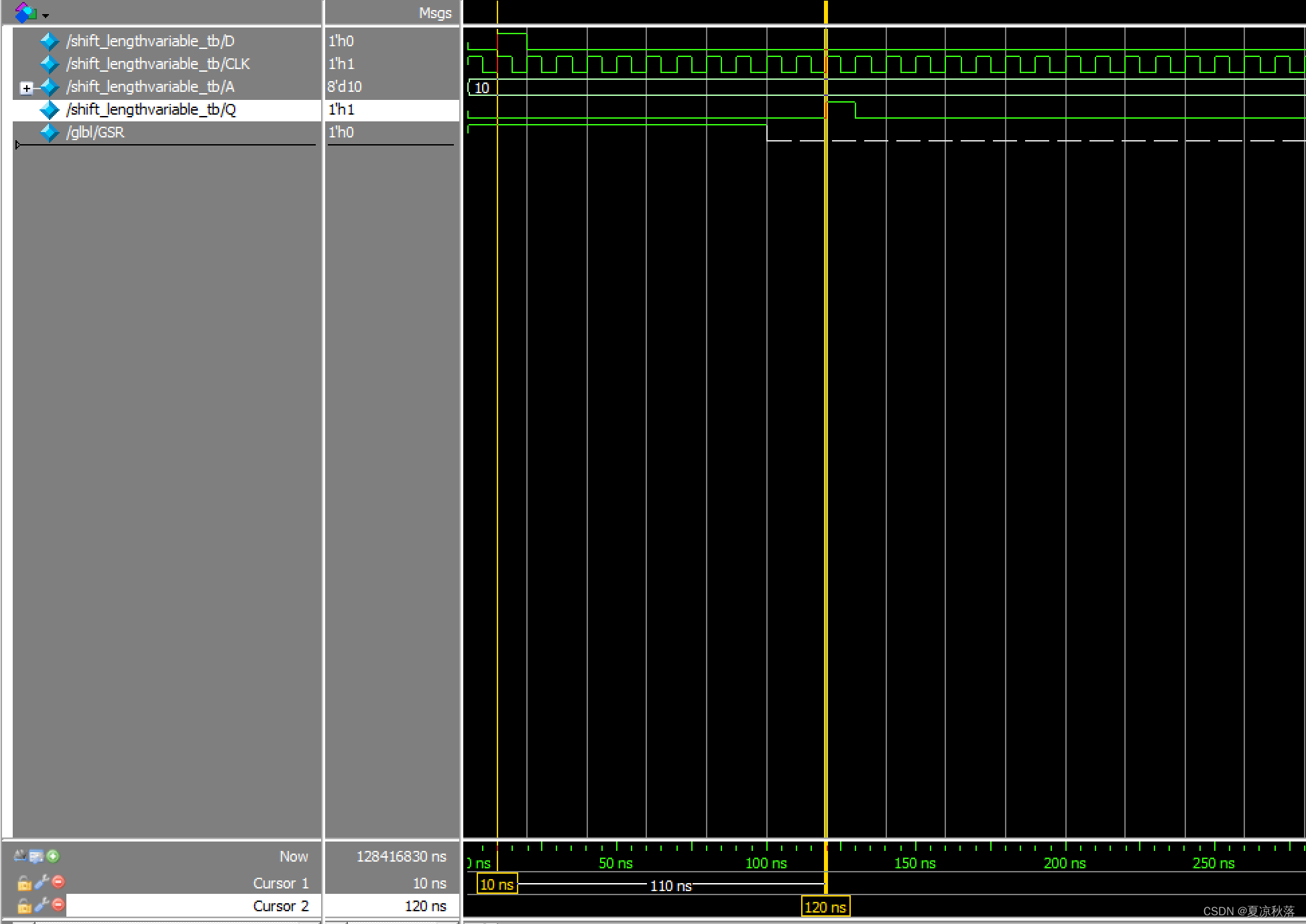

例子2:

总结:A=10,实际输出比输入延时了11个时钟周期,这是因为在ip核设置中如上图绿色框所示多了1个额外的时钟周期

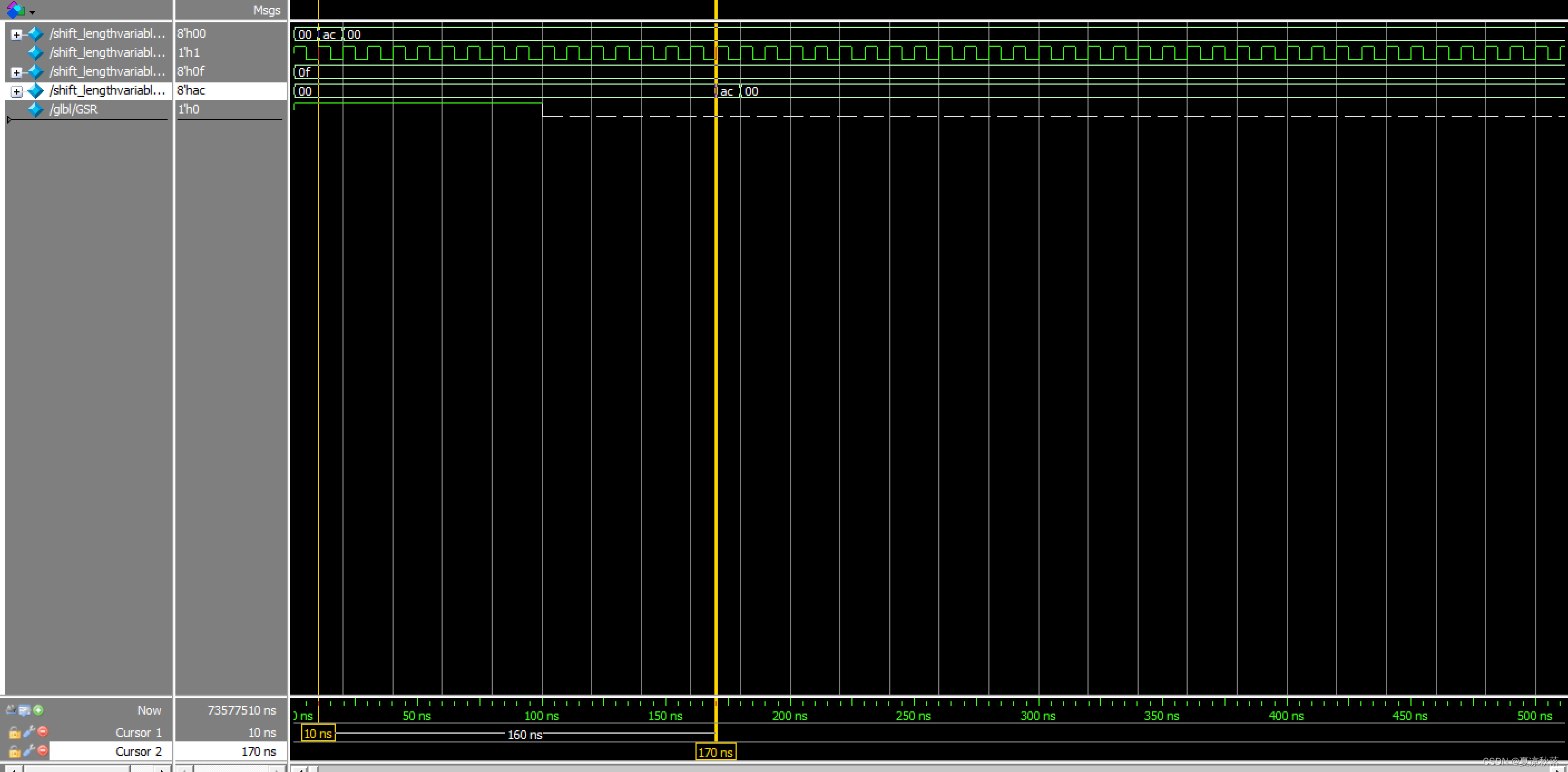

例子3:

总结:A=15,实际为16个时钟周期,解释同例子2

520

520

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?