Clocking

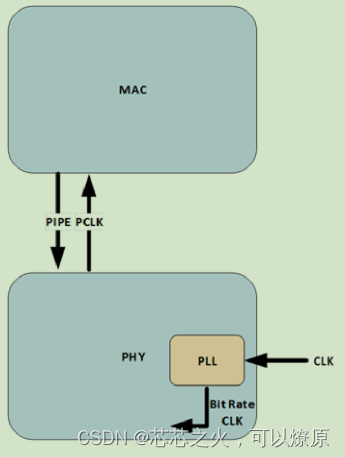

对于PIPE Interface,PIPE Interface中有三个和clock相关的信号,具体如下:

- 第一个时钟是ref_clk。PHY用这个时钟去产生内部逻辑发送数据和接收数据所需要的时钟。PIPE SPEC指出这个信号必须由厂商指定。ref_clk根据系统的需要可能会有扩展频谱调制(Spread Spectrum Modulation)。

- 第二个时钟是PCLK。PCLK对应有两种情况,一种是PCLK作为PHY的输出模式下的PCLK,还有一种是PCLK作为PHY的输入信号的PCLK。PCLK用于并行接口数据的同步,这个时钟的频率取决于Rate,PCLK Rate,以及PHY Mode和数据的位宽。PCLK也可能会有扩展频谱调制(Spread Spectrum Modulation)。

- 第三个时钟是MAX PCLK。这个时钟仅仅用于PCLK作为PHY的输入模式下并且要求PHY最大支持的速率为8GT/s及以上。MAX PCLK的数值应该设置为PHY最大支持的PCLK速率。

时钟结构

PCLK作为PHY的输出

PCLK作为PHY的输出这种时钟结构仅仅适用于原始的PIPE实现方案,不适用于PCIe Gen5的设计实现。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

996

996

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?