通过Report Utilization查看资源利用率报告时,会生成如下图所示的一个表格。在这个表格中Resource对应的列会有LUT和LUTRAM,那么两者到底有什么区别呢?是包含关系吗?不过,可以断定的是LUTRAM是指将LUT用做分布式RAM/ROM,换句话说是指SLICEM中的LUT被用做了存储单元,那么这里的存储单元是否包含移位寄存器(SRL)呢?

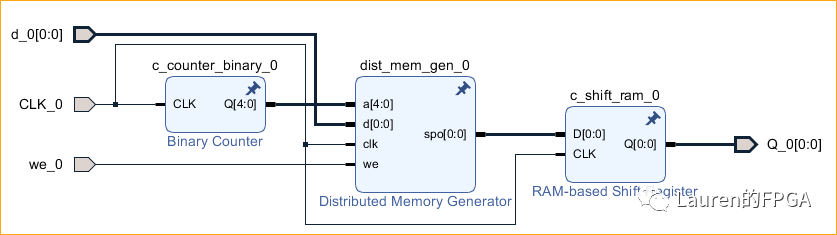

为了验证我们看如下一个设计。这个设计包含三个模块:5-bit计数器(会消耗1个LUT),32x1(深度为32,宽度为1)的分布式RAM(会消耗1个SLICEM中的LUT),深度为32的移位寄存器(会消耗1个SLICEM中的LUT)。

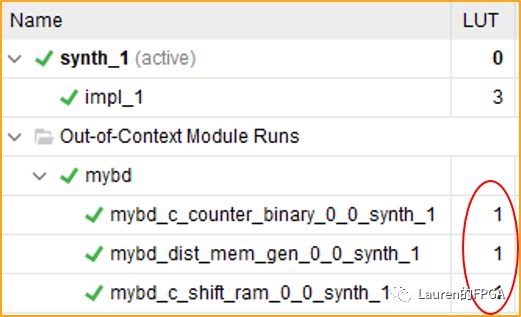

对每个模块采用OOC综合方式,可以验证上述对每个模块LUT利用率推断的正确性,如下图所示。

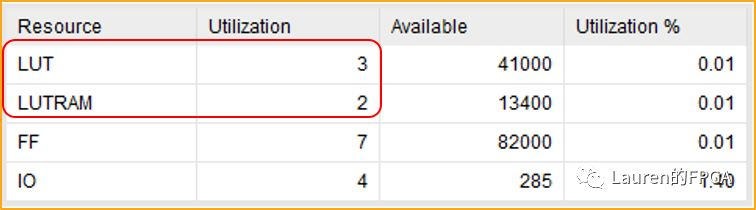

打开布线后的DCP,执行report_utilization命令,结果如下图所示。可以看到该设计共消耗了3个LUT,2个LUTRAM。

事实上,从Available对应列可以看到LUT对应的数据为41000,而该数据指的是FPGA中所有LUT的个数。

结论:

-资源利用率中的LUT是指设计中消耗的所有LUT,包括用做逻辑函数发生器的LUT(SLICEL中的LUT),也包括用做存储单元的LUT(SLICEM中的LUT)

-资源利用率报告中的LUTRAM是指设计中消耗的SLICEM中的LUT(用做分布式RAM/ROM或移位寄存器)

本文详细解析了FPGA设计中的LUT和LUTRAM的概念及其区别,通过实例验证了LUT作为逻辑函数发生器和存储单元的角色,以及LUTRAM特指用于分布式RAM/ROM或移位寄存器的SLICEM中的LUT。

本文详细解析了FPGA设计中的LUT和LUTRAM的概念及其区别,通过实例验证了LUT作为逻辑函数发生器和存储单元的角色,以及LUTRAM特指用于分布式RAM/ROM或移位寄存器的SLICEM中的LUT。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?