目录

1. 概述

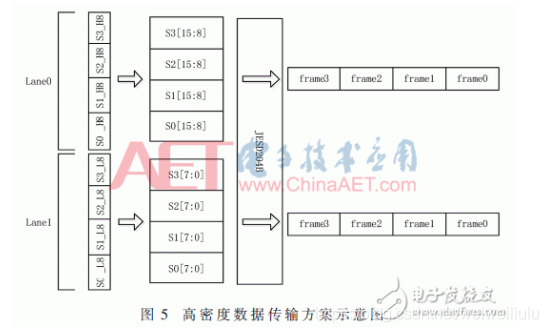

在JESD204接口出现以前,数模转换器的数字接口绝大多数是差分LVDS的接口,这就造成了布板的困难,当PCB的密度很大的时候就需要增加板层从而造成制版的成本。但是JESD204需要进行严格的同步和时延的测量,接口逻辑会比LVDS复杂。JESD204 有不同的版本,但是大部分用的subclass1。

2. 时钟

device clock 是器件工作的主时钟,一般在模数转换器里为采样时钟或者整数倍频的时钟,其协议本身的帧和多帧时钟也是基于device clock 。sysref是用于指示不同转换器或者逻辑的device clock的沿,或者不同器件间的deterministic latency 的参考。

device clock 和sysref必须满足的时序关系。sysref 的第一个上升沿要非常容易的能被device clock捕捉到。通常会因为PCB 的线长以及时钟器件不同,通道输出时的skew会带来一定的误差,device clock的上升沿不一定正好在sysref 的脉冲正中间,工程上只要在一定范围内就能保证JESD204收发正常工作。

sysref 在我以前的设计中,用的是,同步上以后,就没有sysref信号,也就IP 配置的时候sysref off。

3. 同步协议

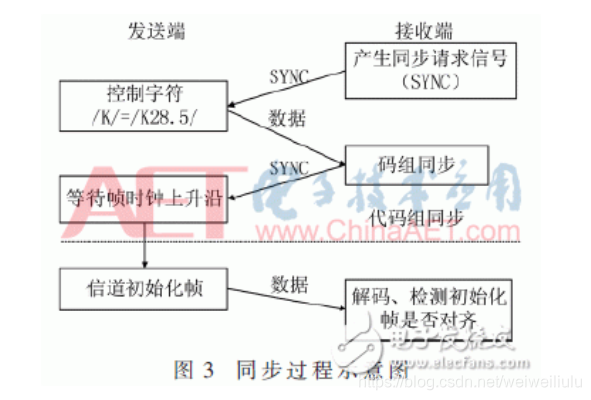

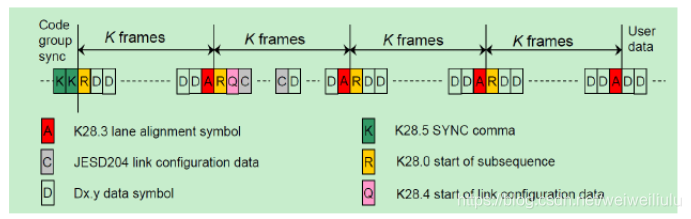

CGS:代码组同步(code group sync)当发送端检测到syncb信号为低电平时启动发送8B10B 中的K28.5码,本段数据段不进行扰码和字节替换操作,接收端检测到最少4个BC字节后可释放SYNCb信号;

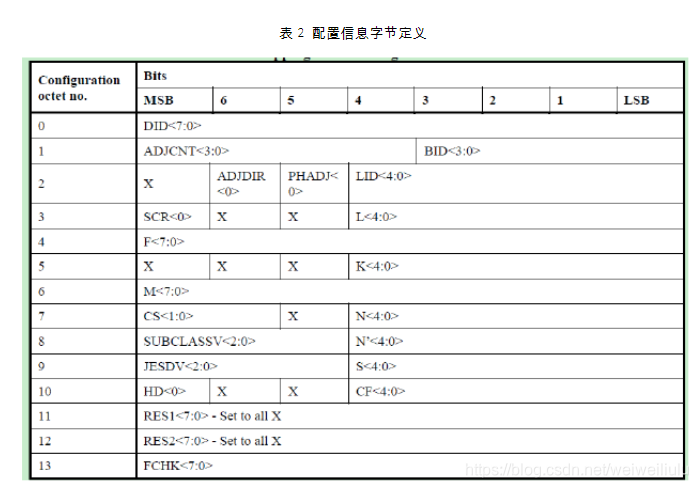

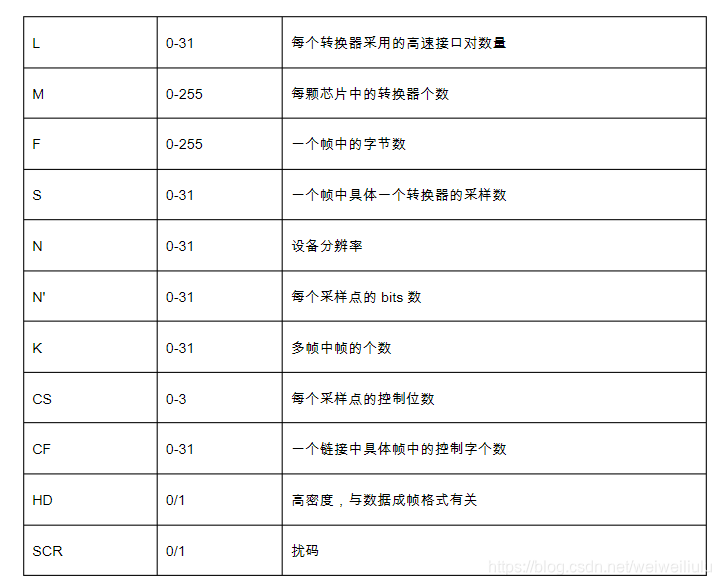

ILA:初始化多帧序列 (initial lane alignment)该阶段发送连续4个初始化多帧(多帧是由K个帧组成,字节数为K*F),此样本数据段不进行扰码和字节替换。初始化多帧以8B10B中的K28.0开始以K28.3结束,其中第二个多帧的第二字节K28.4关键字用来指示当前多帧在紧跟着K28.4的后续14个字节是参数配置信息。表2是具体的配置参数定义。

DATA:数据传输阶段 (data transmission ),该阶段进行数据传输,规范中要求该阶段的数据需要进行字节替换(扰码和不扰码的字节替换规则不同)。

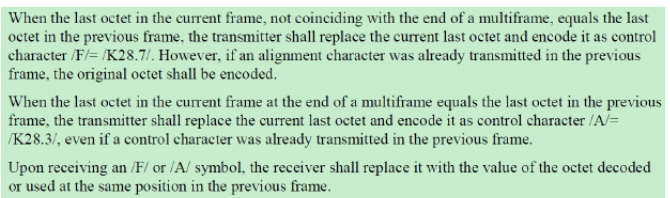

字节替换规则:

1、没有使能扰码情况下的字节替换规则

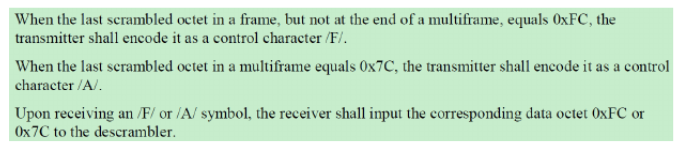

2、 使能扰码情况下的字节替换规则

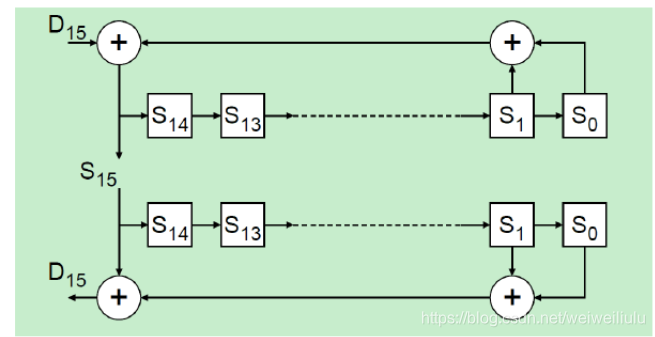

JESD204B规定的扰码、解扰码生成多项式

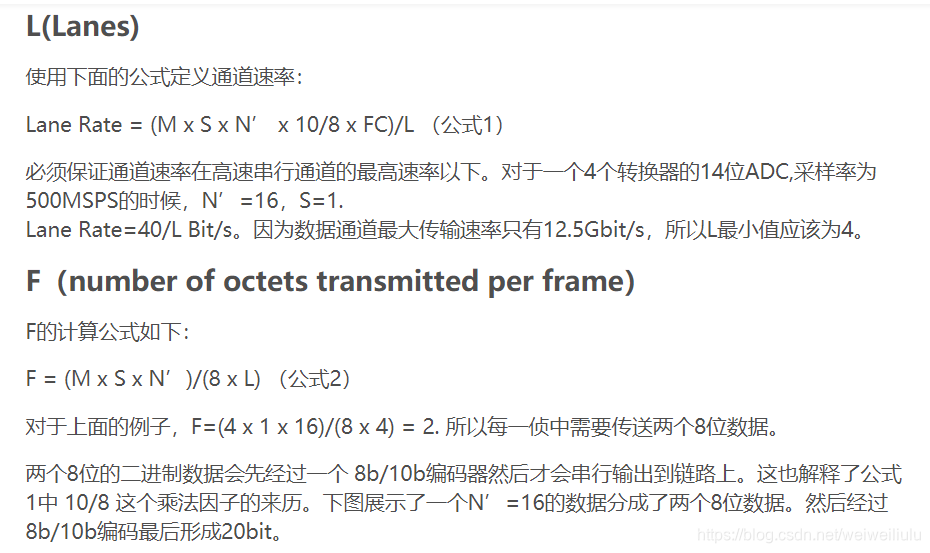

4. 参数理解

具体实现可以参考 http://xilinx.eetrend.com/blog/2020/100049267.html 小青菜哥哥的博文

1036

1036

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?