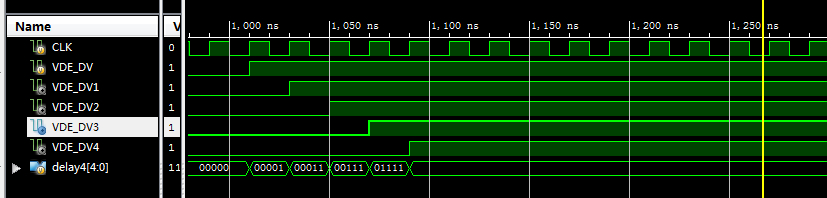

需要做的事情:使能信号TxE_to_ETH由时钟122.88M时钟输出;另一使能信号VDE_DV由25M时钟输出,计算两个使能信号之间的时间间隔,即两个信号上升沿之间的时钟计数。

由于两个信号属于不同的时钟域,因此要先进行跨时钟域处理,这里对VDE_DV进行处理:在122.88M时钟下将VDE_DV进行多次(至少两次)延时,这里不再使用这样的方法:

reg VDE_DV_1 = 0;

reg VDE_DV_2 = 0;

reg VDE_DV_3 = 0;

always @ (posedge clk_122p88)

begin

VDE_DV_1 <=VDE_DV;

VDE_DV_2 <=VDE_DV_1;

VDE_DV_3 <= VDE_DV_2;

end

而是使用这样的方法:

module syn(

input CLK,

input VDE_DV,

output VDE_DV1,

output VDE_DV2,

output VDE_DV3,

output VDE_DV4

);

reg [4:0] delay4 = 0;

always @ (posedge CLK)

begin

delay4 <= {delay4[3:0],VDE_DV};

end

assign VDE_DV1 = delay4[1];

assign VDE_DV2 = delay4[2];

assign VDE_DV3 = delay4[3];

assign VDE_DV4 = delay4[4];

endmodule

3210

3210

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?