一种对输入数据边沿进行检测的设计。

目录

一、边沿检测

边沿检测在芯片设计中会经常用到。当某一信号发生变化时,我们常常需要检测到这种变化,以此作为其他事件的触发条件。

检测数据,输出上升沿、下降沿和总体的数据边沿。

上代码:

module check(

input clk,

input rst_n,

input data,

output pos_edge,

output neg_edge,

output data_edge

);

reg [1:0] data_r;

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

data_r <= 2'b0;

end

else begin

data_r <= {data_r[0],data};

end

end

assign pos_edge = ~data_r[1] & data_r[0];

assign neg_edge = data_r[1] & ~data_r[0];

assign data_edge = pos_edge | neg_edge;

endmodule对输入数据进行打拍处理。

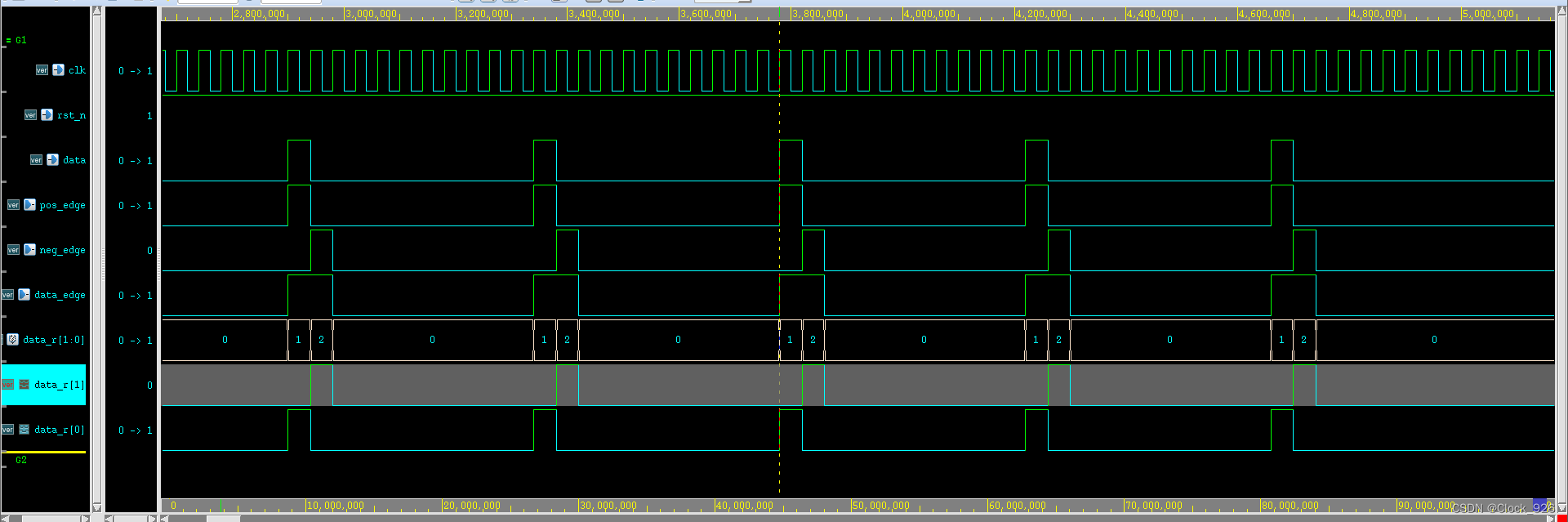

测试波形:

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?