目录

题目

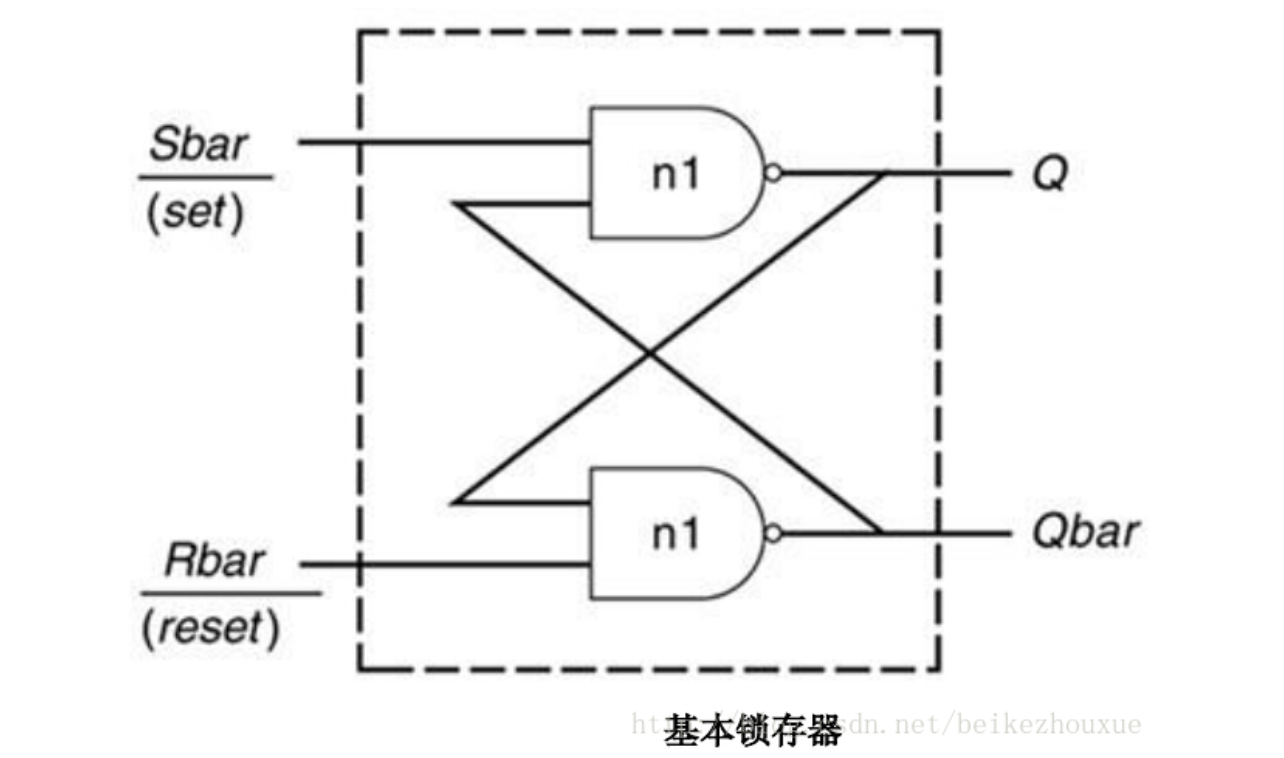

门电路搭建锁存器

核心思路

锁存器(latch):是电平触发的存储单元,数据存储的动作(状态转换)取决于输入时钟(或者使能)信号的电平值,尽当锁存器处于使能状态时,输出才会随着数据输入发生变化。

分为普通锁存器和门控锁存器,普通锁存器无控制信号,输出状态始终直接由输入决定。在实际的数字系统中,为了协调各部分的工作,往往需要有一个特定的控制信号去控制锁存器状态转换的时间,在控制信号无效时,输出保持不变,不随输入变换;当控制信号有效时,输出由输入决定,跟随输入变化。

答案

FPGA全貌

第1节 什么是 FPGA

FPGA 的全称为 Field-Programmable Gate Array,即现场可编程门阵列。 FPGA 是在 PAL、 GAL、 CPLD 等可编程器件的基础上进一步发展的产物, 是作为专用集成电路( ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。 简而言之, FPGA 就是一个可以通过编程来改变内部结构的芯片。FPGA 功能实现:需要通过编程即设计硬件描述语言,经过 EDA 工具编译、综合、布局布线成后转换为可烧录的文件,

最终加载到 FPGA 器件中去,改变 FPGA 内部的连线,最终完成所实现的功能。FPGA 性能对比:FPGA 相比于单片机、 CPU 等集成电路芯片拥有效率更高、功耗更低的特点,但是易于开发程度远远不如单片机、 CPU; 在数字芯片设计领域, FPGA 虽然相比 ASIC 具有更短的开发周期与开发难度, 但是其存在着成本过高、性能较差并且在资源的利用率上远不及 ASIC 等问题,不能真正的替代 ASIC。

第2节 FPGA 的基本结构

FPGA 可编程的特性决定了其实现数字逻辑的结构不能像专用 ASIC 那样通过固定的逻辑门电路来完成,而只能采用一种可以重复配置的结构来实现, 而查找表(LUT)可以很好地满足这一要求,目前主流的 FPGA 芯片仍是基于 SRAM 工艺的查找表结构。FPGA 芯片参数指标:包含可编程逻辑模块的数量、固定功能逻辑模块(如乘法器)的数目及存储器资源(如嵌入式 RAM)的大小。

在最底层的可配置逻辑模块(如片上的逻辑单元) 上,存在着基本的两种部件:触发器和查找表( LUT) , 而触发器和查找表的组合方式不同,是各个 FPGA 家族之间区别的重要依据, 并且查找表本身的结构也可能各不相同( 有 4 输入或 6 输入或其他)。

查找表( Look-Up-Table)简称为 LUT, 其本质上就是一个 RAM。目前 FPGA 内部中多使用 4输入的 LUT,每一个 LUT 可以看成一个有 4 位地址线的 RAM。

当用户在 EDA 工具上通过原理图或 硬件描述语言设计了一个逻辑电路以后, FPGA 开发软件会自动计算逻辑电路的所有可能结果,并把真值表(即结果)事先写入 RAM 中。 这样,每输入一个信号进行逻辑运算就等于输入一个地址进行查找表操作, 通过地址找到对应的 RAM 中的结果, 最后将其输出。以实现数字逻辑 Y=A&B&C 的功能为例。如果是在专用 ASIC 中,为了实现该逻辑,逻辑门都已经事先确定好, Y 的输出值为两个逻辑与运算后的结果,其基本的实现结构如下图所示:

对Y=A&B&C 的 利用FPGA 实现基本结构 :

第3节 更为复杂的 FPGA 架构

随着技术的发展和工艺节点的进步, FPGA 的容量和性能在不断提高的同时, 其功耗却不断的优化减少。 2006 年以前四输入查找表一直被广泛使用, 在一些高端器件可能会用上六输入、八输入或更多输入端口的查找表。 而一个多输入的查找表又可以分解成较小输入的查找表, 即能够分裂成许多更小的功能。 例如一个八输入的查找表可以分解成两个四输入的查找表或分解成一个三输入加一个五输入的查找表。在实际的高端器件中,这种可编程构造可以描述相当于百万级(有时甚至千万级)的原始逻辑门。在 FPGA 内部,利用 FPGA 的可编程性在芯片内部构造实现了一个计数器逻辑,有着“软内核”与“硬内核”之分。

软内核(软功能):在构造计数器逻辑过程中使用到的功能便可以被称为软功能。

硬内核(硬功能):功能若是直接利用芯片实现的,则是利用了芯片内部的硬功能。

软内核与硬内核之间优势互补,软内核的优势在于可以在利用芯片资源的基础上利用编程设计让其完成需要实现的任何功能(注意是数字功能,不包括模拟功能)。 而**硬内核由于是实现固定功能的器件,因此其优势在于资源利用率高且功耗较低, 占用硅片的面积也较小, 并具有较高的性能。最重要的区别**在于:与软内核相比硬内核可用于实现模拟功能, 例如锁相环的倍频功能,这个功能需要在模拟电路下实现,所以这一部分是在 FPGA 内部用硬件来实现的 。

4万+

4万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?